General Xilinx information

IBERT for 7 Series GTX Transceivers

https://www.xilinx.com/products/intellectual-property/ibert_7series_gtx.html

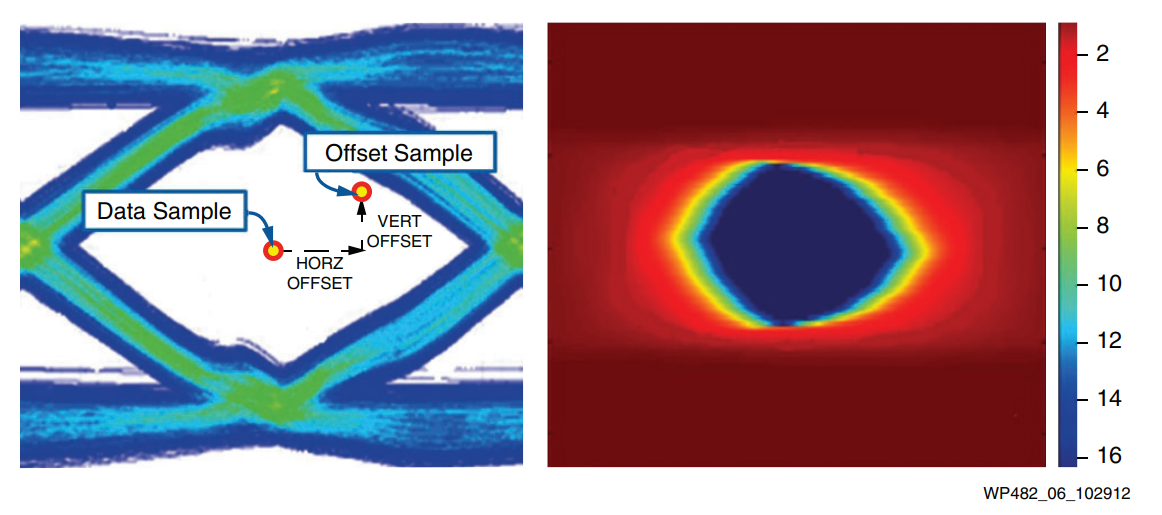

Eye Scan Theory

page 215 of https://www.xilinx.com/support/documentation/user_guides/ug476_7Series_Transceivers.pdf

IBERT for UltraScale/UltraScale+ GTH Transceivers

https://www.xilinx.com/products/intellectual-property/ibert_ultrascale_gth.html

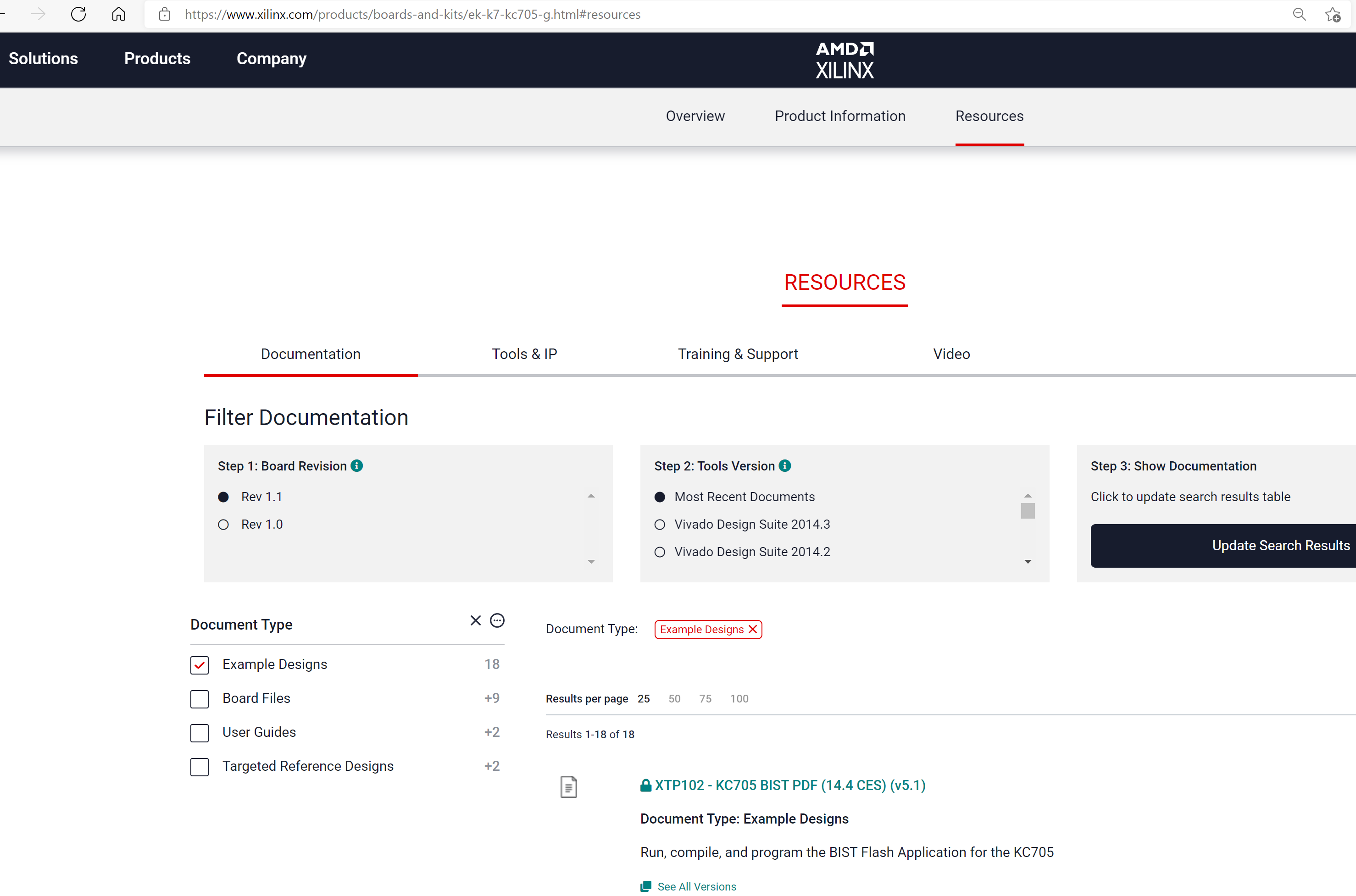

Xilinx Kintex-7 FPGA KC705 Evaluation Kit

https://www.xilinx.com/products/boards-and-kits/ek-k7-kc705-g.html

many useful information and example from the resources center:

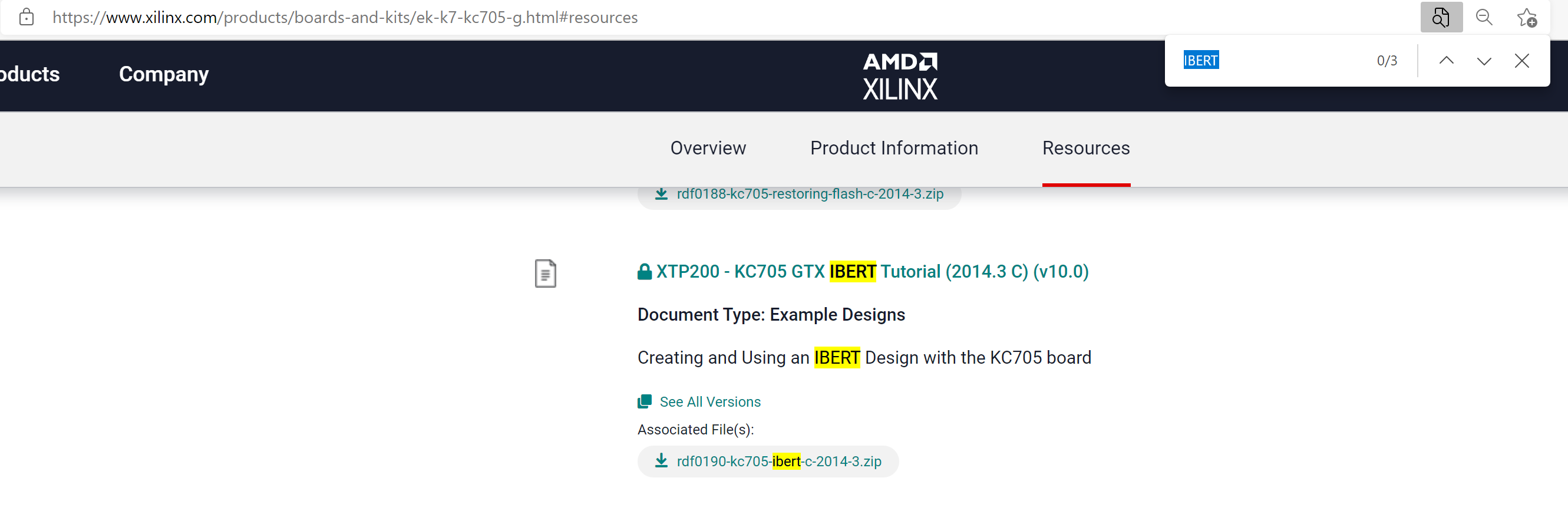

the KC705 GTX IBERT Tutorials: (Needs a Xilinx account to download the slides, firmware, and source code)

KC705 schematics: kc705_Schematic_xtp132_rev1_1.pdf

KC705 IBERT tutorial: xtp200-kc705-ibert-c-2014-3.pdf

firmware and source code: rdf0190-kc705-ibert-c-2014-3.zip

Xilinx Kintex UltraScale FPGA KCU105 Evaluation Kit

https://www.xilinx.com/products/boards-and-kits/kcu105.html

many useful information and example from the resources center:

KCU105 schematics: kcu105-schematic-xtp392.zip

KCU105 IBERT tutorial: xtp346-kcu105-gth-ibert-c-2017-3.pdf

firmware and source code: rdf0312-kcu105-gth-ibert-c-2017-3.zip (this file is too big to directly uploaded to confluence, so, it points to a google driver link)

White paper for the Xilinx FPGA IBERT and transceivers

wp428-7Series-Serial-Link-Signal-Analysis.pdf

Compiling the IBERT FPGA for KC705

Xilinx official tutorial for IBERT firmware

Step-by-step Instruction

you can use the ATLAS team rddev111 server. Please contact Su Dong and Matthias Wittgen for a user account.

- ssh login to the rddev111 server

- source the Xilinx vivado environment: $ source /data/Xilinx/Vivado/2021.2/settings64.sh

- add a license for vivado: $ export LM_LICENSE_FILE=2100@rdlic1:2100@rdlic2:2100@rdlic3

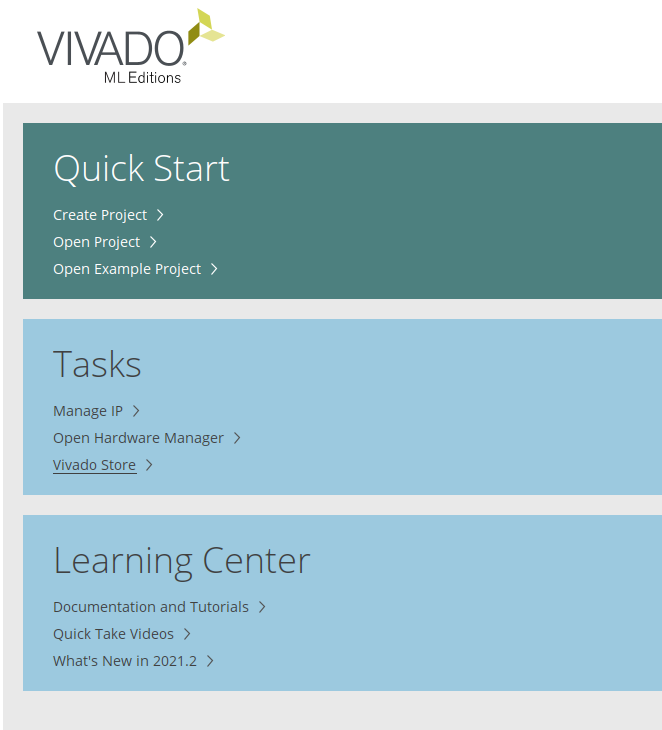

- start the vivado software: $ vivado

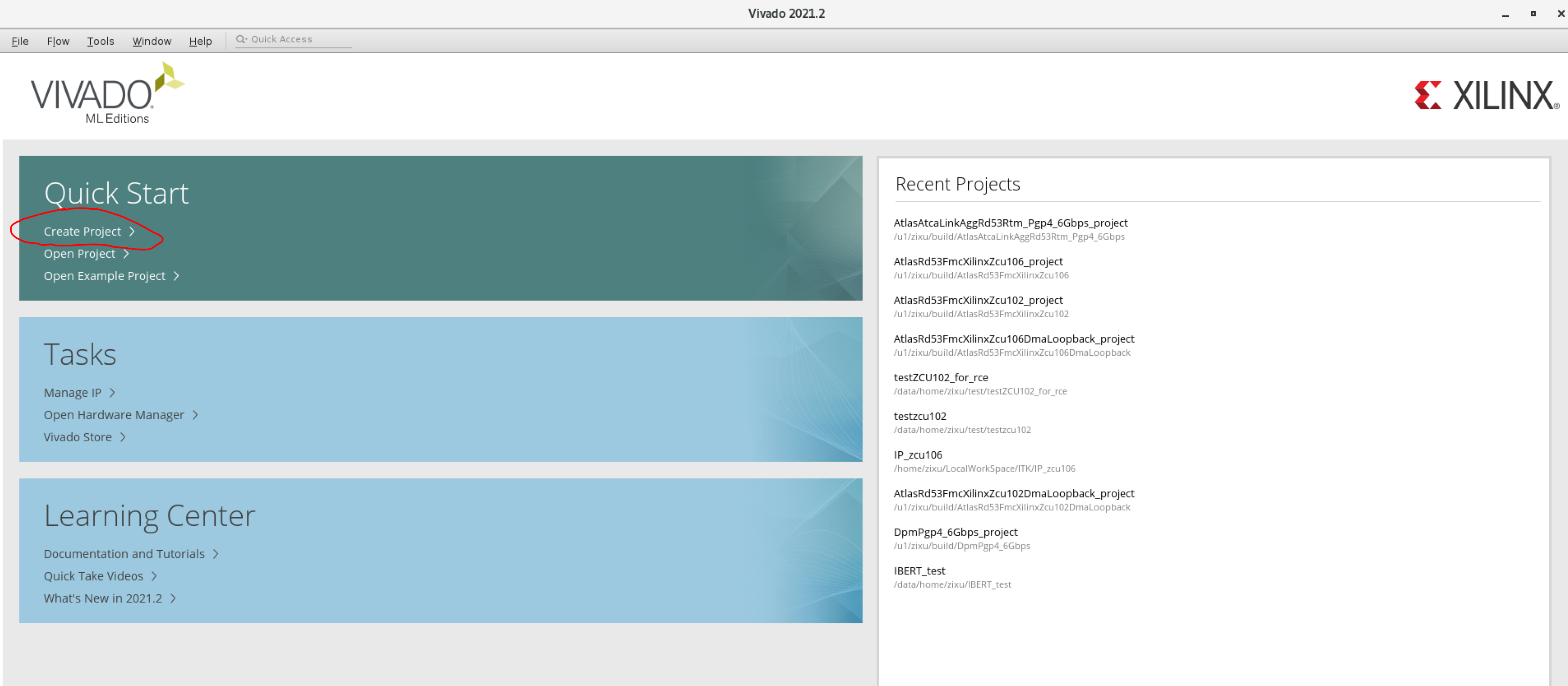

- create a project:

- project name:

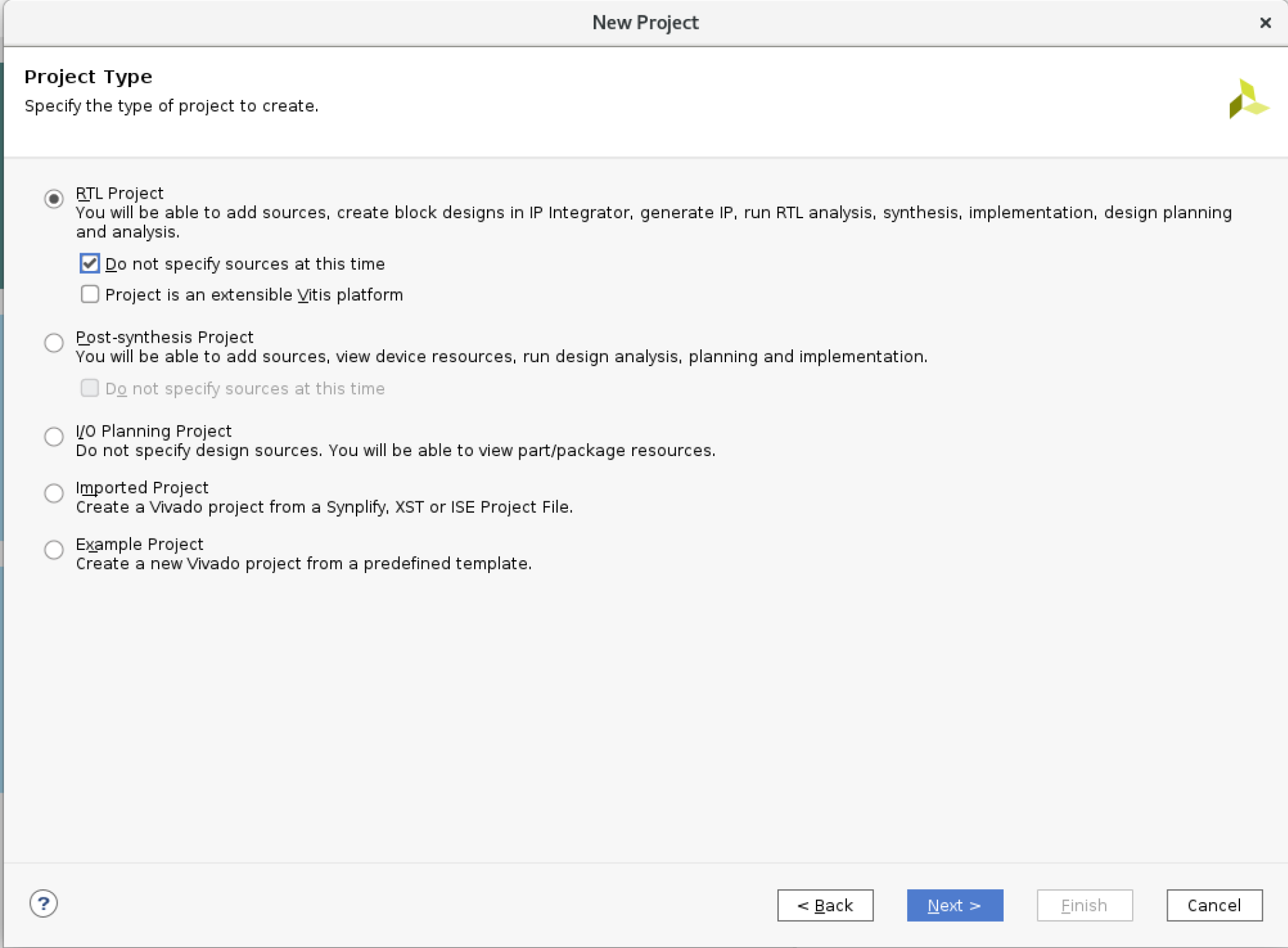

- project type:

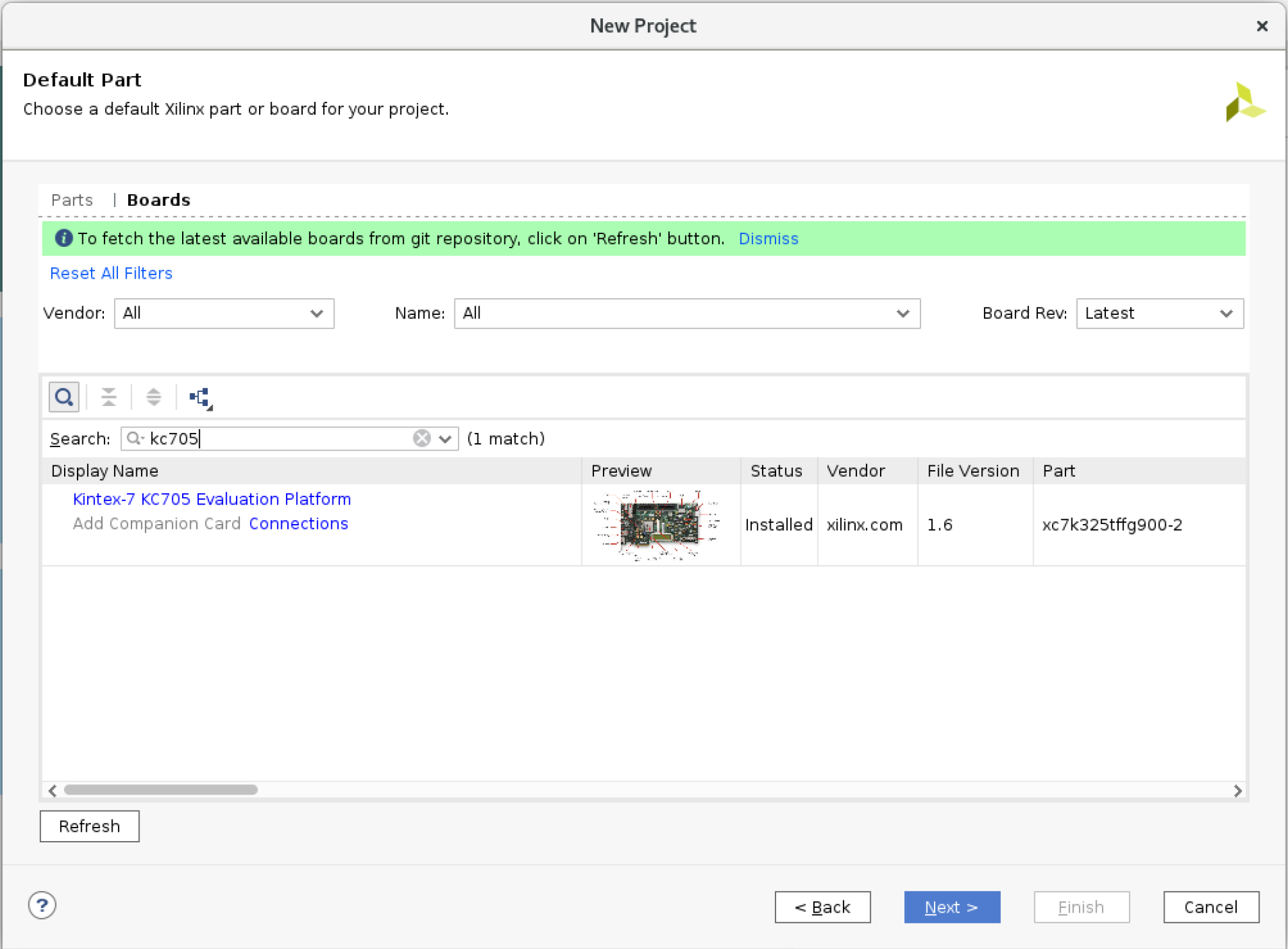

- choose hardware platform:

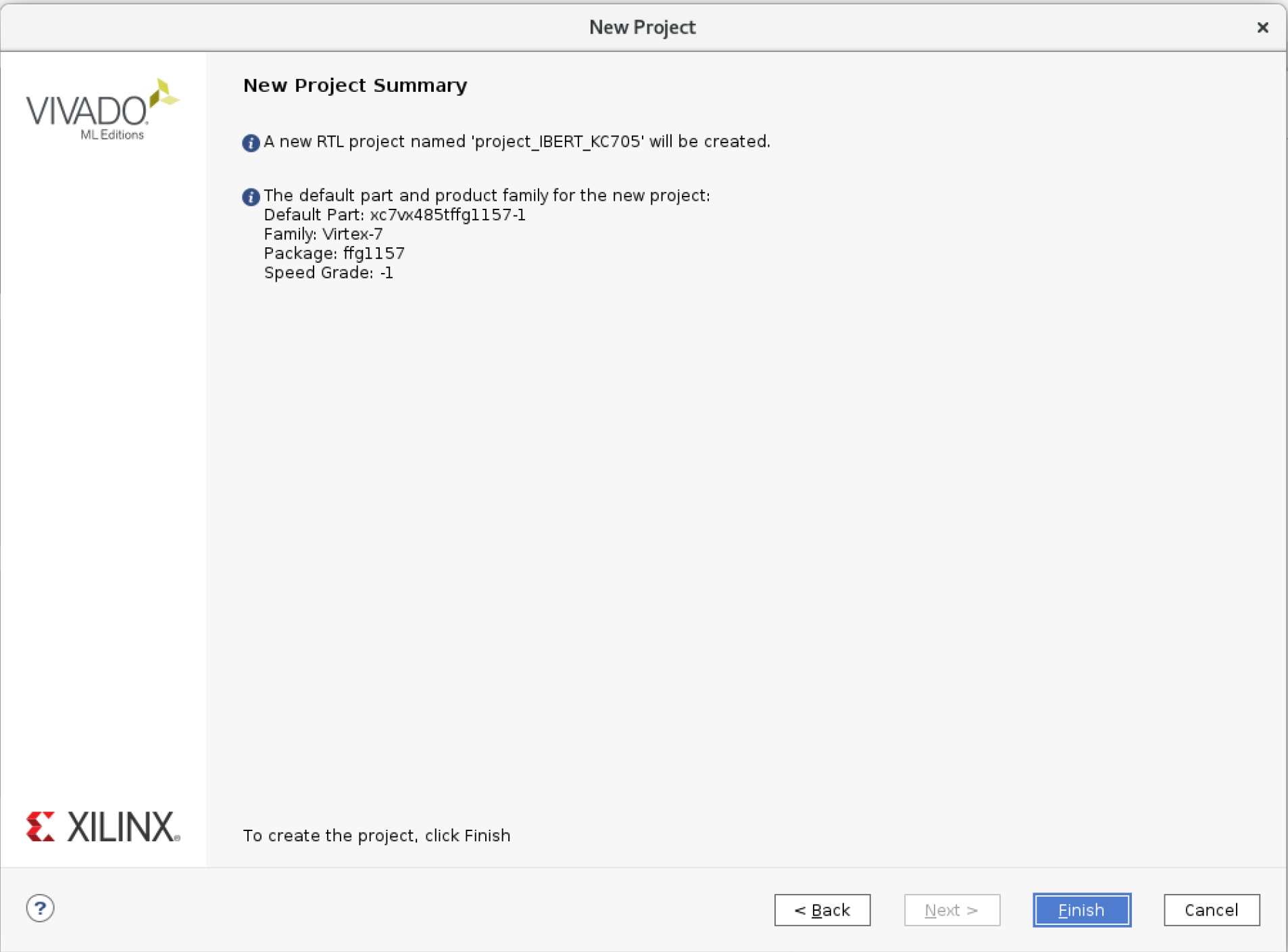

finish:

- click "IP catalog", and search "IBERT"

- double click "IBERT 7 Series GTX" to customize this IP

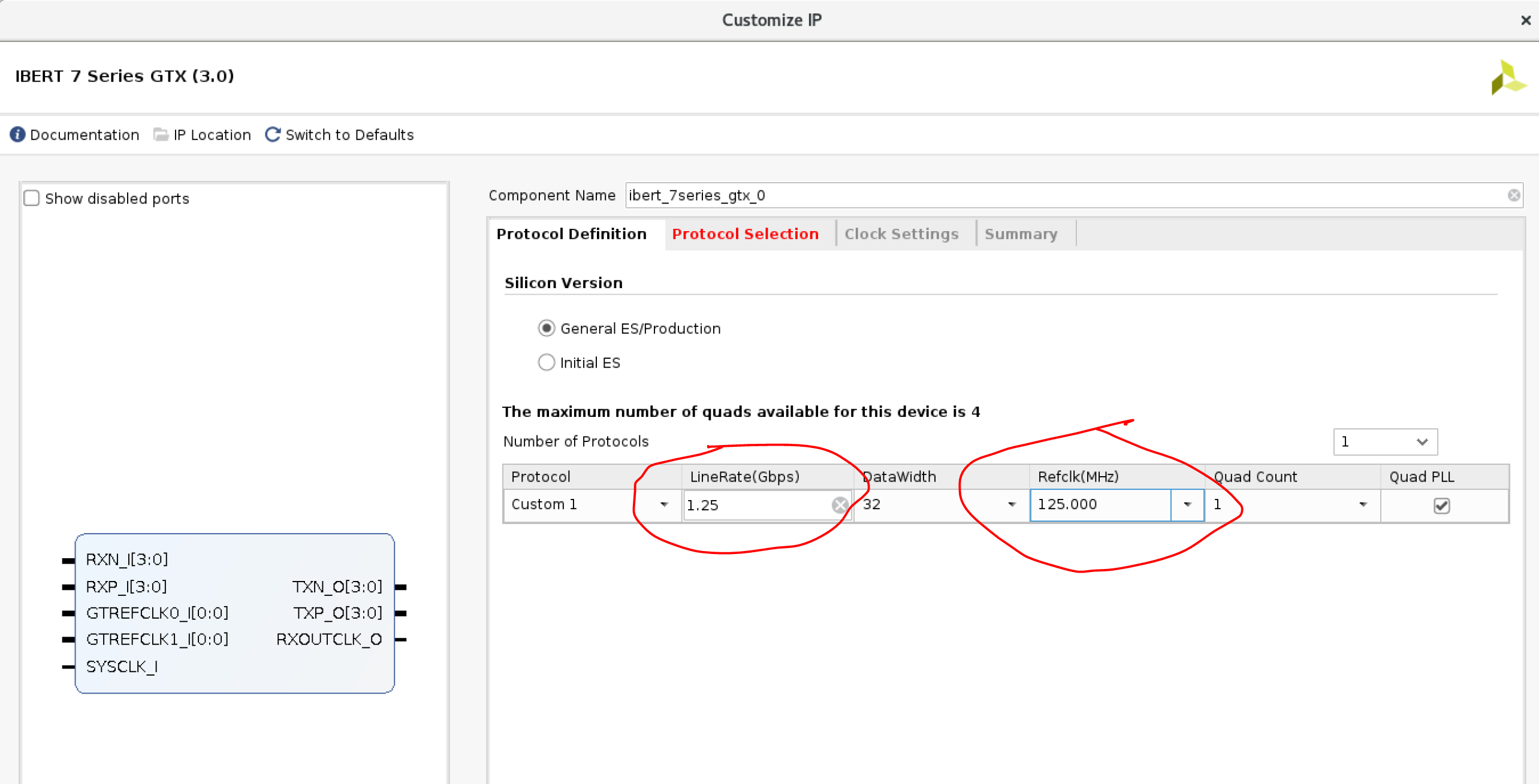

- lineRate to 1.25Gbps, and RefClk 125.0MHz :

- the RefClk is fixed to 125MHz, so, the lineRate can only be 1.25Gbps, but not 1.28Gbps. (LineRate could also be 2.0Gbps when refClk=125MHz)

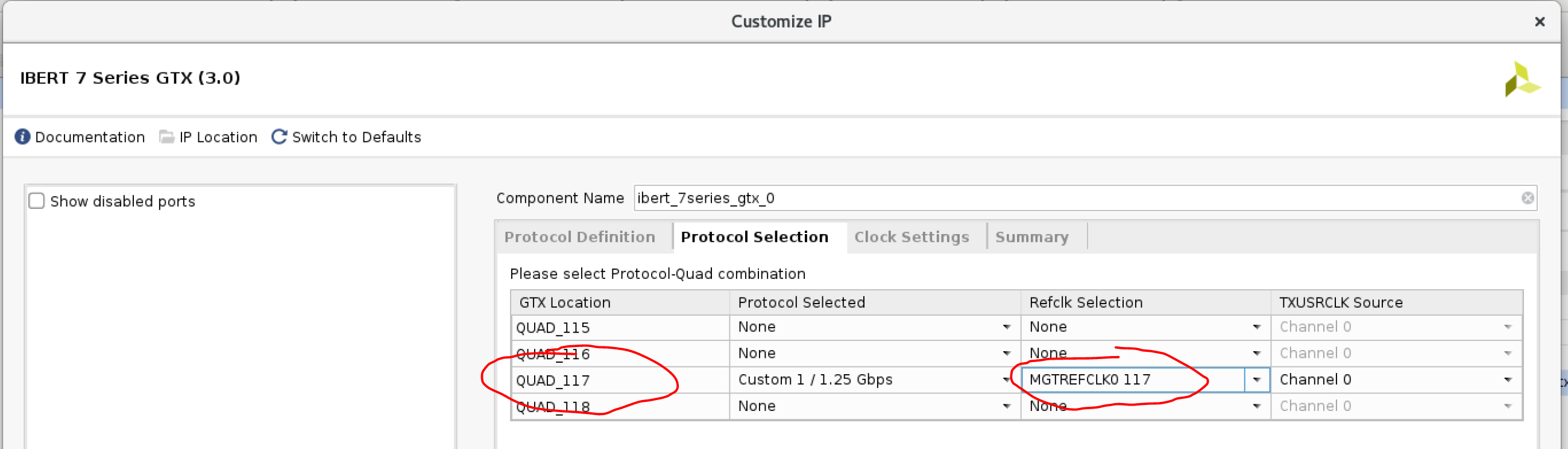

- Protocol selection:

- Quad_117 support the SMA and SPF+ interface

- System Clock setting:

- Customize IP Done:

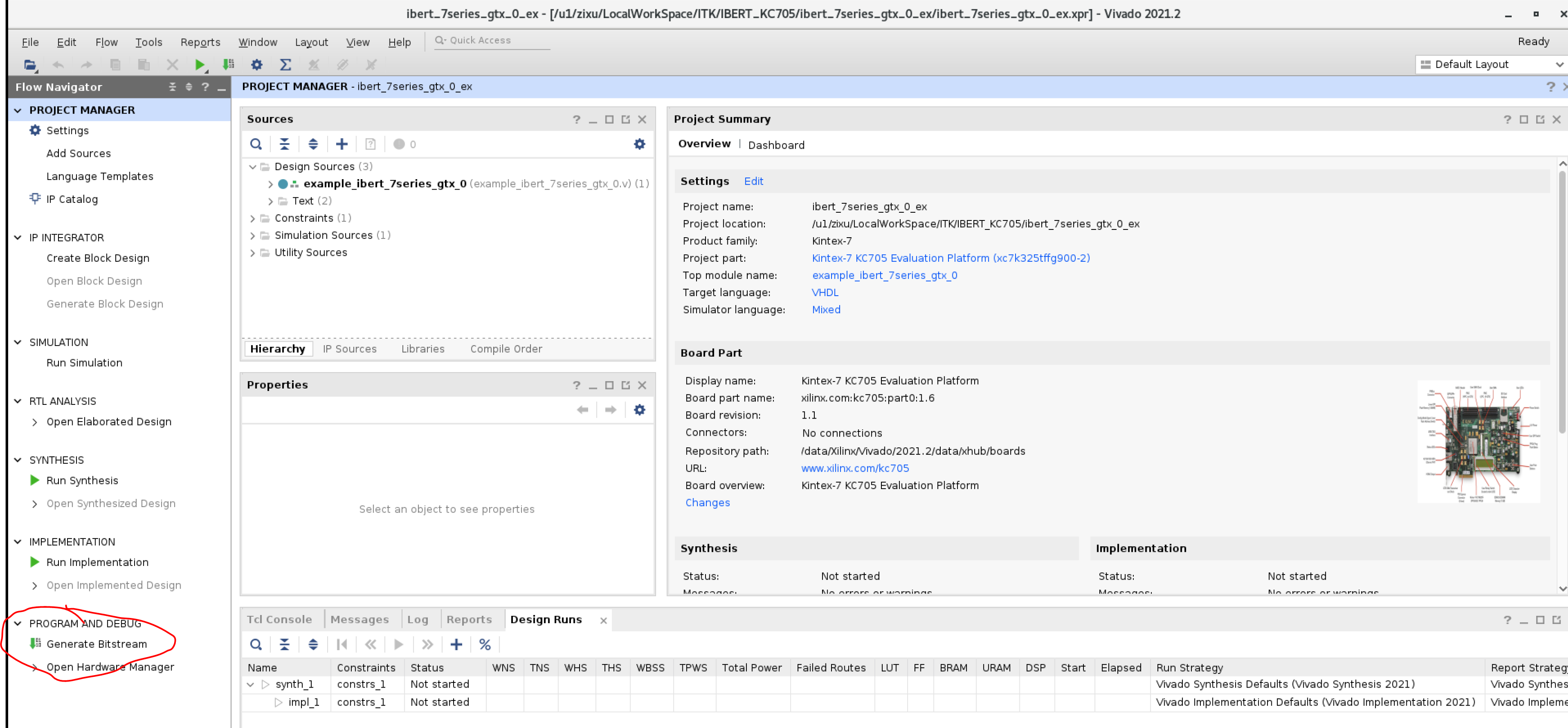

- right-click the IP instance "ibert_7series_gtx_0", and Open IP Example Design:

- open IP example design:

- Generate Bitstream on the new vivado GUI:

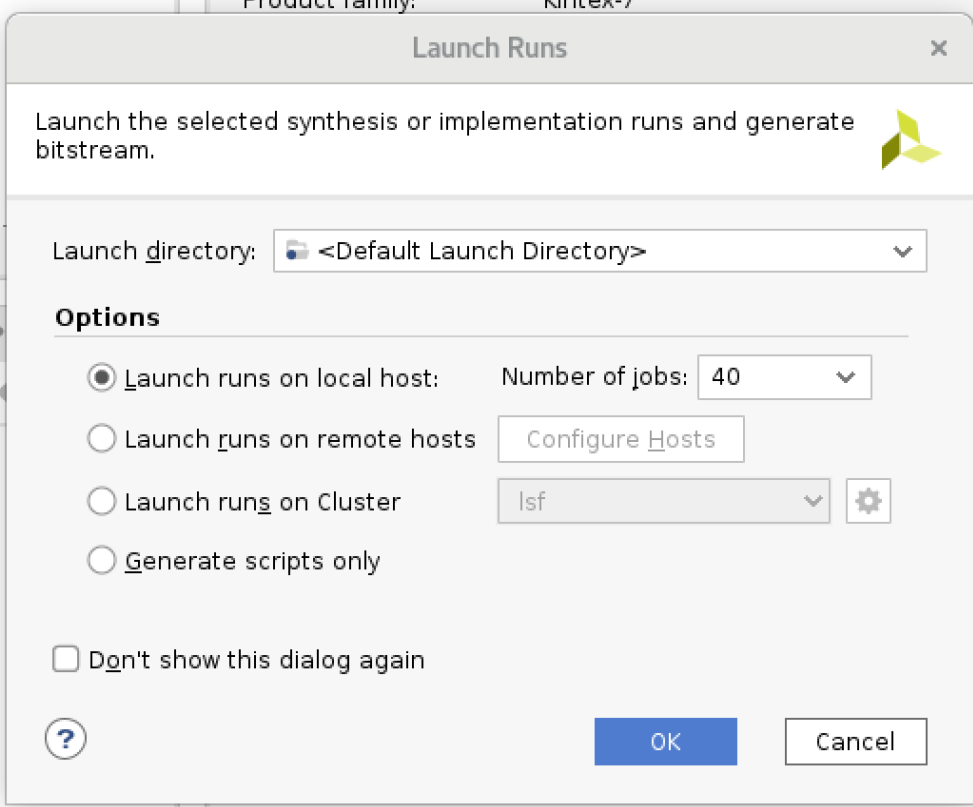

- Launch Runs, and click ok:

- about 6 mins, done:

- if your FPGA board is connected to this computer, you can choose "Open Hardware Manager" to continue.

- If you want to use another PC/laptop to control the FPGA board, you need to copy the firmware from: <your project location>/ibert_7series_gtx_0_ex/ibert_7series_gtx_0_ex.runs/impl_1/example_ibert_7series_gtx_0.bit

Compiling the IBERT FPGA for KCU105

Xilinx official tutorial for IBERT firmware

Simplified Step-by-step Instruction

*it is almost the same as KC705 for firmware compiling. So, I don't repeat them, but just show the most import steps below:

- choose "IBERT Ultrascale GTH":

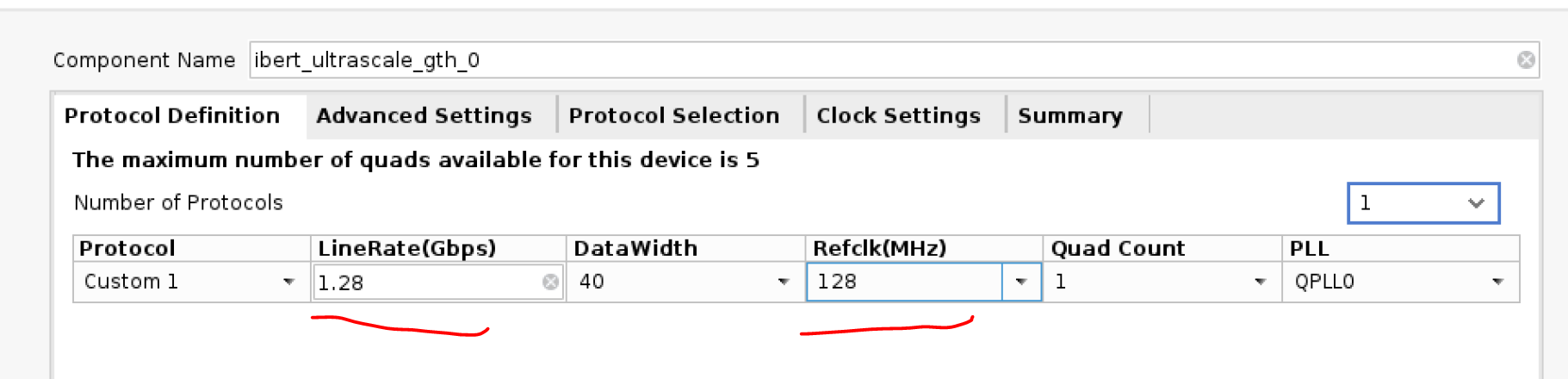

- set the LineRate and RefClk

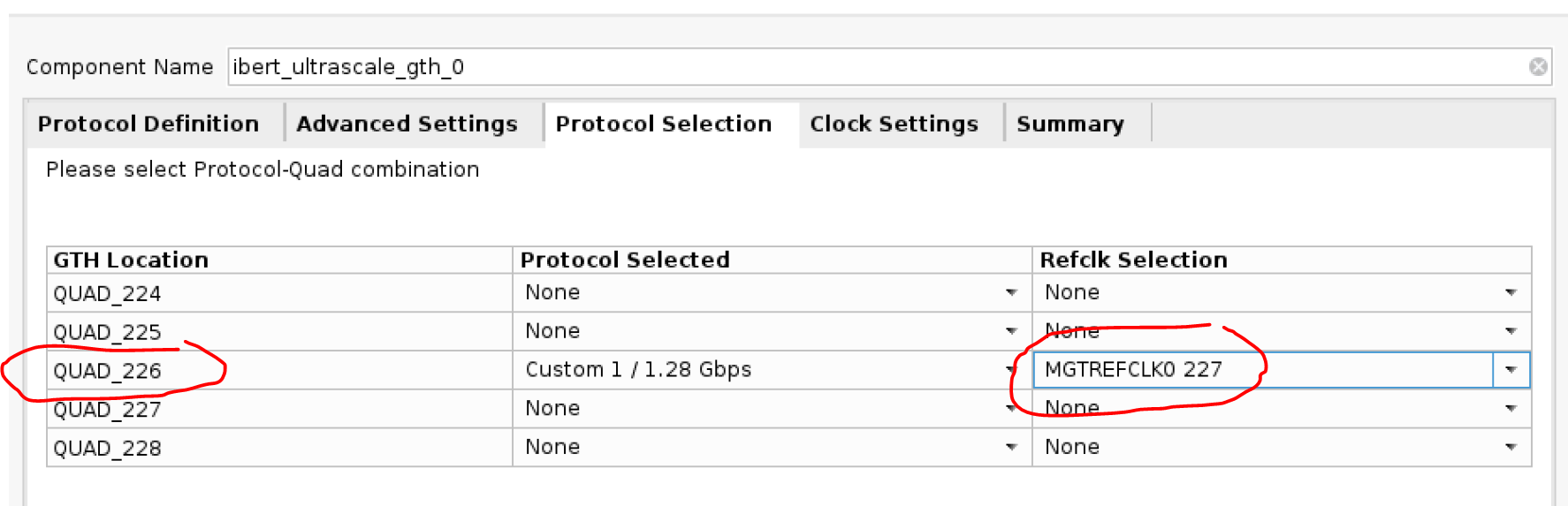

- Protocol selection:

- SMA interface connected to the Quad_226

- MGTREFCLK0 227 is connected to a Silicon Labs Si570 programmable low-jitter clock. the default output frequency is 156.25MHz. We will change it to 128MHz when powering the FPGA board up.

- system clock settings:

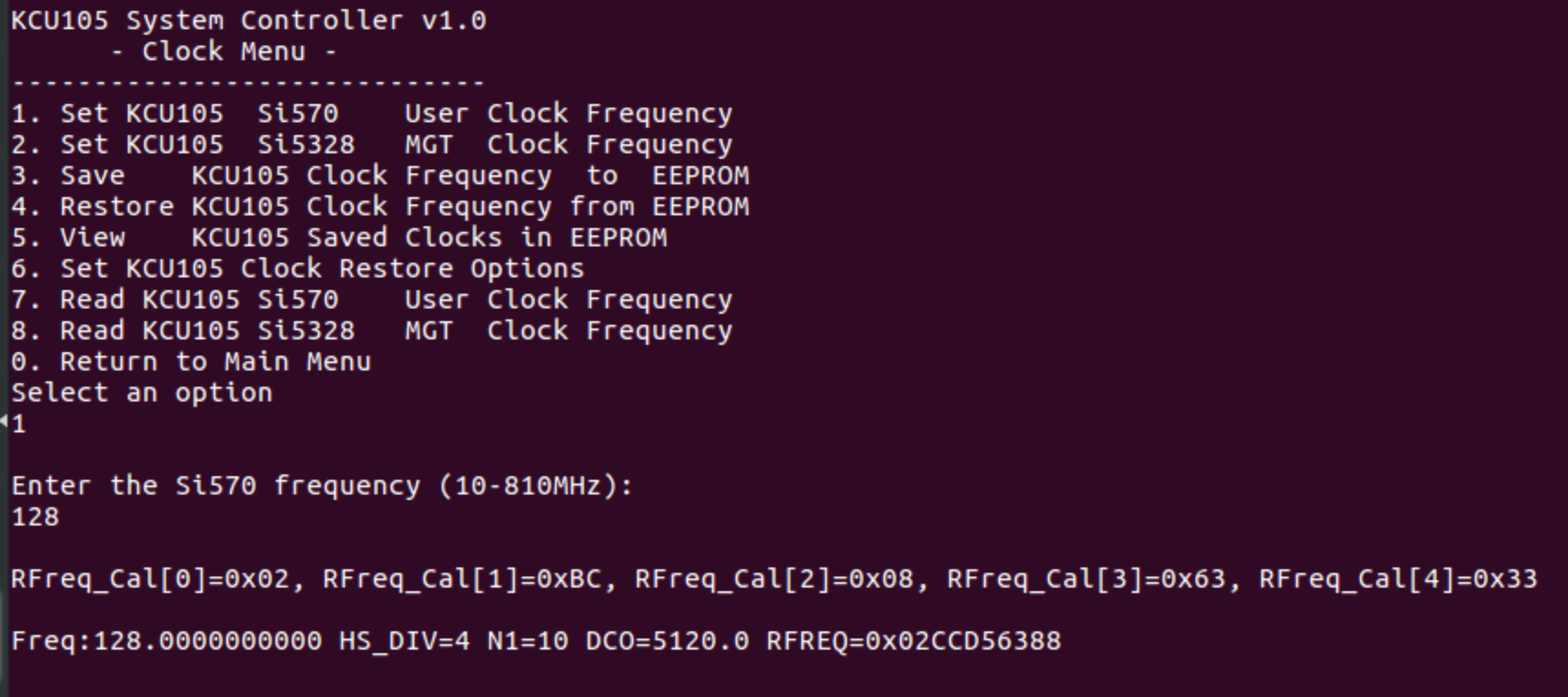

Program the KCU105 Clock

The programmable Si570 clock is connected to Quad 227 MGTREFCLK0, which is used in the IBERT firmware. The default output frequency of Si570 is 156.25MHz, so, need to change it to 128MHz.

You need software "minicom" in Linux OS, or "putty" in windows OS. I just use the minicom as an example.

- connect KCU105 UART interface to your PC

- power on KCU105 board

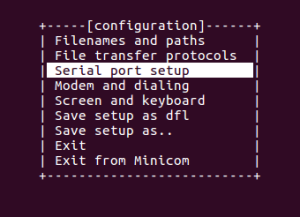

- in the linux PC, open a terminal, and start the minicom with root permission: $ sudo minicom -s

- Serial port setup: ,

- you will see the KCU105 system controller clock menu:

- input "1" to set KCU105 Si570 User Clock Freq, and input "128" to set it to 128MHz

- you could read KCU105 Si570 clock frequency to confirm

Computer to control the FPGA board

Vivado Lab Edition

If you don't need to compile the firmware on your own PC, you can only download the vivado lab edition for controlling FPGA. This edition is much much smaller than the full vivado software (~100GB)

https://www.xilinx.com/support/download.html

Vivado to program the FPGA

- connect your PC to the JTAG interface of KCU105

- power on the board

- start vivado

- open hardware manager

- open target, and choose "auto connect":

- if it failed to see the FPGA, please check the USB cable connection, and check your PC has correctly installed the JTAG interface driver.

- for windows OS, the driver is always installed when you install vivado (or vivado lab edition)

- for linux OS, need to manually install the driver, see here: https://www.xilinx.com/support/documentation/sw_manuals/xilinx2021_2/ug973-vivado-release-notes-install-license.pdf#page=47

Pre-compiled firmware list

KC705, 1.25Gbps IBERT, CPLL

bit file: CPLL_example_ibert_7series_gtx_0.bit

source code: ibert_kc705_1p25Gbps_CPLL.tar.gz

KC705, 1.25Gbps IBERT, QPLL

bit file: example_ibert_7series_gtx_0.bit

source code: ibert_7series_gtx_0_ex.tar.gz

KCU105, 1.28Gbps IBERT, QPLL (need to config the Si570 User Clock to 128MHz)

bit file: example_ibert_ultrascale_gth_0.bit

source code: ibert_ultrascale_gth_0_ex.tar.gz

KCU105, 1.5625Gbps IBERT, QPLL (with the KCU105 default clock setting)

bit file: 1p5625_example_ibert_ultrascale_gth_0.bit

source code: ibert_kcu105_speed1p56.tar.gz

KCU105, 1.25Gbps IBERT, CPLL (with the KCU105 default clock setting)

bit file: 1p25_CPLL_example_ibert_ultrascale_gth_0.bit

source code:ibert_kcu105_speed1p25_defaultClk_CPLL.tar.gz

KCU105, 1.5625Gbps IBERT, CPLL (with the KCU105 default clock setting)

bit file:1p5625_CPLL_example_ibert_ultrascale_gth_0.bit

source code:ibert_kcu105_speed1p5625_defaultClk_CPLL.tar.gz