...

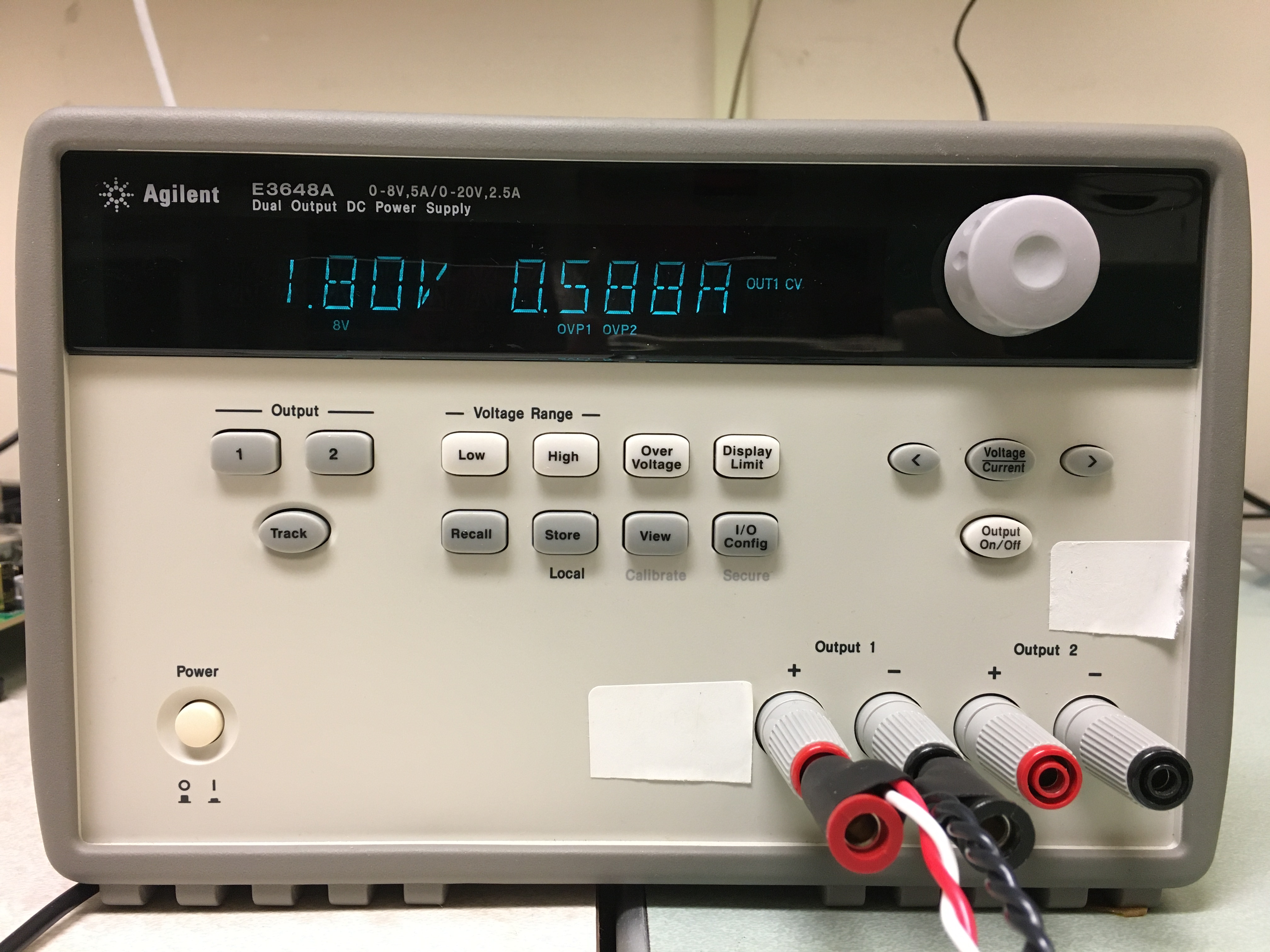

RD53A Single Chip Card | Power Supply with Output 1 set to 1.8V |

|---|---|

ZCU102 | miniDP connection on YARR PC |

Hardware Info

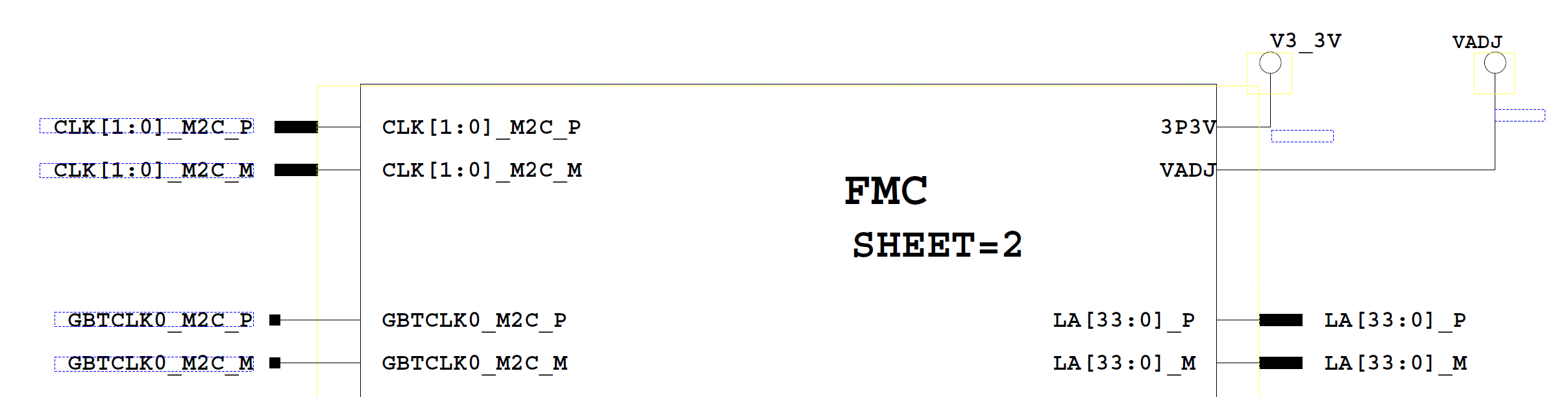

SLAC FMCv3: https://confluence.slac.stanford.edu/display/AIRTRACK/PC_256_101_00_C03

FMC pin mapping: (LA[33:30] is not used by the FMC adaptor)

General Setup

Preparing an SD card for ZCU102

...

Reboot ZCU102 after you update the FPGA firmware and RCE driver

Useful IP Addresses

If you can not find your machine here, open up the file /etc/hosts on rddev111 for a full list.

RCE DAQ access

...

B84, room B231 (lab C)

...

zcu102_1.atlas.lab

...

LinkAgg board for lpGBT Emulator

the hardware project page: https://confluence.slac.stanford.edu/display/AIRTRACK/PC_256_101_02_C01

...

C01-01

...

Compiling YARR Software for RCE DAQ

### RCE Guide

- for ARM target cross compilers are provided by the RCE_SDK

- installtion instructions: https://twiki.cern.ch/twiki/bin/viewauth/Atlas/RCEGen3SDK

- using CMake:

- ``$ source /opt/rce/setup.sh (for RCE cross compilation setup)``

- ``$ export CENTOS7_ARM32_ROOT=/opt/rce/rootfs/centos7 #(points to cross installed CentOS7)``

- ``$ export CENTOS7_ARM64_ROOT=/opt/rce/rootfs/centos7_64 #for ZCU102 ``

- ``$ git clone --single-branch --branch devel_rogue_fastMultichip_master_v1p2p2 https://gitlab.cern.ch/YARR/YARR.git Yarr``

- ``$ cd Yarr``

- ``$ mkdir build``

- ``$ cd build``

- select one of the supported toolchains

- ``$ cmake3 .. -DYARR_CONTROLLERS_TO_BUILD="Spec;Emu;Rogue" -DCMAKE_TOOLCHAIN_FILE=../cmake/linux-clang # requires clang installed on Linux ``

- ``$ cmake3 .. -DYARR_CONTROLLERS_TO_BUILD="Spec;Emu;Rogue" -DCMAKE_TOOLCHAIN_FILE=../cmake/linux-gcc # gcc 7.3 or higher ``

- ``$ cmake3 .. -DYARR_CONTROLLERS_TO_BUILD="Spec;Emu;Rogue" -DCMAKE_TOOLCHAIN_FILE=../cmake/rce-arm32 # ARM32/Centos7 on RCE ``

- ``$ cmake3 .. -DYARR_CONTROLLERS_TO_BUILD="Spec;Emu;Rogue" -DCMAKE_TOOLCHAIN_FILE=../cmake/rce-arm64 # ARM64/Centos7 on zcu102 ``

- ``$ make -j8 install ``

Run YARR SW in RCE DAQ

- Run YARR SW in ZCU102

- copy bin/scanConsole to ZCU102

- copy configs folder to ZCU102

- run scanConsole for single digital scan: ``./scanConsole -r configs/controller/ZCU102_rogueCfg.json -c configs/connectivity/example_rd53a_setup.json -s configs/scans/rd53a/std_digitalscan.json -p``

- ``scripts/fast_tune-rd53a.sh`` to tune Rd53a Syn+Diff+Lin FE

- Multi-Scan Console is another convinient tool to run a list of scan

- run scanConsole for multi-digital scan in fast mode(without plotting, without save FE cfg file): ``./bin/multiScanConsole -r configs/controller/ZCU102_lpGBTEmu_rogueCfg.json -c configs/connectivity/example_rd53a_lpGBTEmu_SCC_setup.json -l configs/scans/rd53a/linkScan_scanList.json -f``

- Tuning for Rd53a Syn+Diff+Lin FE: ``./bin/multiScanConsole -r configs/controller/ZCU102_rogueCfg.json -c configs/connectivity/example_rd53a_setup.json -S configs/scans/rd53a/tune_scanList.json -p``

- Tuning for Rd53a Diff+Lin FE: ``./bin/multiScanConsole -r configs/controller/ZCU102_rogueCfg.json -c configs/connectivity/example_rd53a_setup.json -S configs/scans/rd53a/tune_scanList_noSync.json -p``

- Running link Data Transmission Scan: ``python runLinkScan.py``

- Run YARR SW in HSIO2+KCU105

- copy bin/scanConsole to HSIO2

- copy configs folder to HSIO2

- run scanConsole: ``./scanConsole -r configs/controller/HSIO2_KCU105_rogueCfg.json -c configs/connectivity/example_rd53a_setup.json -s configs/scans/rd53a/std_digitalscan.json -p``

Useful IP Addresses

If you can not find your machine here, open up the file /etc/hosts on rddev111 for a full list.

RCE DAQ access

| Board Name | IP | Location |

|---|---|---|

| ZCU102 | 192.168.4.31 | B84, room B231 (lab C) |

| ZCU102, zcu102_1.atlas.lab | 192.168.4.32 | B84, room B282 (student office) |

Power Supply access for Rd53a

...

2) add "enable/disable Rx" switch to firmware to improve the analog scan performance. So, no need for long sleeping time after ECR.

Mar 8, 2022:

sync with YARR SW master branch 1.3.1

new branch: https://gitlab.cern.ch/YARR/YARR/-/tree/master_v1p3p1_rogue

Mar 14, 2022:

fixed the bugs for multiple chip running

new branch: https://gitlab.cern.ch/YARR/YARR/-/tree/master_v1p3p1_rogue

Mar 21, 2022:

improved for data transmission test, and has the rceRd53aScanConsole and rceRd53aMultiScanConsole