The SLAC ATLAS group

The ATLAS group at SLAC is large, and continues to grow rapidly as we anticipate the start of LHC physics. ATLAS is supported as a top priority of the SLAC laboratory, taking over from BaBar as the main high-energy physics activity. We have two professors (Su Dong, Ariel Schwartzman), several senior researchers (Rainer Bartoldus, Charlie Young, Richard Partridge), a Panofsky Fellow (Andy Haas), ~10 research scientists, ~8 postdocs, and 5 students.

Physics

Our physics activities focus on searches for new physics and measurements of the top quark cross-section and other SM processes. Searches are underway for gluinos which have come to rest in the calorimeter and decay during empty bunch crossings, excess like-sign leptons, a 4th generation quark, R-Parity violating Supersymmetry, light pseudoscalar Higgs in the NMSSM, long-lived particles in Hidden Valley models, and "lepton-jets". We will also measure the production of top quark pair production in the b+MET+jets final-state, which is also a background to many SUSY searches. Many tools are developed for use in these analyses, and for use by the collaboration as a whole, such as an algorithm which matches clusters of tracks with jets in the calorimeter, studies of jet calibration, b-tagging, b-jet triggering, and b/c-jet separation. SLAC is a Tier2 computing facility, and provides strong support for data analysis and simulation efforts.

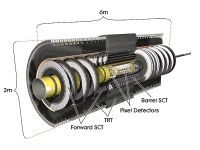

Detector

The group plays a major role in the operation of the Pixel detector, building on SLAC's long experience in silicon detector technology. We are also very involved in the triggers and data-aquisition (TDAQ) system, working on the TDAQ software and infrastructure, as well as high-level triggers. And we contribute to the simulation software, with expertise in GEANT4 modeling. SLAC is also proposing major roles in several projects that will address the planned ATLAS upgrades, including the B-layer pixel insertion upgrade and TDAQ upgrades based on cutting-edge serial I/O + FPGA technology.