Introduction

This confluence page describes how to build the firmware. For this project, there are two flavors of firmware: "Simple" and "PGP".

Licensing

If you are building on a SLAC server:

$ cd /u1/ExampleRceProject/firmware

$ source setup_env.csh

If you are building on a remote server, you (or your IT department) will be responsible for setting up the FLEX_LM licensing server and install Vivado software

Vivado Version

Currently, all firmware targets are locked to Vivado Version 2014.4 and will not build if otherwise.

Creating a build output directory

$ cd /u1/ExampleRceProject/firmware

$ mkdir build

Building SimpleDpm and SimpleDtm

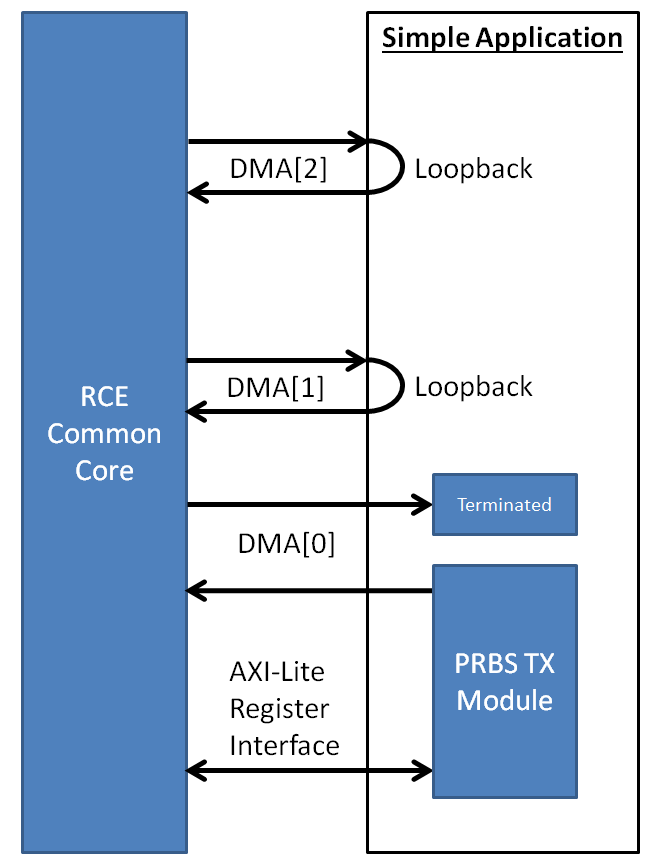

This is a simple example firmware that has no high speed IOs interfaces. DMA[2:1] are configured as loopback channels. The outbound DMA[0] channel is terminated to prevent back pressure if sent from software. The inbound DMA[0] channel is connected to a PseudoRandom Binary Sequence generator (PRBS TX). By default, the PRBS TX module is constantly generating data on the inbound DMA[0] channel.

The following are the steps to building the firmware .bit image file:

$ cd /u1/ExampleRceProject/firmware/target/SimpleDpm/

$ make

$ cd /u1/ExampleRceProject/firmware/target/SimpleDtm/

$ make

Building PgpDpm and PgpDtm

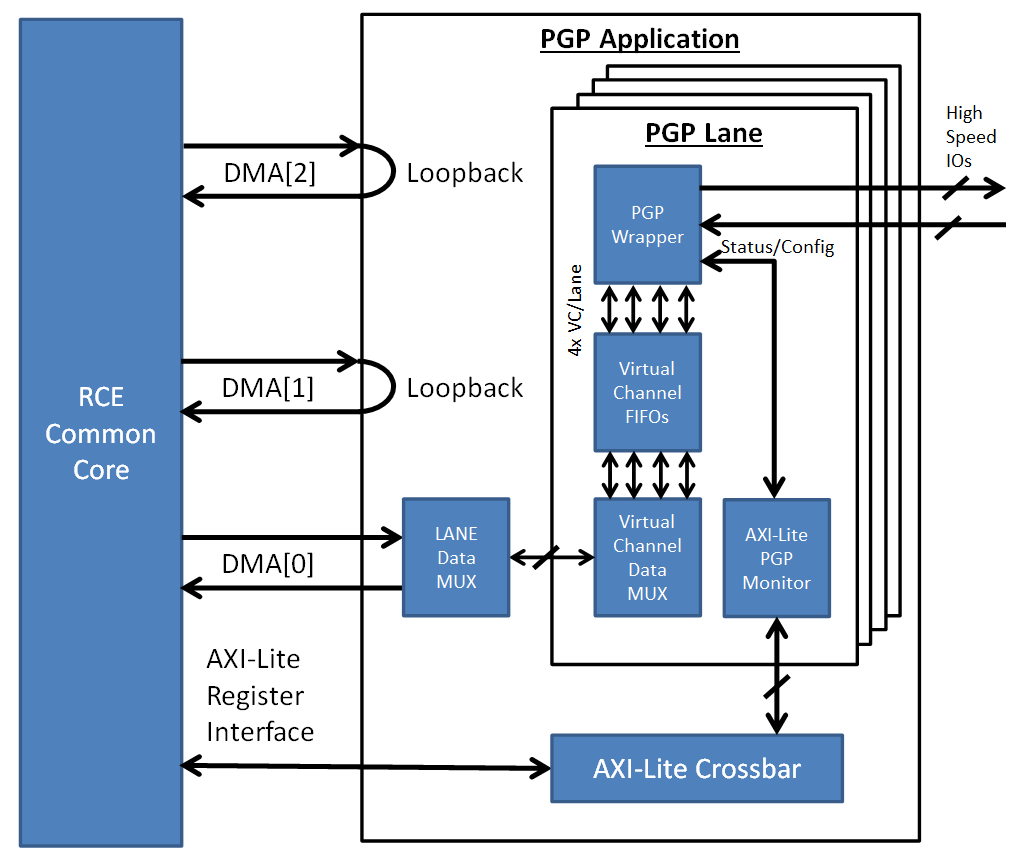

This is an example firmware that uses the high speed IOs interfaces on the RTM. The communication protocol for the high speed IOs is Pretty Good Protocol (PGP). The PGP link speeds are all configured for 3.125 Gbps. DMA[2:1] are configured as loopback channels. Inbound and outbound DMA[0] channel is connected to a data multiplexer/demultiplexer, which multiplexes the data to/from the different PGP lanes. Each PGP lane has a data multiplexer/demultiplexer, which multiplexes the data to/from the different PGP virtual channels within a lane. In between the virtual channel data multiplexer/demultiplexer and the PGP IP core wrapper are FIFOs for buffering. Also attached to the PGP IP core wrapper is a AXI-Lite PGP monitor, which monitors the status and configures the PGP IP core wrapper. All the AXI-Lite PGP monitor modules are connected to a AXI-Lite crossbar module. The AXI-Lite crossbar handles arbitration between the different AXI-Lite slave register module to the AXI-Lite master software register interface.

The following are the steps to building the firmware .bit image files:

$ cd /u1/ExampleRceProject/firmware/target/PgpDpm/

$ make

$ cd /u1/ExampleRceProject/firmware/target/PgpDtm/

$ make

Updating the .bit image on the SD memory card

The .bit image on the SD memory card can be updated using the following commands:

$ scp $TARGET_PATH root@$IP_ADDRESS:/mnt/boot/fpga.bit

$ ssh root@$IP_ADDRESS

# sync

# reboot

Where $TARGET_PATH is the path to the new .bit file and $IP_ADDRESS is the IP address of the RCE that you want to update. The "sync" command synchronizes the SD memory card.