Page History

...

| Code Block | ||

|---|---|---|

| ||

### Setup the library ###

import pyrogue as pr

import os, sys

import matplotlib.pyplot as plt

import time

import datetime

import numpy as np

import math

import pprint

import inspect

top_level=f'{os.getcwd()}/../'

rootTopLevel = top_level+'script/'

pr.addLibraryPath( rootTopLevel )

import setupLibPaths

import ePix320kM as devBoard

args = None

# ONLY RUN ONCE!

# Defining root

root = devBoard.Root(

top_level = rootTopLevel,

dev = '/dev/datadev_0',

pollEn = False,

initRead = True,

serverPort = 9099,

pciePgpEn = True,

)

root.start()

# example showing a read

AxiVersion = root.Core.AxiVersion

print ( '###################################################')

print ( '# Firmware Version #')

print ( '###################################################')

AxiVersion.printStatus()

print ( '###################################################')

# Useful short names

APP = root.App

AXIV = root.Core.AxiVersion

ASICTOP = APP.AsicTop

TRIG = ASICTOP.TriggerRegisters

ASIC0 = APP.Mv2Asic[0]

ASIC1 = APP.Mv2Asic[1]

ASIC2 = APP.Mv2Asic[2]

ASIC3 = APP.Mv2Asic[3]

HSDAC = APP.Dac.FastDac

PKREG = [None] * 4

PKREG[0] = ASICTOP.DigAsicStrmRegisters0

PKREG[1] = ASICTOP.DigAsicStrmRegisters1

PKREG[2] = ASICTOP.DigAsicStrmRegisters2

PKREG[3] = ASICTOP.DigAsicStrmRegisters3

BATCHER0 = ASICTOP.BatcherEventBuilder0

BATCHER1 = ASICTOP.BatcherEventBuilder1

BATCHER2 = ASICTOP.BatcherEventBuilder2

BATCHER3 = ASICTOP.BatcherEventBuilder3

DEBUG0 = root._dbg[0]

DEBUG1 = root._dbg[1]

DEBUG2 = root._dbg[2]

DEBUG3 = root._dbg[3]

DATARCV0 = root.DataReceiver0

DATARCV1 = root.DataReceiver1

DATARCV2 = root.DataReceiver2

DATARCV3 = root.DataReceiver3

FULLRATERCV0 = root.fullRateDataReceiver[0]

FULLRATERCV1 = root.fullRateDataReceiver[1]

FULLRATERCV2 = root.fullRateDataReceiver[2]

FULLRATERCV3 = root.fullRateDataReceiver[3]

DAC = APP.Dac

REGCTRL = ASICTOP.RegisterControlDualClock

# Configure clock to 168 MHz and configures all ASICS

root.InitASIC([3,1,1,1,1])

# disable some software rogue data receivers

root.disableAndCleanAllFullRateDataRcv()

root.enableDataRcv(False)

root.enableDataDebug(False)

#run some triggers and exercise lanes and locks

frames = 5000

rate = 1000

root.hwTrigger(frames, rate)

#get locked lanes

root.getLaneLocks()

#Enable data receivers and run some triggers

root.enableDataRcv(True)

root.enableAllAsics(True)

root.Trigger() # one event via software trigger

# Obtain descrambled single frame data from ASICs from DataReceiver. Data receiver is do

wn sampled.

root.printDataReceiverStatus()

frame = [None for i in range(4)]

for asicIndex in range(4):

frame[asicIndex] = getattr(root, f"DataReceiver{asicIndex}").Data.get()

#frame dimensions

for asicIndex in range(root.numOfAsics):

print(np.shape(frame[asicIndex]))

#plot image

plt.subplots(2,2,figsize=(17,17))

for asicIndex in range(root.numOfAsics):

if asicIndex == 3 :

plt.subplot(2,2,3)

elif asicIndex == 2 :

plt.subplot(2,2,4)

else :

plt.subplot(2,2,asicIndex+1)

if np.shape(frame[asicIndex])[0] != 1 :

plt.imshow(frame[asicIndex])

plt.xlabel("ASIC {}".format(asicIndex))

plt.colorbar()

else :

plt.xlabel("ASIC {}: No data".format(asicIndex)) |

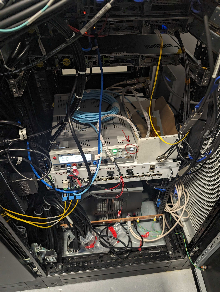

Teststand: (timing is left fiber, registers are on middle MPO8 fiber, data is on right MPO8 fiber)

Overview

Content Tools