The PETACACHE experiment at SLAC

# **Cluster Element Module**

An I/O System On Chip

# **Design proposal**

Document Version: Document Issue: Document Edition: Document Status: Document ID: Document Date: 0.4 3 English Draft - for internal distribution only To be assigned April 5 , 2007

This document has been prepared using the Software Documentation Layout Templates that have been prepared by the IPT Group (Information, Process and Technology), IT Division, CERN (The European Laboratory for Particle Physics). For more information, go to http://framemaker.cern.ch/.

# Abstract

To be written.

## Hardware compatibility

This document assumes the following hardware revisions: TBD.

## Intended audience

TBD

## **Conventions used in this document**

Certain special typographical conventions are used in this document. They are documented here for the convenience of the reader:

- Field names are shown in bold and italics (*e.g.*, *respond* or *parity*).

- Acronyms are shown in small caps (*e.g.*, SLAC or CDS).

- Hardware signal or register names are shown in Courier bold (*e.g.*, RIGHT\_FIRST or LAYER\_MASK\_1)

## References

- 1 Preliminary Product Specification of the *Xilinx* Virtex-4 Family Overview, dated June 17, 2005

- 2 Data sheet for the Cisco SFS 7012P and 7024P Infiniband Server Switch

- 3 Data sheet for the *SilverStorm* 9024 (SDR/DDR) *Infiniband* Switch

- 4 Data sheet for the *DataDirect Networks* S2A9500 *Infiniband* Modular RAID Storage Networking System

- 5 Product Data sheet for the *Verari* VS7000i, Native *Infiniband* Storage System

- 6 "Proposal for LSST R & D", no date or revision given.

- 7 *Infiniband* Architecture Specification Volume 1, Release 1.2. Dated October 2004 (final release).

- 8 Optical Design Parameters, Proposed Camera Coordinate System, Proposed Numbering Systems. *Martin Nordby*, Camera Team Meeting, 1 February 2006

- 9 Data sheet for the *Micron* 576Mb CIO Reduced Latency (RLDRAM II), part number MT49H64M9, dated September, 2005.

- 10 *Xilinix* Virtex-4 Family Overview, Preliminary Product specification, dated February 10, 2006

- 11 Strawman design for the Science Array DAQ Subsystem (SDS), dated February 23, 2006. *Michael Huffer*

Note: For additional resources, refer to xxx on the Camera Control System:

http://www-lsst.slac.stanford.edu/Elec\_DAQ/Elec\_DAQ\_home.htm

Click *<u>Hardware</u>* and then click, *<u>List of all documents</u>*.

# **Document Control Sheet**

| Document   | Title:                                                      | Cluster Element Module De                                        | esign proposa | 1                  |

|------------|-------------------------------------------------------------|------------------------------------------------------------------|---------------|--------------------|

|            | Version:                                                    | 0.4                                                              |               |                    |

|            | Issue:                                                      | 3                                                                |               |                    |

|            | Edition:                                                    | English                                                          |               |                    |

|            | ID:                                                         | To be assigned                                                   |               |                    |

|            | Status:                                                     | Draft - for internal distribut                                   | tion only     |                    |

|            | Created:                                                    | February 9, 2002                                                 |               |                    |

|            | Date:                                                       | April 5 , 2007                                                   |               |                    |

|            | Access:                                                     | Z:\Private\pcp\CEM\v0.4                                          | hrontmatter.  | fm                 |

|            | Keywords:                                                   | TBD                                                              |               |                    |

| Tools      |                                                             |                                                                  | Version:      | 6.0                |

| 10013      | DTP System:                                                 | Adobe FrameMaker                                                 | version.      | 0.0                |

| 10013      | DTP System:<br>Layout<br>Template:                          | Adobe FrameMaker<br>Software Documentation<br>Layout Templates   | Version:      | V2.0 - 5 July 1999 |

|            | Layout                                                      | Software Documentation                                           |               |                    |

| Authorship | Layout<br>Template:<br>Content                              | Software Documentation                                           | Version:      |                    |

|            | Layout<br>Template:<br>Content<br>Template:                 | Software Documentation<br>Layout Templates<br>                   | Version:      |                    |

|            | Layout<br>Template:<br>Content<br>Template:<br>Coordinator: | Software Documentation<br>Layout Templates<br><br>Michael Huffer | Version:      |                    |

Table 1 Document Control Sheet

## **Document Status Sheet**

| Table 2 | Document Status Sheet |

|---------|-----------------------|

|---------|-----------------------|

| Title:  | Cluster El  | Cluster Element Module Design proposal |                   |  |  |  |  |  |  |  |  |  |

|---------|-------------|----------------------------------------|-------------------|--|--|--|--|--|--|--|--|--|

| ID:     | To be assig | o be assigned                          |                   |  |  |  |  |  |  |  |  |  |

| Version | Issue       | Date                                   | Reason for change |  |  |  |  |  |  |  |  |  |

| 0.0     | 1           | 6/30/2006                              | Initial draft     |  |  |  |  |  |  |  |  |  |

# **Table of Contents**

| Abstract                           | • |  |  |  | • | • | • |  | • | • | • | • | • | .3 |

|------------------------------------|---|--|--|--|---|---|---|--|---|---|---|---|---|----|

| Hardware compatibility             | • |  |  |  |   | • |   |  | • | • |   | • | • | .3 |

| Intended audience                  | • |  |  |  |   |   |   |  |   |   |   |   | • | .3 |

| Conventions used in this document. | • |  |  |  |   | • |   |  |   | • |   | • | • | .3 |

| References                         | • |  |  |  |   | • |   |  | • | • |   | • | • | .4 |

| Document Control Sheet             | • |  |  |  |   | • |   |  |   | • |   |   | • | .5 |

| Document Status Sheet              | • |  |  |  |   | • |   |  | • | • |   |   | • | .5 |

| List of Figures                    |   |  |  |  |   |   |   |  | • | • |   |   |   | 13 |

| List of Tables                     | • |  |  |  |   | • |   |  |   |   |   |   | • | 15 |

| Chapter 1                          |   |  |  |  |   |   |   |  |   |   |   |   |   |    |

| Overview                           |   |  |  |  |   |   |   |  |   |   |   |   |   | 17 |

| 1.1 Introduction                   |   |  |  |  |   |   |   |  |   |   |   |   |   |    |

| 1.2 The Memory Subsystem .         |   |  |  |  |   |   |   |  |   |   |   |   |   |    |

| 1.3 DCR Bus Usage                  |   |  |  |  |   |   |   |  |   |   |   |   |   |    |

| 1.3.1 Bus Map                      |   |  |  |  |   |   |   |  |   |   |   |   |   |    |

| 1.3.2 Register Conventions         |   |  |  |  |   |   |   |  |   |   |   |   |   |    |

| Chapter 2                          |   |  |  |  |   |   |   |  |   |   |   |   |   |    |

| Configuration Memory               |   |  |  |  |   |   |   |  |   |   |   |   | • | 21 |

| 2.1 Introduction                   |   |  |  |  |   |   |   |  |   |   |   |   |   | 21 |

| 2.2 Page organization and page     |   |  |  |  |   |   |   |  |   |   |   |   |   |    |

| 2.3 Root block                     |   |  |  |  |   |   |   |  |   |   |   |   |   |    |

| 2.4 File organization                                     |       |      |   |   | • | • |     |   | • |   | • |   |   |   |   | • | 23 |

|-----------------------------------------------------------|-------|------|---|---|---|---|-----|---|---|---|---|---|---|---|---|---|----|

| 2.5 DCR Interface                                         |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 25 |

| 2.5.1 Transfer Control Register .                         |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 26 |

| 2.5.2 Transfer Address Register                           |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 26 |

| 2.5.3 Transfer Data Register                              |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| Chapter 3                                                 |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| Processor Bootstrapping                                   |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 29 |

| 3.1 Introduction                                          |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 3.2 Bootstrap Block                                       |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 3.3 DCR Interface                                         |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 3.3.1 Restart Options Register                            |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

|                                                           |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| Chapter 4                                                 |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   | 01 |

| The Packet Interface Core (PIC)                           |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.1 Introduction                                          |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.1.1 Packet model                                        |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.1.2 The Transfer Model and Transfer                     |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.1.3 Building blocks                                     |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.1.3.1 Transfer Blocks                                   |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.1.3.2 Interrupt Summary Bl                              |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.1.4 Connecting the blocks                               |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.2 The Transaction Descriptor                            |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.3 The Transaction Completion Descr                      | -     |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.3.0.1 Invalid payload length                            |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.3.0.2 Invalid header address                            |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.3.0.3 Invalid payload addre                             |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.3.0.4 Data under-run                                    |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.4 Events, Conditions and the Transa                     |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.4.1 FIFO parameters                                     | • •   | •    | • | • | • | • |     | • | • | • | • | • | • | • | • | • | 44 |

| $4.5$ Events $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | • •   | •    | • | • | • | • |     | • | • | • | • | • | • | • | • | • | 44 |

| 4.6 Faults                                                | • •   | •    | • | • | • | • |     | • | • | • | • | • | • | • | • | • | 45 |

| 4.7 The Pending Export Block                              |       | •    | • | • | • | • |     | • | • | • | • | • | • | • | • | • | 46 |

| 4.7.1 Parameters                                          |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.7.2 The PEB's Transaction FIFO                          |       | •    | • | • | • | • |     | • | • | • | • | • | • | • | • | • | 48 |

| 4.7.3 Faults triggered by a Protoco                       | ol Co | re   | • | • | • | • |     | • | • | • | • | • | • | • | • | • | 49 |

| 4.7.3.1 Data Pipeline Empty                               |       |      | • | • | • | • |     | • | • | • | • | • | • | • | • | • | 49 |

| 4.7.3.2 Status Pipeline Full .                            |       |      | • | • | • | • |     | • | • |   | • | • | • |   | • | • | 49 |

| 4.7.4 Faults triggered by a Protoco                       | ol Dr | iveı | 1 | • | • | • |     | • | • |   | • | • | • |   | • | • | 49 |

| 4.7.4.1 Invalid Transfer Descr                            | -     |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.7.4.2 No such ECB                                       |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.7.4.3 Export FIFO Full                                  |       |      |   |   |   |   |     |   |   |   |   |   |   |   |   |   |    |

| 4.8 The Export Complete Block                             |       | •    | • | • | • | • | • • | • | • |   |   |   |   |   |   | • | 50 |

| 4.8.1 Parameters                                                       |  |   | • |   |   | • | • | 52 |

|------------------------------------------------------------------------|--|---|---|---|---|---|---|----|

| 4.8.2 The ECB's Transaction FIFO                                       |  |   |   |   |   |   |   | 52 |

| 4.8.3 Faults triggered by a Protocol Core                              |  |   |   |   |   |   |   | 53 |

| 4.8.4 Faults triggered by a Protocol Driver                            |  |   |   |   |   |   |   | 53 |

| 4.9 The Free-List Block                                                |  |   |   |   |   |   |   | 53 |

| 4.9.1 Parameters                                                       |  |   |   |   |   |   |   | 54 |

| 4.9.2 The FLB's Transaction FIFO                                       |  |   |   |   |   |   |   | 55 |

| 4.9.3 Faults triggered by a Protocol Core                              |  |   | • | • | • | • | • | 56 |

| 4.9.4 Faults triggered by a Protocol Driver                            |  |   | • | • | • | • | • | 56 |

| 4.9.4.1 Invalid Transfer Descriptor                                    |  |   | • | • | • | • | • | 56 |

| 4.9.4.2 Freelist Full                                                  |  |   |   | • | • |   |   | 56 |

| 4.10 The Pending Import Block                                          |  |   | • | • | • | • | • | 57 |

| 4.10.1 Parameters                                                      |  |   | • | • | • | • | • | 58 |

| 4.10.2 The PIB's Transaction FIFO                                      |  |   | • | • | • | • | • | 58 |

| 4.10.3 Faults triggered by a Protocol Core                             |  | • |   | • | • | • | • | 59 |

| 4.10.3.1 No such FLB                                                   |  |   |   |   |   |   |   | 60 |

| 4.10.3.2 Data Pipeline Full                                            |  |   |   |   |   |   |   | 60 |

| 4.10.4 Faults triggered by a Protocol Driver                           |  |   |   |   |   |   |   |    |

| 4.11 The Interrupt Summary Block                                       |  |   |   |   |   |   |   | 60 |

| 4.11.1 Parameters                                                      |  |   |   |   |   |   |   | 61 |

| 4.12 The Export transaction                                            |  |   |   |   |   |   |   | 61 |

| 4.12.1 Data structures for a successful export transaction             |  |   |   |   |   |   |   | 62 |

| 4.12.2 Data structures for a failed export transaction                 |  |   |   |   |   |   |   | 63 |

| 4.13 The Import transaction                                            |  |   |   |   |   |   |   | 64 |

| 4.13.1 Data structures for a successful import transaction             |  |   |   |   |   |   |   | 65 |

| 4.13.2 Data structures for a failed import transaction                 |  |   |   |   |   |   |   | 67 |

| 4.14 The protocol engine message transaction                           |  |   |   |   |   |   |   | 68 |

| 4.14.1 Data structures for a message transaction                       |  |   |   |   |   |   |   |    |

|                                                                        |  |   |   |   |   |   |   |    |

| Chapter 5                                                              |  |   |   |   |   |   |   |    |

| The PIC Front-End Interface                                            |  |   |   |   |   |   |   |    |

| 5.1 Introduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |  |   |   |   |   |   |   |    |

| 5.1.1 Terminology $\ldots$ $\ldots$ $\ldots$ $\ldots$                  |  |   |   |   |   |   |   |    |

| 5.1.2 Post-processing and completion status                            |  |   |   |   |   |   |   |    |

| 5.1.3 What to do if a data or status pipeline is full?                 |  |   |   |   |   |   |   |    |

| 5.2 Exporting                                                          |  |   |   |   |   |   |   |    |

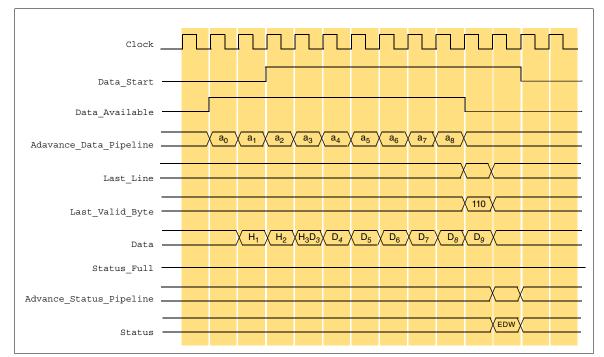

| 5.2.1 Advancing the export pipeline                                    |  |   |   |   |   |   |   | 73 |

| 5.2.2 PEB Signal Descriptions                                          |  |   |   |   |   |   |   | 74 |

| 5.2.2.1 Export-Clock                                                   |  |   |   |   |   |   |   |    |

| 5.2.2.2 Export-Data Available                                          |  |   |   |   |   |   |   |    |

| 5.2.2.3 Export-Data Start                                              |  |   |   |   |   |   |   | 75 |

| 5.2.2.4 Export-Advance Data Pipeline      |  | • |  |   |  |   |  |  | 75  |

|-------------------------------------------|--|---|--|---|--|---|--|--|-----|

| 5.2.2.5 Export-Data Last Line             |  | • |  | • |  |   |  |  | 75  |

| 5.2.2.6 Export-Data Last Valid Byte .     |  | • |  | • |  |   |  |  | 75  |

| 5.2.2.7 Export-Data                       |  |   |  | • |  |   |  |  | 75  |

| 5.2.2.8 Export-Advance Status Pipeline    |  | • |  | • |  |   |  |  | 76  |

| 5.2.2.9 Export-Status                     |  | • |  | • |  |   |  |  | 76  |

| 5.2.2.10 Export-Status Full               |  |   |  | • |  |   |  |  | 76  |

| 5.2.2.11 Export-Core Reset                |  | • |  | • |  |   |  |  | 76  |

| 5.2.3 Transfer data structure             |  | • |  | • |  |   |  |  | 76  |

| 5.2.4 Timing examples                     |  | • |  | • |  |   |  |  | 77  |

| 5.2.5 Export Post-processing              |  | • |  | • |  |   |  |  | 79  |

| 5.3 Importing                             |  | • |  | • |  |   |  |  | 81  |

| 5.3.1 PIB Signal Descriptions             |  | • |  | • |  |   |  |  | 82  |

| 5.3.1.1 Import-Clock                      |  | • |  | • |  |   |  |  | 82  |

| 5.3.1.2 Import-Freelist                   |  | • |  | • |  | • |  |  | 82  |

| 5.3.1.3 Import-Advance Data Pipeline      |  |   |  |   |  |   |  |  | 82  |

| 5.3.1.4 Import-Data Last Line             |  |   |  |   |  |   |  |  | 83  |

| 5.3.1.5 Import-Data Last Valid Byte .     |  |   |  |   |  |   |  |  | 83  |

| 5.3.1.6 Import-Data                       |  |   |  |   |  |   |  |  | 83  |

| 5.3.1.7 Import-Data Pipeline Full         |  |   |  |   |  |   |  |  | 83  |

| 5.3.1.8 Import-Core Reset                 |  | • |  |   |  |   |  |  | 83  |

| 5.3.2 Transfer data structure             |  |   |  |   |  |   |  |  | 84  |

| 5.3.3 Timing examples                     |  |   |  |   |  |   |  |  | 85  |

| 5.3.4 Import Post-processing              |  |   |  |   |  |   |  |  | 86  |

|                                           |  |   |  |   |  |   |  |  |     |

| Chapter 6 The PIC DCR Interface           |  |   |  |   |  |   |  |  |     |

| 6.1 The PEB (Pending Export Block)        |  |   |  |   |  |   |  |  |     |

| 6.1.1 Control and Status Register (CSR) . |  |   |  |   |  |   |  |  |     |

| 6.1.2 Export Pending Register             |  |   |  |   |  |   |  |  |     |

| 6.1.3 Export Fault Register               |  |   |  |   |  |   |  |  |     |

| 6.2 The ECB (Export Complete Block)       |  |   |  |   |  |   |  |  |     |

| 6.2.1 Control and Status Register (CSR) . |  |   |  |   |  |   |  |  |     |

| 6.2.2 Export Complete Register            |  |   |  |   |  |   |  |  |     |

| 6.2.3 Export Complete Fault Register      |  |   |  |   |  |   |  |  |     |

| 6.3 The FLB (Freelist Block)              |  |   |  |   |  |   |  |  |     |

| 6.3.1 Control and Status Register (CSR) . |  |   |  |   |  |   |  |  |     |

| 6.3.2 Freelist Register                   |  |   |  |   |  |   |  |  |     |

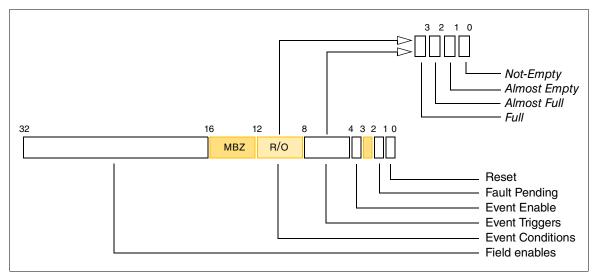

| 6.3.3 Freelist Fault Register             |  |   |  |   |  |   |  |  |     |

| 6.4 The (PIB) Pending Import Block        |  |   |  |   |  |   |  |  |     |

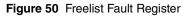

| 6.4.1 Control and Status Register (CSR) . |  |   |  |   |  |   |  |  |     |

| 6.4.2 Import Pending Register             |  |   |  |   |  |   |  |  |     |

| 6.4.3 Import Fault Register               |  |   |  |   |  |   |  |  | 101 |

| 6.5 The ISB (Interrupt Summary Block) | • |   | • |   |   |   |   | • | • |   |   | • |   | . 101 |

|---------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|-------|

| 6.5.1 Event Sources (Low) Register    | • |   | • |   |   | • |   | • | • |   |   | • |   | . 102 |

| 6.5.2 Event Sources (High) Register   |   | • | • | • | • | • | • |   |   | • | • | • | • | . 102 |

| 6.5.3 Fault Sources (Low) Register    | • |   | • | • |   | • | • | • | • | • | • | • | • | . 103 |

| 6.5.4 Fault Sources (High) Register   | • |   | • |   |   | • |   | • | • |   |   | • |   | . 103 |

# **List of Figures**

| Figure 1  | p. 18 | Data structures involved in a successful export transaction |

|-----------|-------|-------------------------------------------------------------|

| Figure 2  | p. 21 | TBD.                                                        |

| Figure 3  | p. 22 | Entity relationships                                        |

| Figure 4  | p. 23 | TBD                                                         |

| Figure 5  | p. 24 | TBD                                                         |

| Figure 6  | p. 25 | TBD                                                         |

| Figure 7  | p. 26 | Transfer Control register                                   |

| Figure 8  | p. 26 | Transfer Address Register                                   |

| Figure 9  | p. 26 | Transfer Data Register                                      |

| Figure 10 | p. 29 | TBD.                                                        |

| Figure 11 | p. 30 | Restart options register                                    |

| Figure 12 | p. 32 | CEM I/O model                                               |

| Figure 13 | р. 33 | Entity relationships                                        |

| Figure 14 | p. 34 | Packet model                                                |

| Figure 15 | p. 35 | Packet transfer model                                       |

| Figure 16 | p. 37 | Connecting the blocks                                       |

| Figure 17 | p. 38 | Transfer Descriptor                                         |

| Figure 18 | p. 41 | Transaction Completion Descriptor (TCD) and its EDW         |

| Figure 19 | p. 46 | Block diagram of the PEB                                    |

| Figure 20 | p. 48 | Structure of the TDE as used by the PEB                     |

| Figure 21 | p. 51 | Block diagram of the ECB                                    |

| Figure 22 | p. 52 | Structure of the TDE as used by the ECB                     |

| Figure 23 | p. 54 | Block diagram of the FLB                                    |

| Figure 24 | p. 55  | Structure of the TDE as used by the FLB                             |

|-----------|--------|---------------------------------------------------------------------|

| Figure 25 | p. 57  | Block diagram of the PIB                                            |

| Figure 26 | p. 59  | Structure of the TDE as used by the PIB                             |

| Figure 27 | p. 61  | Block diagram of the ISB                                            |

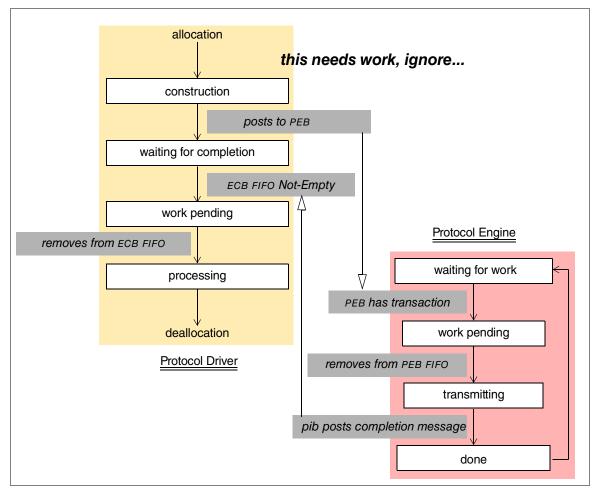

| Figure 28 | p. 62  | Typical lifetime of a Transfer Descriptor used to transmit a packet |

| Figure 29 | p. 63  | Data structures involved in a successful export transaction         |

| Figure 30 | p. 64  | Data structures involved in an unsuccessful export transaction      |

| Figure 31 | p. 65  | Typical lifetime of a Transfer Descriptor used to receive a packet  |

| Figure 32 | p. 66  | Data structures involved in a successful import transaction         |

| Figure 33 | p. 68  | Data structures involved in an unsuccessful import transaction      |

| Figure 34 | p. 69  | Information exchange for a protocol engine message transaction      |

| Figure 35 | p. 70  | Data structures involved in a protocol engine message transaction   |

| Figure 36 | p. 77  | Transfer structure for the PEB.                                     |

| Figure 37 | p. 78  | Timing diagram (one transfer) for the PEB                           |

| Figure 38 | p. 79  | Timing diagram for PEB three packet transfer                        |

| Figure 39 | p. 84  | Transfer structure for the PEB.                                     |

| Figure 40 | p. 85  | Timing diagram (one transfer) for the PIB                           |

| Figure 41 | p. 86  | Timing diagram for PIB three packet transfer                        |

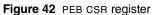

| Figure 42 | p. 90  | PEB CSR register                                                    |

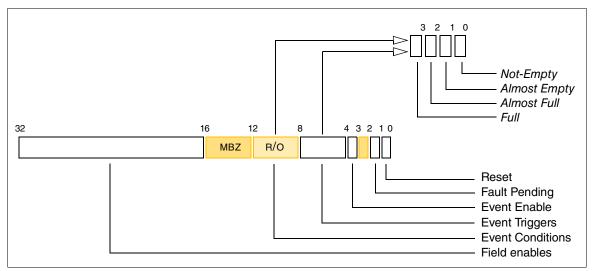

| Figure 43 | p. 92  | Export Pending Register                                             |

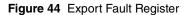

| Figure 44 | p. 92  | Export Fault Register                                               |

| Figure 45 | р. 93  | ECB CSR register                                                    |

| Figure 46 | p. 94  | Export Complete Register                                            |

| Figure 47 | p. 95  | Export Complete Fault Register                                      |

| Figure 48 | p. 96  | FLB CSR register                                                    |

| Figure 49 | p. 98  | Freelist Register                                                   |

| Figure 50 | p. 98  | Freelist Fault Register                                             |

| Figure 51 | p. 99  | PIB CSR register                                                    |

| Figure 52 | p. 101 | Import Pending Register                                             |

| Figure 53 | p. 101 | Import Fault Register                                               |

| Figure 54 | p. 102 | ISB event register (Low)                                            |

| Figure 55 | p. 103 | ISB event register (High)                                           |

| Figure 56 | p. 103 | ISB fault register (Low)                                            |

| Figure 57 | p. 104 | ISB fault register (High)                                           |

|           |        |                                                                     |

# **List of Tables**

| Table 1  | p. 5   | Document Control Sheet                                    |

|----------|--------|-----------------------------------------------------------|

| Table 2  | p. 5   | Document Status Sheet                                     |

| Table 3  | p. 25  | Register offsets for the PEB                              |

| Table 4  | p. 30  | Register offsets for the PEB                              |

| Table 5  | p. 42  | Reason and Parameter values for errors defined by the PIC |

| Table 6  | p. 74  | Signal definitions for the PEB                            |

| Table 7  | p. 82  | Signal definitions for the PIB                            |

| Table 8  | p. 89  | Register offsets for the PEB                              |

| Table 9  | p. 92  | Register offsets for the ECB                              |

| Table 10 | p. 95  | Register offsets for the FLB                              |

| Table 11 | p. 98  | Register offsets for the PIB                              |

| Table 12 | p. 102 | Register offsets for the ISB                              |

Chapter 1 Overview

## 1.1 Introduction

TBD

## 1.2 The Memory Subsystem

TBD

### 1.3 DCR Bus Usage

TBD

#### 1.3.1 Bus Map

All these relationships are illustrated in Figure 1:

Figure 1 Data structures involved in a successful export transaction

#### **1.3.2 Register Conventions**

The application interface to the CE consists of *registers* on the processor's DCR bus (see xxx). Registers on this bus are all thirty-two (decimal) bits wide. These registers are further broken down into *fields*, where a field is specified as a bit offset and length (in number of bits). Any

field used as a boolean has a width of one bit. A value of *one* (1) is used to indicate its *set* or *true* sense and a value of *zero* (0) to indicate its *clear* or *false* sense. Field numbering (bit offsets) for registers are such that *zero* (0) corresponds to a register's Least Significant Bit (LSB) and thirty-one (31) corresponds to a register's Most Significant Bit (MSB). Bit offsets are always specified in decimal, unless otherwise noted. There are four types of generic fields:

- **Not defined:** Undefined fields are identified as *Must Be Zero* (MBZ) and are illustrated *greyed out*. MBZ fields will:

- read back as zero

- ignore writes

- reset to zero

**Read/Write:** Read/Write fields will, on *Reset*, be set to *zero*.

- Selective Set and Clear (SSC): SSC fields are used where it is necessary to change one or more fields of a register and leave the remaining fields unchanged<sup>1</sup>. These fields will have a complementing *Enable* field. This field will have the same width as its corresponding SSC field. The Enable field for any arbitrary SSC field is found by shifting that field's bit offset by 16 (decimal). Enable fields are illustrated *lightly* greyed-out. These fields satisfy the following conventions:

- may only be *set*, clearing the field is ignored

- read back as zero

- SSC fields will:

- ignore writes, *unless* their corresponding field enables are also asserted

- reset to zero, unless otherwise documented

- **Read-Only:** Read-only fields are illustrated *lightly* greyed-out with their value. *Read-Only* fields will:

- ignore writes

- reset to *zero*, unless otherwise documented

Registers on the DCR bus are read using the mfdcr instruction and written using the mtdcr instruction. The literal offset of these instructions corresponds to the register's bus address.

<sup>1.</sup> Sometimes referred to as *indivisible* read/modify/write.

# Chapter 2 Configuration Memory

### 2.1 Introduction

TBD. This model is illustrated in Figure 2:

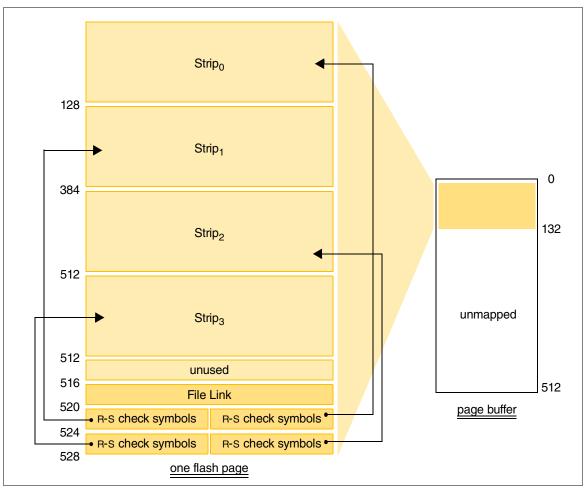

## 2.2 Page organization and page buffer

#### TBD.

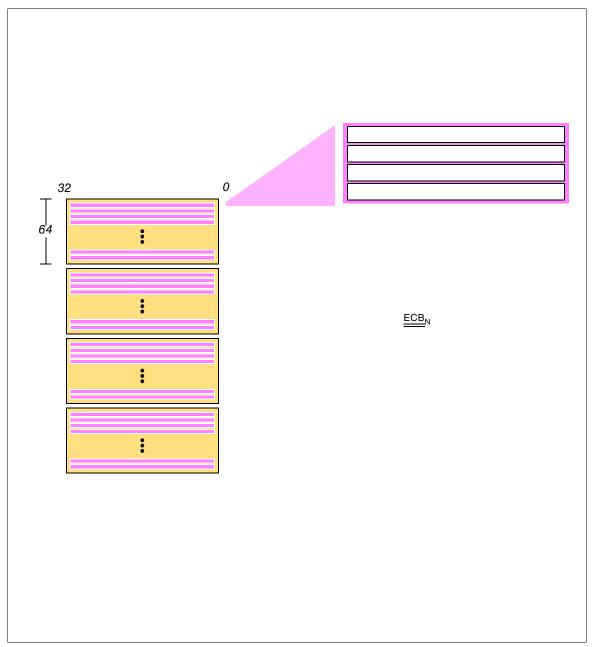

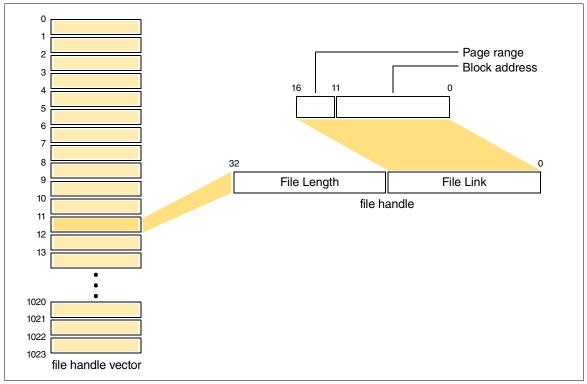

xxx are shown in Figure 3:

Figure 3 Entity relationships

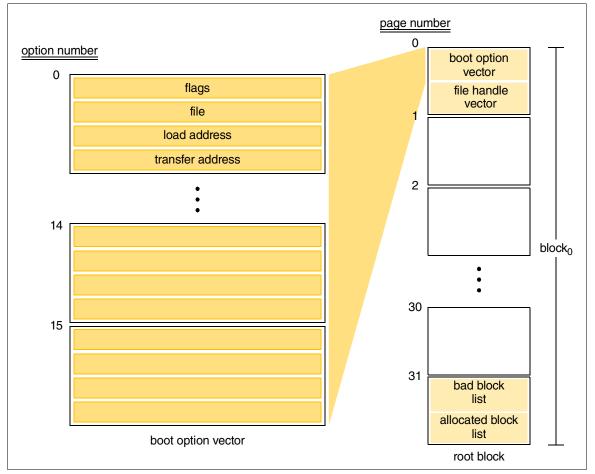

### 2.3 Root block

TBD. xxx are shown in Figure 4:

Figure 4 TBD

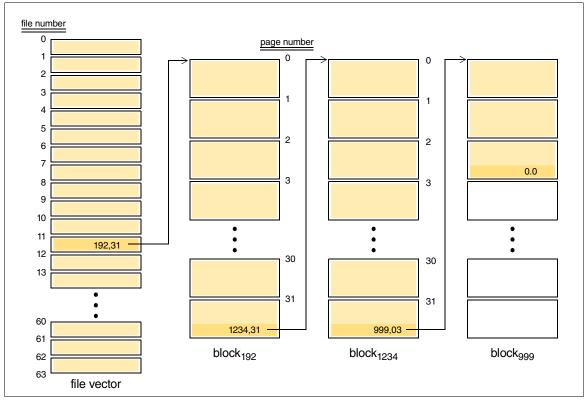

## 2.4 File organization

.

TBD. This model is illustrated in Figure 5:

TBD. This model is illustrated in Figure 6:

Figure 6 TBD

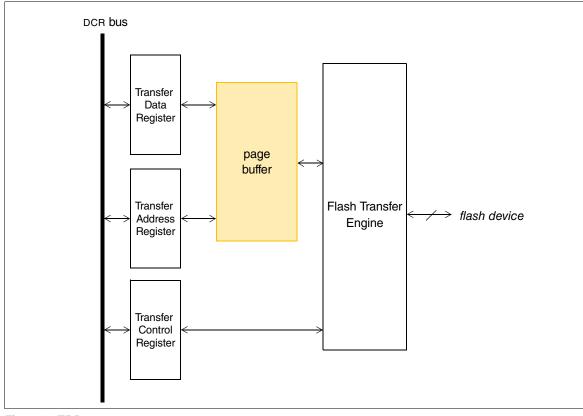

### 2.5 DCR Interface

The Back-End interface to the XXX consists principally of three registers. The location of these registers on the DCR bus relative to one another is enumerated in Table 3. The absolute location of these registers is specified as a block instantiation parameter.

| Offset <sup>1</sup> | Name | Description                                                                                        |

|---------------------|------|----------------------------------------------------------------------------------------------------|

| 0                   | TCR  | Transfer Control Register. See Section 2.5.1                                                       |

| 4                   | TAR  | Transfer address FIFO. See Section 2.5.2                                                           |

| 8                   | TDR  | Transfer Data REgister. Contains either the data read or the data to be written. See Section 2.5.3 |

1. In bytes

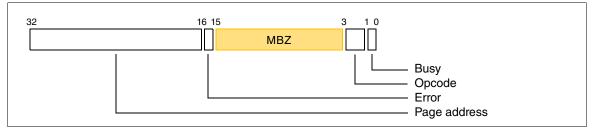

#### 2.5.1 Transfer Control Register

TBD. The structure of this register is illustrated in Figure 7:

Where:

**XXX:** TBD. Note: this is a *Selective Set and Clear* field (see Section 2.5). In order to reset the block the appropriate field enable must also be *set* (see below).

#### 2.5.2 Transfer Address Register

TBD. The structure of this register is illustrated in Figure 8:

Figure 8 Transfer Address Register

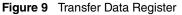

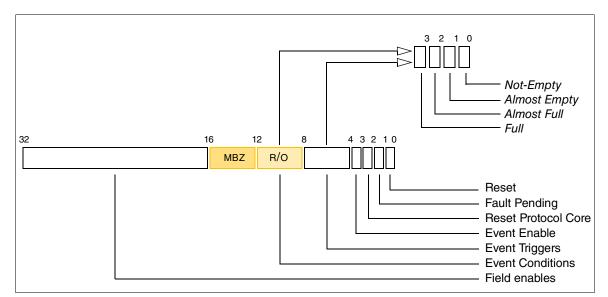

#### 2.5.3 Transfer Data Register

TBD. The structure of this register is illustrated in Figure 9:

# Chapter 3 **Processor Bootstrapping**

## 3.1 Introduction

TBD. This model is illustrated in Figure 10:

Figure 10 TBD.

TBD. This model is illustrated in Figure 10

### 3.2 Bootstrap Block

TBD.

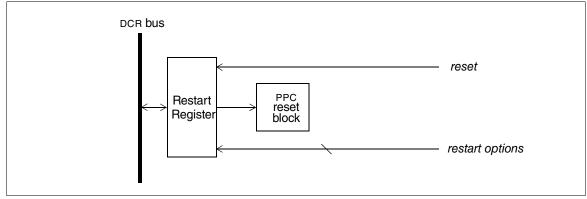

### 3.3 DCR Interface

The Back-End interface to the XXX consists of a single register. The location of this register on the DCR bus relative to one another is enumerated in Table 4. The absolute location of these registers is specified as a block instantiation parameter.

Table 4

Register offsets for the PEB

| Offset <sup>1</sup> | Name    | Description              |

|---------------------|---------|--------------------------|

| 0                   | RESTART | Restart options. See xxx |

1. In bytes

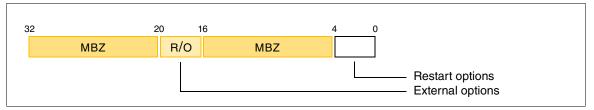

#### 3.3.1 Restart Options Register

TBD. The structure of this register is illustrated in Figure 11:

Where:

**XXX:** TBD. Note: this is a *Selective Set and Clear* field (see Section 1.3.2). In order to reset the block the appropriate field enable must also be *set* (see below).

# Chapter 4 The Packet Interface Core (PIC)

### 4.1 Introduction

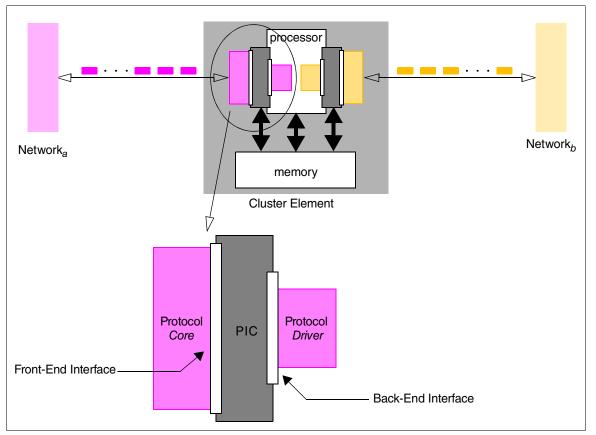

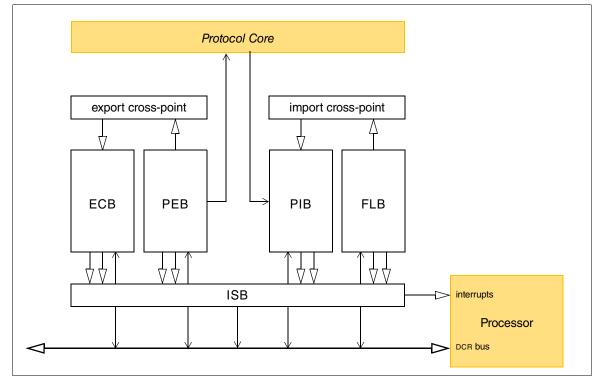

The CEM's I/O model allows external data transfers to move directly (with no processor intervention) from outside world to and from processor memory. Data is transferred from one or more protocol specific *networks*. The number and types of networks that are accessible to the CE are only constrained by the amount of resources available on the CE. While the detailed structure of data within each network is protocol specific, the model assumes data is always transferred between network and CE in units of *Packets*, as illustrated in Figure 12:

The Packet Interface Core (PIC) is a set of five different types of IP blocks designed to facility protocol implementation by providing a common interface, independent of protocol to efficiently transfer packets between networks and processor memory. The implementor interacts with these blocks through a series of *Interfaces*. The model assumes the sum of the intellectual effort to implement a specific protocol stack is partitioned into two domains:

- **The Protocol Core:** The set of hardware (VHDL) instructions which interact with the PIC. The protocol core uses the PIC's *Front-End* interfaces. The specification for these interfaces is given in Chapter 5. Typically, the protocol engine is comprised of a *protocol core*, elements of the PIC's Front-End Interface, and the logic to glue these components all together.

- **The Protocol** *Driver***:** The set of software (processor) instructions which interact with the PIC. The protocol core uses the PIC's *Back-End* interfaces. The specification for these interfaces is given in Chapter 6.

The relationship between a core, its corresponding driver and the PIC is illustrated in Figure 12:

Figure 12 CEM I/O model

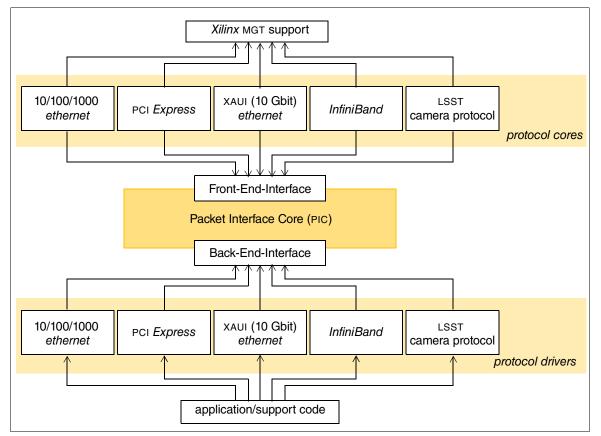

As a CE is realized using FPGAs from the *Virtex*-4 family (see [1]), it is assumed that a protocol core's physical layers will most likely (but, not necessarily) depend on the Multi-Gigibit-Transceivers (MGTs) provided by the FPGA. The dependencies between MGTs, potential protocol cores and drivers and the PIC are illustrated in Figure 14:

Figure 13 Entity relationships

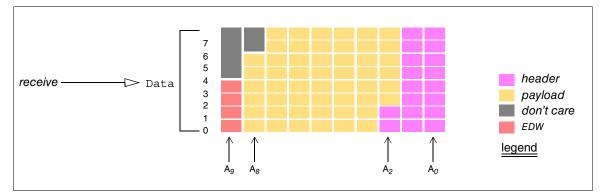

#### 4.1.1 Packet model

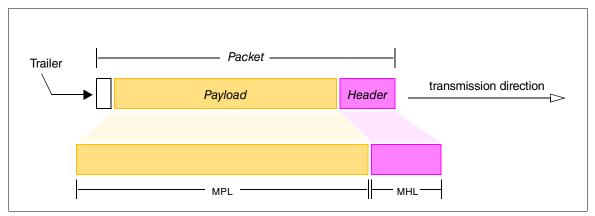

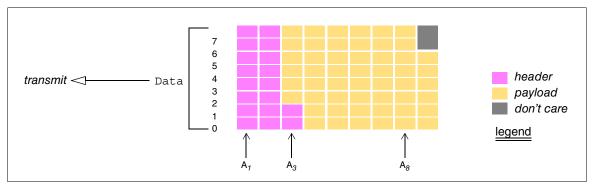

While the detailed structure of a packet is clearly protocol dependent, packets are assumed to share some common characteristics independent of protocol. In particular, all packets can be decomposed into three different components:

Header:The information necessary to describe and manage the packet content (see the<br/>*Payload* component below). For example, source and destination address,<br/>sequence numbers, QOS identifiers, etc... The Header always constitutes the first<br/>bytes of a packet either sent or received. The Header is always an integral number<br/>of *bytes*. For any given protocol the length of the Header is arbitrary, but *fixed*.<br/>This parameter is called the *Maximum Header Length* or MHL.

- **Payload:** The transferred information or content. The Payload immediately follows the Header. The Payload is always an integral number of bytes. Unlike Header length, Payload length is variable. For any given protocol the payload length can vary as a function of packet. However, to facility memory management, for any one protocol, packets must have a *maximum* length. This parameter is called the *Maximum Payload Length*, or MPL.

- **Trailer:** Packet integrity identifiers, for example, packet CRCs. The Trailer immediately follows the Payload and is an indeterminate number of bits. The model assumes the construction and use of the Trailer is outside its scope. (need some explanation here).

One of the responsibilities of the PIC is to enforce length constraints on both header and payload. This topic is discussed in 4.3. The abstract structure of a packet and its relationship with these constraints is illustrated within Figure 14:

Figure 14 Packet model

#### 4.1.2 The Transfer Model and Transactions

The PIC transfers packets in one of two directions. Any one transfer, in any one direction, is called a *Transaction*. Therefore:

- An *Export* transaction transfers a single packet *from* processor memory to network. The *Export Pending* and *Export Complete* blocks are the two principal PIC blocks used for an export transaction. These blocks are introduced in Section 4.1.3.1.

- An *Import* transaction transfers a single packet *to* processor memory from network. The *Import Pending* and *FreeList* blocks are the two principal PIC blocks used for an import transaction. These blocks are introduced in Section 4.1.3.1.

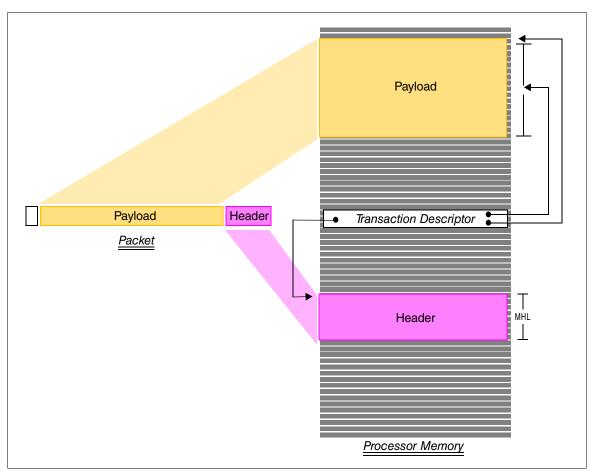

To the protocol core the PIC represents a packet as a single contiguous stream of data, while to the protocol driver, the PIC represents the packet as two separate components located in processor memory, one for header and one for payload. These components can to be located either contiguous with respect to one another or separately, at arbitrary locations within processor memory.

For an export transaction the export blocks will gather both header and payload from memory and transfer there contents to the protocol core for transmission as a single packet. For an import transaction, the protocol core hand a packet to the import blocks where its contents will be scattered to two individual locations in memory, one for the header and one for its payload. The relationship between a packet as seen by the protocol core and its representation in memory is illustrated in Figure 15:

Figure 15 Packet transfer model

Note that header and payload and are no longer necessarily contiguous with respect to one another in memory. The specification of *where* to either scatter or gather the components of a packet are specified in a data structure called the *Transaction Descriptor*. This is the central structure around which much of the dynamics of packet transfer revolve and is discussed below, in Section 4.2.

#### 4.1.3 Building blocks

From the user's perspective, the PIC consists of five different types of building blocks. Four of these blocks are used in packet transfers, one pair (the PEB and ECB) for export transactions and one pair (FLB and PEB) for import transactions. The fifth block (the ISB) is used to couple actions in the transfer blocks with interrupts in the processor. The export blocks communicate internally with each other through their *export* cross-point, while the import blocks communicate are actually hidden from the implementor and only come into existence when a system is instantiated (see xxx).

#### 4.1.3.1 Transfer Blocks

- **Pending Export Block (PEB):** Used to *initiate* export transactions. The block's Back-End Interface is used by a protocol driver to post export requests. This request is called a *Transaction Descriptor* (see Section 4.2). The block's Front-End Interface allows the protocol core to respond to those requests. When the protocol core is ready, the PEB gathers the packet's components and DMAs the assembled packet to the protocol core who transmits the packet. Once transmission is finished, the protocol core signals completion status to this block, which switches this information, through the export cross-point, to the appropriate ECB (see below). The PEB is discussed in additional detail within Section 4.7.

- **Export Complete Block (ECB):** Used to *complete* export transactions. The block's Front-End Interface is not directly accessible to the implementor, instead, this interface is connected to the export cross-point where it waits for completion messages from one or more PEBs (see above). These potential messages are re-formatted and DMA'd to memory as Transaction Completion Descriptors (see Section 4.3). The block's Back-End Interface allows the protocol driver to wait on completed export transactions. The ECB is discussed in additional detail within Section 4.8.

- **Free-List Block (FLB):** This block is used implicitly by a protocol core to allocate buffer space in memory for packets which are pending reception. Each buffer on the freelist describes one Transaction Descriptor. The block's Front-End Interface is not directly accessible to the implementor, instead, this interface is connected to the import cross-point where it waits for buffer requests from one or more PIBs (see below). The block's Back-End Interface is used by the protocol driver to replenish the freelist with the memory needed by the protocol core to buffer incoming packets. The FLB is discussed in additional detail within Section 4.8.3.

- **Pending Import Block (PIB):** The block's Front-End Interface is used by a protocol core to post completed import transactions. In order to determine where to locate the received packet, the interface uses a Transfer Descriptor allocated from a FLB (see above) and obtained through the import cross-point. The protocol driver uses the block's Back-End Interface to wait on completed import transactions. The PIB is discussed in additional detail within Section 4.10.

For each CE the total number of transfer style blocks which may be instantiated  $^1$  is sixty-four (64).

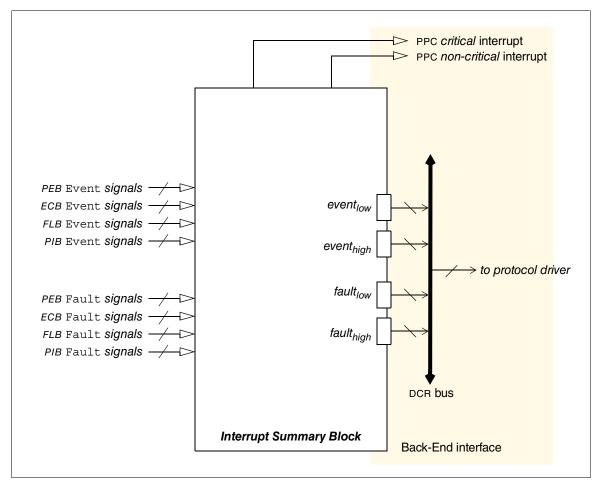

#### 4.1.3.2 Interrupt Summary Block (ISB)

The Interrupt Summary Block (ISB) aggregates the Event and Fault signals from any one of the four different types of transfers blocks. The ISB is discussed in additional detail within Section 4.11. For each CE there will be one, and only one ISB instantiated.

#### 4.1.4 Connecting the blocks

The number and types of blocks instantiated are specified at system build time. Each of the four transfer blocks are configurable and their exact configuration is also established at build time. Both number and type of block in any given system are driven by the specific protocol requirements. For example, if the protocol demands *QOS* (Quality-Of Service), it might require multiple pairs of blocks for different service levels or virtual channels. However, in the most trivial (and perhaps most common) case, a specific protocol would require only four blocks: A single PEB/ECB pair for packet transmission and one FLB/PEB pair for packet reception. This particular configuration is also sufficient to illustrate (see Figure 17) the connectivity established between the blocks by the PIC when a system is instantiated:

Figure 16 Connecting the blocks

<sup>1.</sup> Assuming the FPGA has sufficient resources

Therefore, to instantiate any one system, the PIC will:

- Instantiate both export and import cross-points.

- Instantiate an ISB.

- Instantiate all specified blocks using their corresponding parameters.

- Connect all the blocks Front-End interfaces to the DCR bus.

- Connect all the blocks Fault and Event signals to the ISB.

- Connect the ISB to the processor interrupt controller.

- Connect the ISB connected to DCR bus.

- Connect all ECBs and PEBs to the *export* cross-point.

- Connect all FLBs and PIBs to the *import* cross-point.

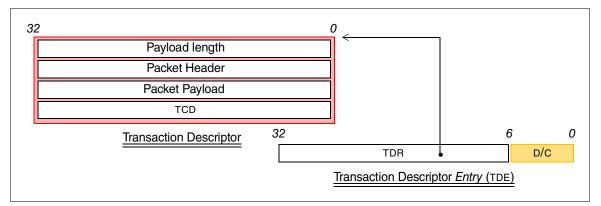

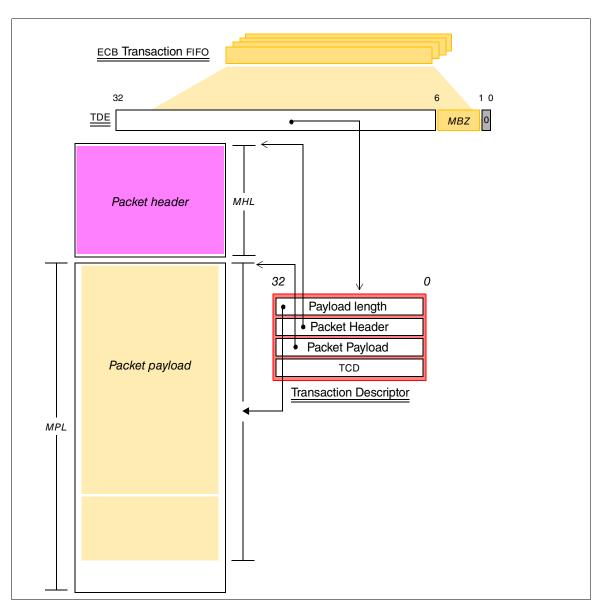

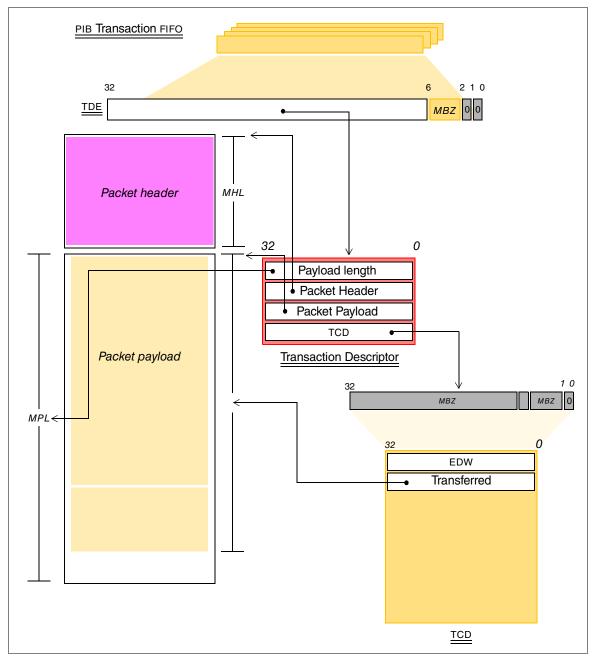

# 4.2 The Transaction Descriptor

The Transaction *Descriptor* is a 16-byte data structure which resides in physical memory and specifies all the information necessary to perform a single transaction. In the case of transmission the protocol driver posts this description to the PIC. In the case of reception, the order is reversed and the PIC posts this description to the protocol driver. The structure of a Transfer Descriptor is illustrated in Figure 17:

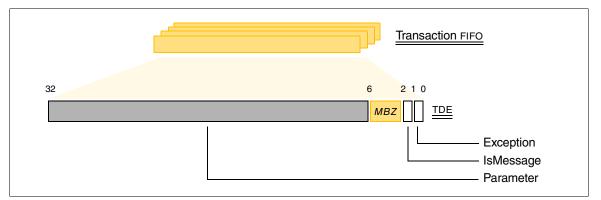

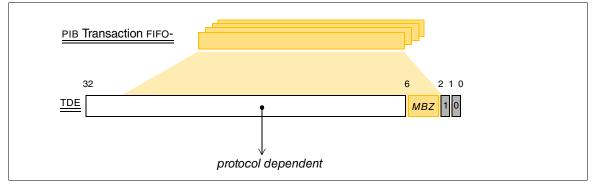

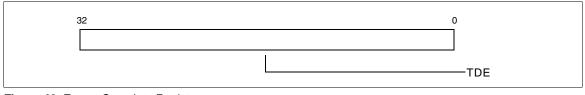

In actuality what is posted is not the descriptor, but instead its *address*. This address is called a Transaction Descriptor *Reference* or TDR. By convention all descriptors must be *64-byte* aligned, therefore the value of the low-order six bits of the address are redundant and a TDR can be (and is) represented in twenty-six bits. This allows the TDR to be encapsulated within a 32-bit word, while at the same time as reserving six of the word's bits for additional functionality. This word is called Transaction Descriptor *Entry*, or TDE. The relationship between Transaction Descriptor, TDR and TDE is illustrated within Figure 17. TDEs are the entities which are actually inserted, buffered and removed by the five different types of PIC blocks (see Section 4.4). The low-order six-bits of the TDE are overloaded and each block interprets these bits in a block specific fashion. For example, see the definition of the TDE used by the PIB

as described in Section 4.7.2. and illustrated within Figure 20. Returning to the Transaction Descriptor its fields are defined as follows:

- **Payload length:** The size of the packet payload expressed in bytes. In a descriptor used to *export* a packet the value of this field specifies the size of the payload of the packet to be transferred from memory to network. There are two constraints on the value of this field:

- It must be less then or equal to the MPL (see Section 4.1.1).

- It must not be *zero*,(0), unless the *IsContiguous* field of the corresponding TDE (see Section 4.8.2) is *true*.

If either of these two constraints are violated the corresponding transaction will abort with the EDW Reason code: INVALID\_PAYLOAD\_LENGTH (see Table 5).

In a descriptor used to *import* a packet, the value of this field sets the threshold for the maximum number of bytes which can be received for the corresponding packet. The value of this field must never exceed the MPL (see Section 4.1.1). If either this constraint is violated or the received packets exceeds the value of this field the corresponding transaction will abort with the EDW Reason code: INVALID\_PAYLOAD\_LENGTH (see Table 5).

- **Packet Header:** The base address of the packet *header* expressed in units of bytes with a value of *zero* corresponding to the first location in memory. This address must be 32-byte aligned. In a descriptor used to export a packet (see Section 4.12), the value of this field specifies the address of the packet header to be transferred from memory to network. In a descriptor used to import a packet (see Section 4.13) this field specifies the address of the buffer which is to contain the packet header transferred from network to memory. When used in a transaction, if the address is invalid the corresponding transaction will abort with the EDW Reason code: INVALID\_HEADER\_ADDRESS (see Table 5). A header address is invalid if it is either not 32-byte aligned (low-order five bits of the field are *not zero*), or any locations within the corresponding header are outside the physical address range of the CE.

- **Packet Payload:** The base address of the packet *payload* expressed in units of bytes with a value of *zero* corresponding to the first location in memory. This address must be *32-byte* aligned. In a descriptor used to export a packet (see Section 4.12), the value of this field specifies the address of the payload of the packet to be transferred from memory to network. In a descriptor used to import a packet (see Section 4.13) this field specifies the address of the buffer which is to contain the packet payload transferred from network to memory. The address is checked for validity in all cases, *except* an export transaction in which the *IsContiguous* field of the corresponding TDE (see Section 4.8.2) is *true*. In all other cases, if the address is invalid the corresponding transaction will abort with the EDW Reason code: INVALID\_PAYLOAD\_ADDRESS (see Table 5). A payload address is invalid if it is either not *32-byte* aligned (low-order five bits of the field are *not zero*), or any locations within the corresponding payload are outside the physical address range of the CE.

**TCD:** The address of an *Transaction Completion Descriptor* (TCD) expressed in units of bytes with a value of *zero* corresponding to the first location in memory. This address must be 32-byte aligned. The structure and usage of the TCD are discussed in Section 4.3. When used in a transaction, if this address is invalid a *fault* will be declared (see Section 4.6). A TCD address is invalid if it is either not 32-byte aligned (low-order five bits of the field are *not zero*), or the location is outside the physical address range of the CE.

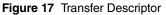

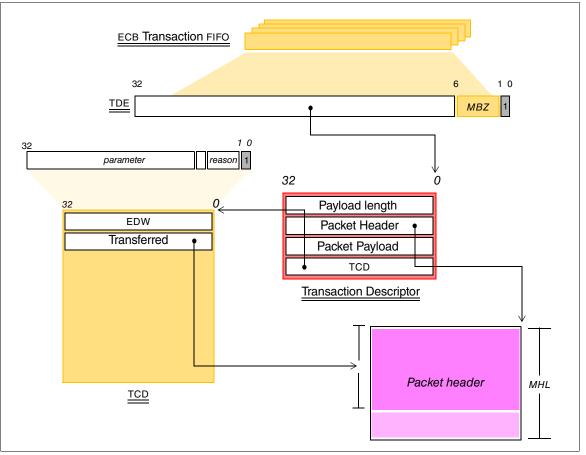

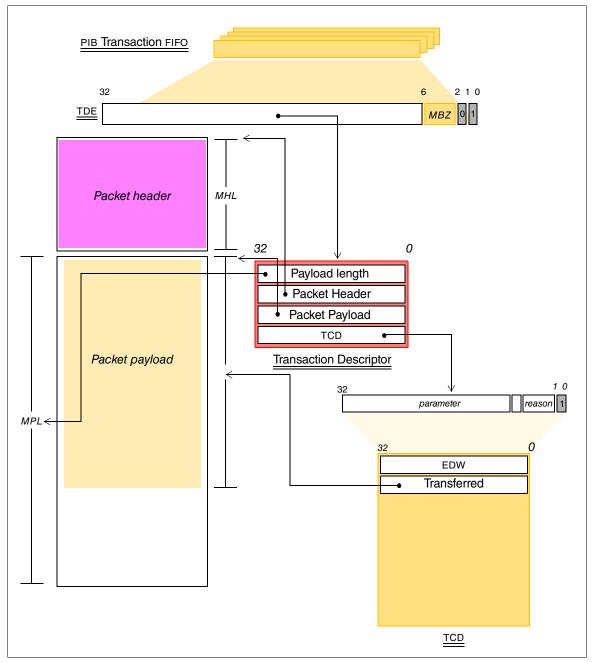

# 4.3 The Transaction Completion Descriptor (TCD)

Transactions can either succeed or fail. Their completion status is *defined* by a combination of the PIC and the appropriate protocol core and *read* and *used* by the protocol driver. And while all successes are the same, all failures are different, occurring at different points in a transaction and for different reasons. For example, the contents of the Transfer Descriptor could be invalid, or a packet received by a protocol driver could contain a CRC error. All this transaction completion information is encapsulated in a 32-byte structure, residing in physical memory called the Transaction Completion Descriptor, or TCD. The address of the TCD for any particular transaction is contained in a Transaction Descriptor described above (see Section 4.2). It is the responsibility of the protocol core and the PIC, working in concert, to deliver for each transaction a well-formed TCD. For the PIC, this is an explicit operation and for the protocol core this is an implicit operation. Implicit, because the protocol core is not exposed directly to the TCD. Instead it contributes completion status indirectly through a PIC block's Front-End interface. For example, when the protocol core finishes packet transmission, it passes its completion status by writing to the PEB's Status port (see Section 5.2.2.9). The structure of the TCD and its EDW is illustrated in Figure 18. The first word of the TCD is called the Error Description Word, or EDW, the second word is the actual transfer count and the remaining words are reserved and must be zero. The structure of the first word is called out separately, as the completion status value written by the protocol core is actually an EDW (see Section 5.2.5).

Figure 18 Transaction Completion Descriptor (TCD) and its EDW

where:

- **WasError:** This field determines the interpretation of the values of the higher-order fields. If this field is true (*set*) the values of the remaining fields are interpreted as specified below. If this field is false (*clear*), the value of the remaining fields are unspecified.

- **Error Reason:** A six-bit value which enumerates the reason the reported transaction failed. Reason values are protocol dependent, however, if the *WasBlock* field is *set* (see below), the origin of the error was the PIC itself. In such a case, the potential values for this field are enumerated in Table 5.

- WasBlock: This field determines whether the error originated within the PIC (i., e., in one or more of the four interface blocks described below). In such a case, this field is true (*set*) and both the *Error Reason* and *Error Parameter* fields are specified in Table 5. If this field is false (*clear*), the value of both the *Error Reason* and *Error Parameter* fields are protocol dependent.

- **Error Parameter:** A twenty-four-bit value which parameterizes the *Error Reason* field (see above). Parameter values are protocol dependent, however, if the *WasBlock* field is *set* (see above), the origin of the error was in the PIC itself. In such a case, the potential values for this field are enumerated in Table 5.

- **Transferred:** This field contains the number of bytes of the packet successfully transmitted or received.

Note: While an import transaction always writes the TCD on completion, on an *export* transaction the PIC only references and writes the TCD for a transaction when it *fails*. By not writing this structure when the transaction completes successfully (hopefully, the predominate case), the PIC saves both a cache-line fetch and write, thus contributing to improving the overall system throughput. Therefore, on any successful export transaction its

TCD will retain the values it had at the time its corresponding Transaction Descriptor was posted. It is considered good practice for the protocol driver to ensure the *wasError* field of the EDW is false (*clear*), before the corresponding descriptor is posted.

A TCD is composed by the PIC under two circumstances:

- Whenever either a PEB or FLB discovers inconsistency within a Transfer Descriptor.

- The protocol core generates an error in processing the request.

Its important to realize that in the first case the transaction takes an early exit and the request never reaches the protocol core.

| Reason                  |                    |                               |                 |

|-------------------------|--------------------|-------------------------------|-----------------|

| Name                    | Value <sup>1</sup> | Parameter                     | description     |

| INVALID_PAYLOAD_LENGTH  | 01                 | None (Must be Zero).          | Section 4.3.0.1 |

| INVALID_HEADER_ADDRESS  | 02                 | None (Must be Zero).          | Section 4.3.0.2 |

| INVALID_PAYLOAD_ADDRESS | 03                 | None (Must be Zero).          | Section 4.3.0.3 |

| DATA_OVER_RUN           | 62                 | None (Must be Zero).          | Section 4.3.0.4 |

| DATA_UNDER_RUN          | 63                 | None ( <i>Must be Zero</i> ). | Section 4.3.0.4 |

Table 5 Reason and Parameter values for errors defined by the PIC

1. In decimal.

#### 4.3.0.1 Invalid payload length

The value specified in the *Payload Length* field of the corresponding Transaction Descriptor was greater then MPL (see Section 4.1.1). In such a case the value of the *Parameter* field will be *zero* (0). Note: If more then one of the first three fields in the descriptor is invalid, this error will take precedence over the other two.

#### 4.3.0.2 Invalid header address

The value specified in the *Packet Header* field of the corresponding Transaction Descriptor is invalid for one or more of the following reasons:

- Its most significant bits do not match the RLDRAM base address.

- Its not cache (*32-byte*) aligned.

- Its relative offset within the RLDRAM is such that the data contained in the header will run past the end-of-memory.

In such a case the value of the *Parameter* field will be *zero* (0). Note: If the payload address is also invalid, this error will take precedence.

#### 4.3.0.3 Invalid payload address

The value specified in the *Packet Payload* field of the corresponding Transaction Descriptor is invalid for one or more of the following reasons:

- Its most significant bits do not match the RLDRAM base address.

- Its not cache (*32-byte*) aligned.

- Its relative offset within the RLDRAM is such that the data contained in the header will run past the end-of-memory.

In such a case the value of the *Parameter* field will be *zero* (0).

#### 4.3.0.4 Data under-run

The protocol core was attempting to export a packet, however the PEB's Front-End interface could not keep up with the rate at which the protocol core would wish to transmit the packet. See Section 5.2.5 for a more detailed discussion of this error. In such a case the value of the *Parameter* field will be *zero* (0).

# 4.4 Events, Conditions and the Transaction FIFO

Each one of the four different types of transfer blocks contains a *Transaction* FIFO (see, for example, the ECB described in Section 4.8). The transaction FIFO buffers transaction oriented requests between the protocol core and its corresponding protocol driver. For any one block, one port of the FIFO appears on the block's Front-End interface, while the other port is on its Back-End Interface. These are *asynchronous* FIFO's with the capacity to store up to 512 *x* 36 bit entries<sup>1</sup>. The abstract function of a transaction FIFO is two-fold:

- Decouple the processor's clock domain (the Back-End) from the clock domain required to operate any arbitrary protocol core (the Front-End).

- Decouple the rate a protocol core can post/retire transactions from the rate at which its corresponding protocol driver can post/retire transactions.

When in use, a FIFO can be in one of four states:

- Not-Empty

- Almost-Empty

- Almost-Full

- Full

<sup>1.</sup> With the intent of allowing FIFO implementation to map directly to the FPGA's block memory.

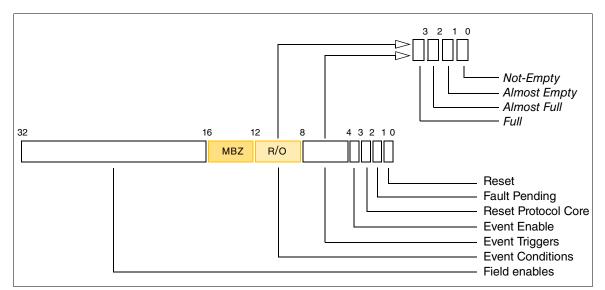

While the definition of *Almost-Empty* and *Full* are block invariant, the thresholds for the *Almost-Full* and *Almost-Empty* states may be specified on a per block basis. See Section 4.4.1 below for more information. When in use, a FIFO's current state is called its *condition*. The FIFO's condition can be monitored by the protocol driver through a field within a block's CSR register (see for example, the PEB's CSR register described in Section 6.1.1). In addition, some FIFO conditions are presented to the driver implicitly. For example, the PIB returns a sentinel value when its Transaction FIFO is read while *Empty* (see Section 6.4.2). However, the most important use of a FIFO's condition is to drive a block's Event signal. This signal is discussed in Section 4.5.

# 4.4.1 FIFO parameters

When a block is instantiated the user may specify the thresholds for two conditions of a block's transaction FIFO as follows:

- **Almost-Empty:** The threshold for asserting the *Almost-Empty* condition. The condition is asserted while the number of TDEs in the corresponding FIFO is less than or equal to the value of this parameter. The parameter is expressed in number of TDEs. The valid parameter values are between *zero* (0) and 510 (decimal) inclusive.

- Almost-Full: The threshold for asserting the *Almost-Full* condition. This condition is asserted while the number of TDEs in the corresponding FIFO is greater than or equal to the value of this parameter. The valid parameter values are between one (1) and 511 (decimal) inclusive.

# 4.5 Events

Each block defines an Event signal. When the block is instantiated, this signal is connected to the ISB (see Section 4.11). The ISB maps this signal to the processor's *non-critical* interrupt signal. Thus, whenever the block asserts its Event signal, a non-critical interrupt is triggered in the processor. This signal is formed by using, as input, the current condition of the block's Transaction FIFO (see Section 4.4) as well as the values of the *Event Triggers* and *Event Enable* fields found in the block's CSR register (see for example Section 6.1.1). Using these inputs the logic to form this signal is as follows:

- mask the current condition against the value of the *Event Triggers* field

- ORs the result

- mask this result against the *Event Enable* field

- if the result is *true*, the Event signal is *asserted*

The Event signal remains asserted until the condition which caused its assertion is removed. For example, if the *Not-Empty* condition of the transaction FIFO is used to trigger an event, then the Event signal will be deasserted only while the FIFO is empty.

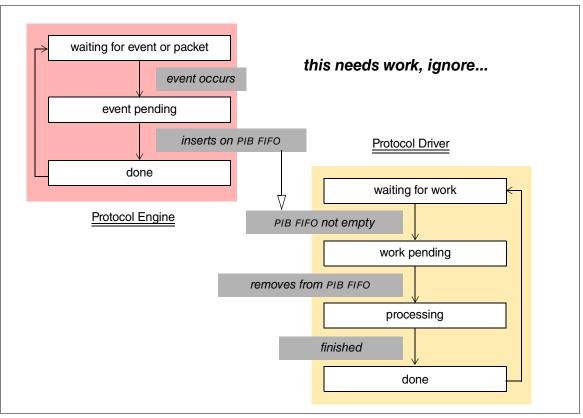

Events are intended to represent state transitions of a protocol engine which, in the normal course of operation, are expected to occur and are expected to be used by protocol core and driver to communicate changes in their relative states. For example, a protocol driver will need to "wait" for received packets. These packets will be delivered by the corresponding protocol core through its PIB (see Section 4.10). When the core has received a packet the PIB's transaction FIFO will be *Not-Empty*. Consequently, the protocol driver could use the *Not-Empty* event as an indication of packet arrival and could wait on its corresponding interrupt.

# 4.6 Faults

Each block contains one Fault signal. When the block is instantiated, this signal is connected to the ISB (see Section 4.11). The ISB maps this signal to the processor's *critical* interrupt signal. Thus, whenever a block asserts its Fault signal, a critical interrupt will be triggered in the processor.

Blocks may generate a fault through actions initiated by either the protocol driver, protocol core, or both. The description of each block enumerates the potential faults generated by that block, broken down by whether the fault originated through an action of the core or the driver. See for example, Section 4.7.3 and Section 4.7.4 which enumerate the potential faults generated by the PEB.

When the block determines from its inputs that a fault should be generated the following actions are taken by the block:

- The action (from either protocol core or driver) triggering the fault is rejected.

- If a fault is currently pending, no further action is taken.

- If a fault is *not* pending:

- The *Fault Pending* field of the block's CSR is *set*.

- The offending TDE is written to the block's *TDE Fault* register.

Unlike an event a fault persists (the signal remains asserted) even after the conditions which precipitated the fault are removed. Only the protocol driver can clear a pending fault. To clear a pending fault (deassert the signal) requires one of the following two actions:

- Clear the *Fault pending* field of the block's CSR (see, for example Section 6.1.3).

- Reset the block through its csr register.

For a description of these registers see Chapter 6. Note: Unlike an *Event* (see Section 4.5), a fault is *not* user maskable.

Note: Faults should be considered, in the normal course of operation, to never occur and their presence should be considered a logic or design error. Basically, they identify a non-recoverable error.

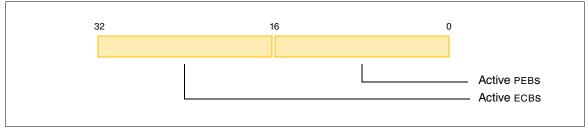

# 4.7 The Pending Export Block

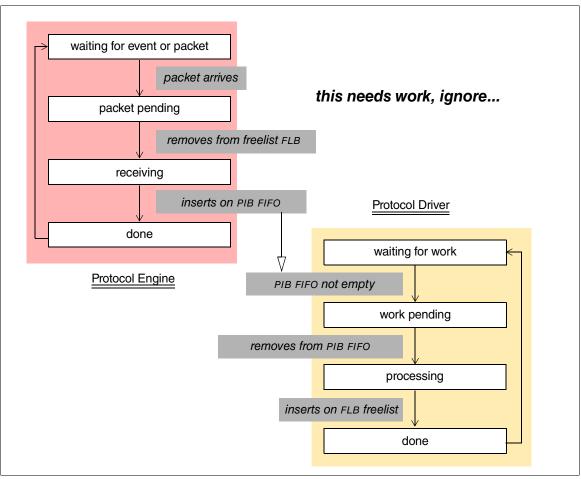

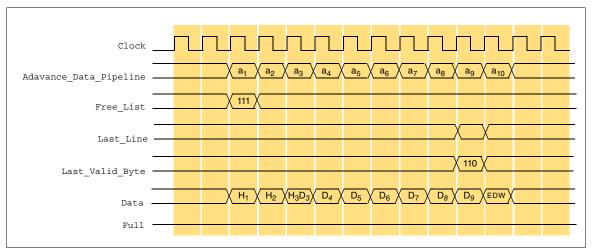

The Pending Export Block (PEB) is used to initiate a packet transfer from memory to network (an *export* transaction). A protocol driver initiates a transaction by queuing a TDE to the block's transaction FIFO through the block's Back-End Interface. When the PEB dequeues that request, it signals through its Front-End Interface, the corresponding protocol core. This core then requests (through this interface) the data corresponding to the transfer, packetizes these data and transmits the resulting packet onto the appropriate network.

Typically (depending on transaction parameterization), once the packet has been transmitted, the PIC locates and uses a ECB (see Section 4.8) to signal back to the protocol driver that the transaction is finished.

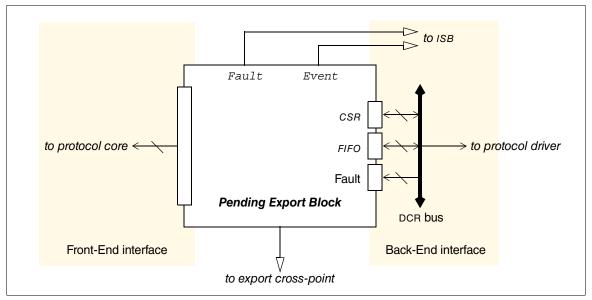

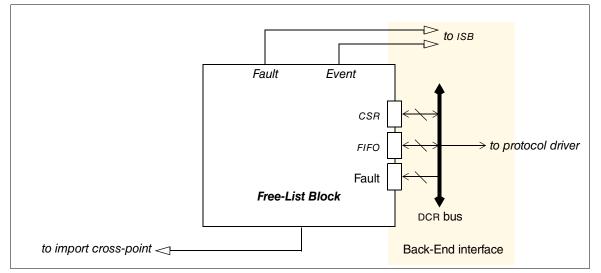

A more detailed discussion of the export transaction is found in Section 4.12. A block diagram of this interface is illustrated in Figure 19:

Figure 19 Block diagram of the PEB

The PEB's Front-End Interface is intended to interface with a protocol specific core. That is, a core's *Back-End* transmit interface "plugs" into the block's *Front-End* interface.

The block's Back-End Interface consists principally of an interface to the PEB's transaction FIFO. This FIFO buffers protocol driver originated TDEs. The description for the TDE associated with the PEB is found in Section 4.7.2. The FIFO's *write* port is connected to the processor's DCR

bus. A protocol driver writes to this port in order to queue transactions. The PEB controls access to the FIFO's corresponding *read* port and uses the information gained from this port to DMA both transfer descriptor and packet data. As these data arrive the Front-End Interface signals the protocol core that data is available.

The current condition of the transaction FIFO is used to drive the block's Event signal (see Section 4.5). When a block of this type is instantiated this signal as well as the Fault signal are automatically connected by the PIC to the ISB (see Section 4.11) and in this fashion FIFO conditions and/or the presence of a fault can used to trigger processor interrupts. The set of conditions which may assert the Event signal are configurable through the block's CSR register (see Section 6.1.1). This register is accessed through the DCR bus. A discussion of FIFO configuration is found in Section 4.11.

The specification for the Front-End Interface is found in Section 5.2. The specification for the Back-End Interface is found in Section 6.1.

The maximum number of PEBs which can be instantiated (consistent with the resources of the FPGA) can be no greater then sixteen (16).

## 4.7.1 Parameters

When a block of this type is instantiated (see Section 4.1.4) various block attributes must be assigned. These include:

- **Block number** This is a small enumeration from *zero* (0) to 15 (decimal) which is used to identify the instantiated block. If more then one block of this type is instantiated, each block must be assigned a unique number. This value is used to establish:

- The relative offset into DCR space for the registers of its Front-End Interface.

See Section 1.3.1 for a discussion of how this identifier maps to an absolute address on the DCR bus.

- The relative register number and bit offset in both the event and fault source registers of the ISB (see Section 6.5).

- **Almost-Full threshold:** This parameter specifies the threshold for the *Almost-Full* condition to be asserted by the block. See Section 4.4.1 for a discussion of this parameter.

- **Almost-Empty threshold:** This parameter specifies the threshold for the *Almost-Empty* condition to be asserted by the block. See Section 4.4.1 for a discussion of this parameter.

- **Header length:** The length (expressed in bytes) of the header of any packet posted to the block for export. This parameter is referred to as The *Maximum header Length* or MHL (see Section 4.1.1). The value of this parameter must be at least *one* (1). Its maximum value must be no larger then the physical address of the CE. To ensure transfer efficiency, when possible, the value of this parameter should be an even number of *cache-lines* (32 bytes).

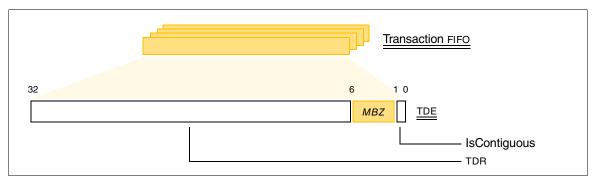

# 4.7.2 The PEB's Transaction FIFO

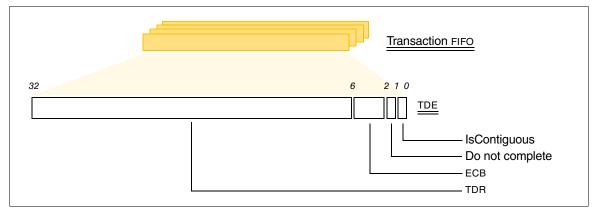

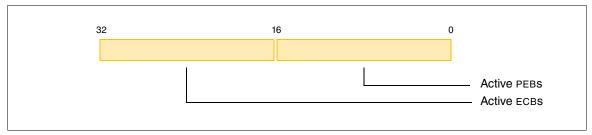

The PEB's transaction FIFO is also called the *pending export* FIFO. This is an *asynchronous* FIFO with the capacity to store up to 512 (decimal) entries. As implied by its name this FIFO buffers pending export transactions. An export transaction is initiated by a protocol driver, processed by the protocol core and completed by the PIB. The protocol driver writes to and the PIB reads from this FIFO. *What* is either inserted or removed from this FIFO is a 32-bit word called a Transfer Descriptor *Entry* (TDE). The structure of a TDE for the PEB is illustrated in Figure 20:

Figure 20 Structure of the TDE as used by the PEB

where:

- **IsContiguous:** This field specifies the in-memory relationship between the end of a packet's header and the beginning of its payload. If this field is true, (*set*) the PEB assumes the packet's header and payload are contiguous with respect to one another. In such a case, the PEB ignores the *Packet Payload* field of the corresponding Transfer Descriptor (see below and Section 4.2). If this field is false (*clear*), the PEB assumes the packet is *not* contiguous and that the location of the packet's payload is specified by the *Packet Payload* field of the corresponding Transfer Descriptor. This option is useful only when *both* the following constraints are present:

- The in-memory representation of the packet must be contiguous. Note: this is by definition and implication true, when the size of the payload is *zero* (see Section 4.2).

- The packet's payload boundary *cannot* be cache-line aligned as the packet header length is not evenly divisible by a cache-line (32 bytes).

In all other instances, this field should be *false*.

**Do not complete:** This field specifies, whenever a transaction completes *successfully*, whether the PEB posts a completion message to an ECB (see Section 4.8.2). The target of this completion message is determined by the value of the *ECB* field described below. If this field is true (*set*), the PEB will *not* post a completion message. If this field is false (*clear*), the PEB *always* post a completion message. This option is useful when export and import transactions are coupled. For example, consider the case of a command/response type protocol. In such a case, the reception of a response packet could be used to complete not only the export (command), but also its

paired import (response) transaction. In turn, this reduces the traffic through the ECBs of the system and the corresponding interrupts that traffic might generate. *Note*: The usage of this field is *only* applicable to successful transactions. If a transaction fails, the value of this field is ignored and a completion message is *always* posted to the specified ECB.

- **ECB:** A small enumeration which specifies the ECB (see Section 4.8) used to complete the transaction. These values were established when the ECBs of the CE were instantiated (see Section 4.1.4 and Section 4.8.1). Note: As failed transaction are *always* posted to an ECB, this field must contain a legitimate value independent of the value of the *Do not complete* field described above.

- **TDR:** A reference to the corresponding Transfer Descriptor (see Section 4.2). In actuality, the 26 most significant bits of the Transfer Descriptor's address as all Transfer Descriptors must be aligned on a *64-byte* boundary and therefore, the low-order six address bits are assumed *zero*.

# 4.7.3 Faults triggered by a Protocol Core

These faults occur in the interface between the protocol *core* and its corresponding PEB. In such a case, the TDE corresponding to the fault is not available to the PIC and therefore the TDE\_Fault\_Register (see Section 6.1.3) is simply *cleared*. See the description of the PEB's Front-End interface (Section 5.2.2) for more information.

#### 4.7.3.1 Data Pipeline Empty

The protocol core attempted to retrieve data from the block when the block had no data to deliver. Formally, this corresponds to the protocol core asserting the block's Advance\_Data\_Pipeline signal while its Data\_Available signal is *not* asserted.

#### 4.7.3.2 Status Pipeline Full

The protocol core completes a packet transfer and attempts to communicate completion status to the PEB. However, the PEB does not have sufficient buffering to accept that completion status. Most likely, the PEB is not able to pass off this completion status to the ECB specified in the transaction. Formally, this corresponds to the protocol core asserting the block's Advance\_Status\_Pipeline signal while its Status\_Full signal is asserted.

## 4.7.4 Faults triggered by a Protocol Driver

These faults occur in the interface between the protocol *driver* and its corresponding PEB. See the description of the PEB's Back-End interface (Section 6.1) for more information.

#### 4.7.4.1 Invalid Transfer Descriptor

The protocol driver posts a TDE to the block's transaction FIFO. The PEB fails to de-reference the Transaction Descriptor pointed to by that TDE. This fault could occur for a variety of reasons:

- The ECB number specified by the TDE exceeds the last ECB defined for the system.

- The TDR does not correspond to a a valid location in processor memory.

- The TCD address specified in the Transaction descriptor is neither 32-byte aligned nor corresponds to a valid location in processor memory.

#### 4.7.4.2 No such ECB

The protocol driver posts a TDE whose *ECB* field points to an ECB not instantiated in the CE.

#### 4.7.4.3 Export FIFO Full

The protocol driver posts a TDE to the block's transaction FIFO. The FIFO is *Full*.

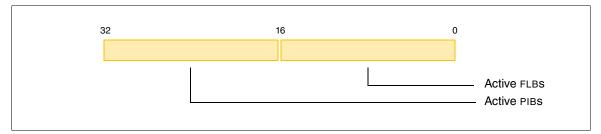

# 4.8 The Export Complete Block

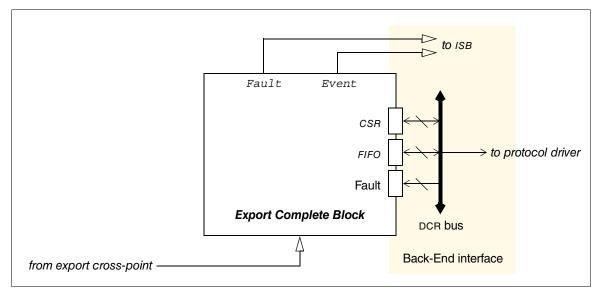

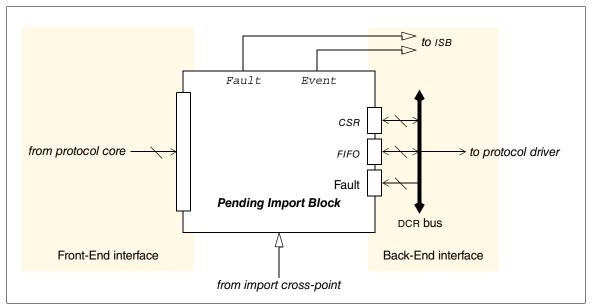

The Export Complete Block (PEB) is used to communicate completed export transactions from the PIC to a protocol driver. Therefore, the block's Front-end Interface is connected directly to the PIC's EMB (see Section 4.7) and is opaque to the user. As such, there is a close partnership between ECB and PEB (see Section 4.7). When a protocol engine completes the transfer of a packet it notifies its corresponding driver by calling on the services of the ECB's Front-End Interface. A driver "waits" on export completion by using the services of the ECB's Back-End Interface. A detailed discussion of the export transaction is found in Section 4.12. A block diagram of this interface is illustrated in Figure 21:

Figure 21 Block diagram of the ECB

The ECB does *not* have a Front-end Interface. Instead, as part of the PIC it is automatically connected to the export cross-point (see Section 4.1.4). This connection allows any of the instantiated PEBs of the CE to draw on the services of any of the instantiated blocks of this type.

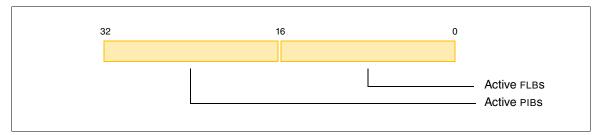

The Back-End Interface consists principally of an interface to the block's transaction FIFO. This FIFO buffers completed export requests. The FIFO's *read* port is connected to the processor's DCR bus. A protocol driver reads from this port to process completed transactions. The FIFO's corresponding *write* port is implicitly driven by one or more of the instantiated PEBs through the export cross-point.

The current condition of the transaction FIFO is used to drive the block's Event signal (see Section 4.5). When a block of this type is instantiated this signal as well as the Fault signal are automatically connected by the PIC to the ISB (see Section 4.11) and in this fashion FIFO conditions and/or the presence of a fault can used to trigger processor interrupts. The set of conditions which may assert the Event signal are configurable through the block's CSR register (see Section 6.2.1). This register is accessed through the DCR bus. A discussion of FIFO configuration is found in Section 4.11.

The specification for the Back-End Interface is found in Section 6.2.

The maximum number of ECBs which can be instantiated (consistent with the resources of the FPGA) can be no greater then sixteen (16).

#### 4.8.1 Parameters

When a block of this type is instantiated (see Section 4.1.4) various block attributes must be assigned. These include:

**Block number** This is a small enumeration from *zero* (0) to 15 (decimal) which is used to identify the instantiated block. If more then one block of this type is instantiated, each block must be assigned a unique number. This value is used to establish:

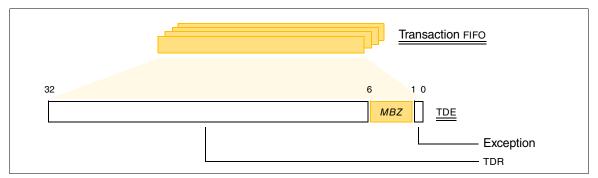

- The relative offset into DCR space for the registers of its Front-End Interface. See Section 1.3.1 for a discussion of how this identifier maps to an absolute address on the DCR bus.