# Using the RCE as an FEE Simulator

RCE Training Workshop

Martin Kocian, kocian@slac.stanford.edu

June 16, 2009

## Introduction

- For DAQ development it is important to test the system under realistic conditions.

- FE ASICS are often available only late in the game.

- It can be hard to get realistic data without collisions.

- To do a real test of the DAQ frontend simulators are crucial.

- The RCE can be used as a frontend simulator.

- This talk discusses how an RCE frontend simulator could be written.

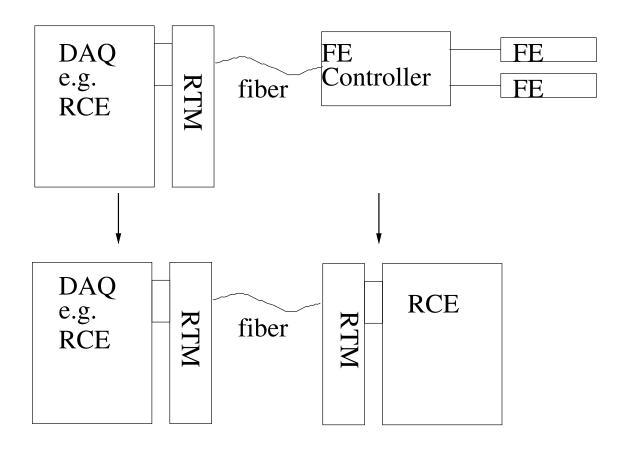

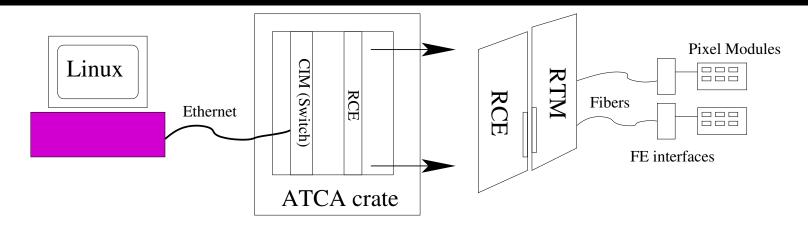

# Concept

- The DAQ talks to the frontends through optical fibers.

- Idea: Replace FE by RCE.

## Possibilities

- Simulate the ASIC behavior on the RCE in C++.

- Test frontend configuration.

- Test calibration software.

- Test data taking/trigger.

- Download data files to the RCE to be fed to the DAQ.

⇒ Emulate frontend behavior in real time.

#### Pixel FE with PGP

- Use Pixel FE with PGP from the previous session as an example on how one could design a frontend simulator.

- Elements:

- PGP RCDI interface.

- HSIO (FPGA interface board) simulation.

- Frontend simulation.

- A straightforward way to emulate the hardware's behavior would be to create classes that correspond to these elements.

## RCDI Interface

- Raw PGP is available through pgp driver on the RCE that emulates the frontend.

- Write a handler class RCDIslave that implements the functionality of the RCDI slave.

- To the DAQ RCE the FE RCE looks like the frontend vhdl RCDI slave.

- RCDI functionality:

- Register R/W.

- Command.

- Data.

# Software Implementation

- RCDI slave executes the master's register and command requests.

- Implementation could be done through callback functions:

```

writeRegister(address, value)

readRegister(address)

executeCommand(opcode)

```

- The user (in this case the class that implements the HSIO functionality) would implement the functions and register them with the RCDIslave.

- RCDI slave could send data to the master through a function sendData(buffer)

- The HSIO class could use this function.

- An official RCDI slave interface is to be written.

## **HSIO**

- In hardware the HSIO is a board with a Xilinx FPGA.

- Function:

- Receive data from RCE.

- Buffer it in a FIFO.

- Serialize it for the FE.

- Receive serial data from the FE.

- Send data to the RCE.

- Create an HSIO class with this functionality.

#### **HSIO** Class

- Implement writeRegister(...) function of RCDIslave to insert data into the buffer.

- Implement executeCommand(...) function of RCDIslave to send buffer to FE class.

- HSIO class calls RCDIslave's sendData(...) as handshaking like in the hardware implementation.

- To send data FE class calls a function in HSIO which then uses RCDIslave's sendData(...) to send data back to the master RCE.

#### FE Classes

- The implementation of the frontend classes depends on the ASIC to be simulated.

- Create classes that correspond to FE elements.

- In the pixel module there is 1 controller and 16 chips.

- Create configuration registers and emulate their functionality as needed.

- For the digital test presented in the previous session one would for example have to implement the pixel mask registers with their functionality.

- Return data on L1A. The data could come from file or be simulated in the FE classes.

- For the digital test the relevant data is basically just a "1" if the pixel fired.

#### FE Parser

- RCDI and HSIO do not know what the configuration and event data means.

- It is the FE controller and the 16 FE chips on the pixel module that parse the incoming bitstream and translate it into register settings.

- Write a parser class to decode the incoming configuration data and set the registers in the frontend classes accordingly.

## Data Encoder

- Collect data from the frontend classes.

- Encode the data into a bitstream.

- Transfer the bitstream buffer to the HSIO class.

- The data can be read into the slave RCE through ethernet or from nfs.

# A Real Example

- At SLAC we want to do a realistic test of the data transmission for the insertable B layer.

- We are building an electrical prototype for one halfstave.

- 16 chips.

- Data readout at 160 Mbits/s.

- Configuration and clock at 40 Mbits/s.

- In order to measure transmission quality and cross-talk we have to run 16 readout chains in parallel.

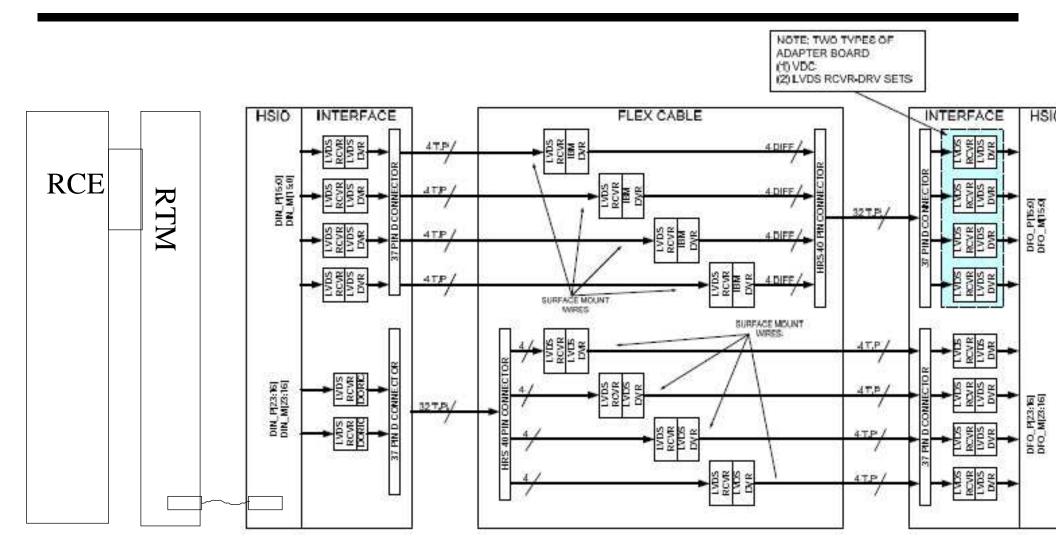

## **IBL** Transmission Test

Drawing: Dave Nelson

• Data transmission test for the insertable B layer.

# Design

- 16 serializers and deserializers on the HSIO.

- HSIO connects to the stave through a custom interface board.

- Upload data from RCE to HSIO via PGP.

- Control serializers via PGP.

- Download transmission results to the RCE through PGP.

# Summary

- The RCE can be used as a frontend simulator.

- Capability to send simulated data to the DAQ at Gbit/s rates.

- Data could be uploaded via ethernet.

- C++ classes emulate hardware components.

- At SLAC we will use the RCE for frontend simulation for the IBL.