# The Bonn ATLAS Telescope

Johannes Treis October 29, 2001

Artist's view of a beam telescope

#### Abstract

A detailed description of the Bonn ATLAS Telescope (BAT) system including software and hardware is given. The BAT is a reference instrument for charged particle tracking. With its four modules, each containing a double sided silicon strip detector, the BAT provides a quadruple of space points used for trace reconstruction of a charged particle.

In contrast to existing telescope systems, the BAT is designed for fully PC-based operation. On-board digitization of analog data and intelligent data preprocessing logic are integrated in each module to perform on-board hit detection and zero suppression. Thus, the system can process an event rate about 15 times larger than the event rate achieved with common VME-based systems.

The BAT can support almost any kind of DUT. The benefits of the BAT, namely high readout speed and data preprocessing, can be carried over to the DUT via a specific interface. Additionally, the system is optimized for low noise operation and the relatively low beam energies provided by the ELSA testbeam facility in Bonn.

Integration of VME components into the BAT readout is possible. Moreover, an interface for VME based operation of the entire telescope system exists.

CONTENTS

## Contents

| 1 | Introduction                                                                                                                                                                                                                                                                                                                                                        | 1                                                  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2 | System overview                                                                                                                                                                                                                                                                                                                                                     | 4                                                  |

| 3 | <u>.</u>                                                                                                                                                                                                                                                                                                                                                            | 8<br>8<br>13<br>16                                 |

| 4 | 4.1 The modules' case                                                                                                                                                                                                                                                                                                                                               | 17<br>17<br>23                                     |

| 5 | 5.1 The VA 2 IC                                                                                                                                                                                                                                                                                                                                                     | 28<br>28<br>32                                     |

| 6 | 6.1 Parameter overview                                                                                                                                                                                                                                                                                                                                              | <b>36</b><br>36<br>38                              |

| 7 | 7.1 PCB features 7.2 The interface FPGA 7.2.1 The central mode address register (CMA) 7.2.2 The first mode decoder (MD1) 7.2.3 The interrupt status register (ISR) 7.2.4 The main FPGA configuration register (COR)                                                                                                                                                 | 41<br>45<br>45<br>46<br>46                         |

|   | 7.3.1 Second mode decoder (MD2) 7.3.2 First command register (CMD I) 7.3.3 Second command register (CMD II) 7.3.4 The RAM access block (RAC) 7.3.5 The status bus readback block (STA) 7.3.6 The software sequencer (SOSE) 7.3.7 The main sequencer (MSQ) 7.3.8 The data preprocessor (DPR) 7.3.9 The shutdown state machine (SSM) and the interrupt control (IRQC) | 49<br>50<br>52<br>53<br>56<br>57<br>59<br>61<br>65 |

|   | 7.3.10 The FIFO control (FICO)                                                                                                                                                                                                                                                                                                                                      | 86                                                 |

CONTENTS

|    |      | 7.3.11 The IO blocks (IOB)                    |

|----|------|-----------------------------------------------|

|    | 7.4  | The module's FIFO                             |

|    | 7.5  | The module's RAM                              |

| 8  | The  | ATC 99                                        |

|    | 8.1  | PCB features                                  |

|    | 8.2  | Hybrid voltage supplies (SVH)                 |

|    | 8.3  | Hybrid bias generation (HB)                   |

|    | 8.4  | Detector bias voltage handling (HV)           |

|    | 8.5  | Signal level shifters (LS)                    |

|    | 8.6  | Current-to-voltage converters (I2UC)          |

|    | 8.7  | Fast digitization of analog output data (DGS) |

|    | 8.8  | Data output multiplexer (DOM)                 |

|    | 8.9  | The calibration chopper (CAC)                 |

|    | 8.10 | Monitoring circuits (MOC)                     |

|    |      | The clock control (CLC)                       |

|    |      |                                               |

| 9  | Pow  | rer supplies 127                              |

| 10 | The  | TLU 130                                       |

|    |      | PCB features                                  |

|    |      | Principle of operation                        |

|    |      | Implementation                                |

|    | 10.0 | 10.3.1 Mode addresses                         |

|    | 10 4 | The CMD register                              |

|    |      | The TLU mask register (TMR)                   |

|    | 10.0 | 10.5.1 TLU interrupts                         |

|    |      | 10.0.1 1E0 Intellapts                         |

| 11 |      | ware issues 145                               |

|    |      | General structure                             |

|    | 11.2 | The producer (PDC)                            |

|    |      | 11.2.1 Compatibility                          |

|    |      | 11.2.2 Graphical user interface               |

|    |      | 11.2.3 Module administration                  |

|    |      | 11.2.4 Run startup and shutdown               |

|    |      | 11.2.5 The interrupt thread (IT)              |

|    | 11.3 | Shared buffers                                |

|    |      | 11.3.1 Concept                                |

|    |      | I                                             |

|    |      | 11.3.2 Events                                 |

|    | 11.4 |                                               |

| CONTENTS | V |

|----------|---|

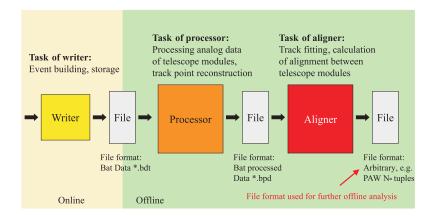

|              | 11.6 Further processing       | . 162 |

|--------------|-------------------------------|-------|

| 12           | Outlook                       | 164   |

| $\mathbf{A}$ | Additional documentation      | 167   |

| В            | Modifications to the ATC card | 168   |

# List of Figures

|   | 1  | Concept of a particle tracker                                 | 2 |

|---|----|---------------------------------------------------------------|---|

|   | 2  | Schematic overview about the BAT setup                        | 4 |

| , | 3  | BAT module interconnection using the BB                       | 5 |

| 4 | 4  | How to include a VME based DUT                                | 6 |

|   | 5  | How to include a BB based DUT                                 | 6 |

| ( | 6  | Setup of a BB based DUT                                       | 7 |

| , | 7  | Picture of the BB-PCI interface card                          | 8 |

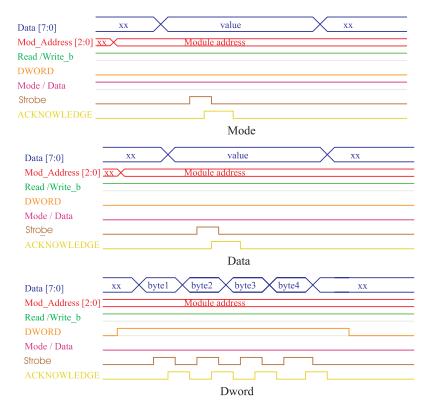

| ć | 8  | Signal timing for the BB write accesses                       | 2 |

| ( | 9  | Signal timing for the BB read accesses                        | 3 |

|   | 10 | Setup for VME based operation of the BB                       | 6 |

|   | 11 | Schematic of a BAT module setup                               | 8 |

|   | 12 | Drawings of the module's frame                                | 9 |

|   | 13 | Schematic back side view of a module                          | 9 |

|   | 14 | Photography of a module's back side holding the connectors 20 | 0 |

|   | 15 | Photography of a fully covered module                         | 2 |

|   | 16 | Testbeam setup at E3                                          | 2 |

|   | 17 | Schematic drawing of a fully mounted hybrid assembly 2        | 4 |

|   | 18 | How to assemble a hybrid assembly                             | 6 |

|   | 19 | A view of a module's DETC                                     | 7 |

|   | 20 | Schematic of a single VA 2 channel                            | 9 |

|   | 21 | Hold timing of the VA 2 IC                                    | 1 |

|   | 22 | Readout sequence of a VA 2 IC                                 | 2 |

|   | 23 | Photography and schematic view of a BELLE VA 2 hybrid 3       | 3 |

|   | 24 | Full schematic of the VA hybrid                               | 5 |

|   | 25 | Overview about detector readout portion                       | 7 |

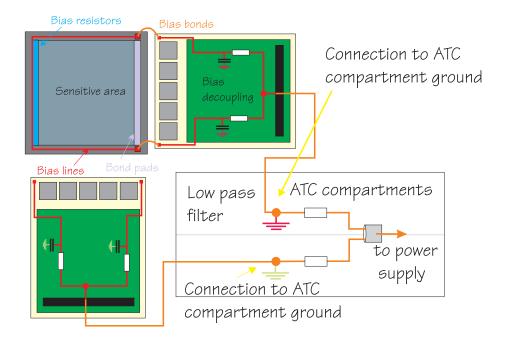

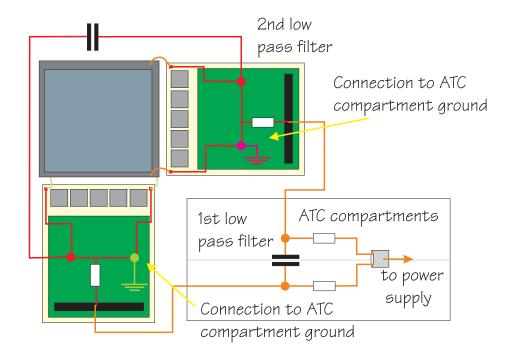

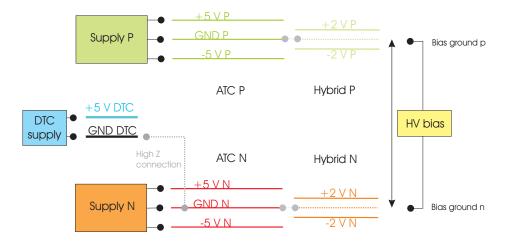

|   | 26 | ATC prototype detector biasing scheme                         | 9 |

|   | 27 | Final ATC detector biasing scheme 4                           | 0 |

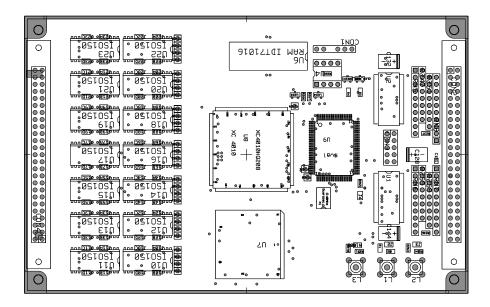

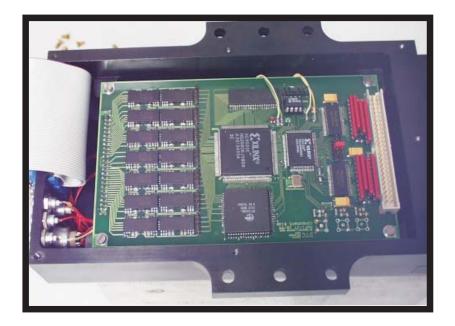

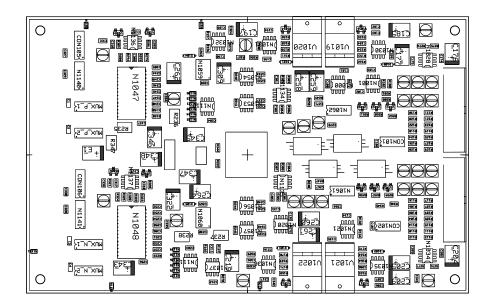

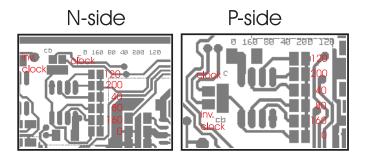

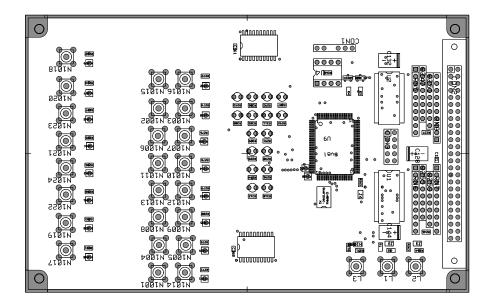

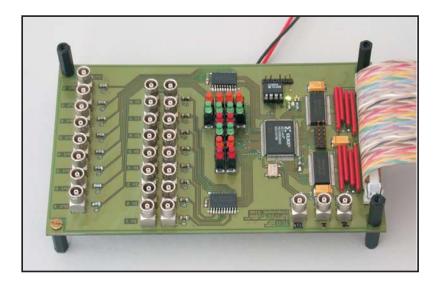

|   | 28 | Layout view of the DTC card                                   | 2 |

|   | 29 | Photo of the DTC card                                         | 2 |

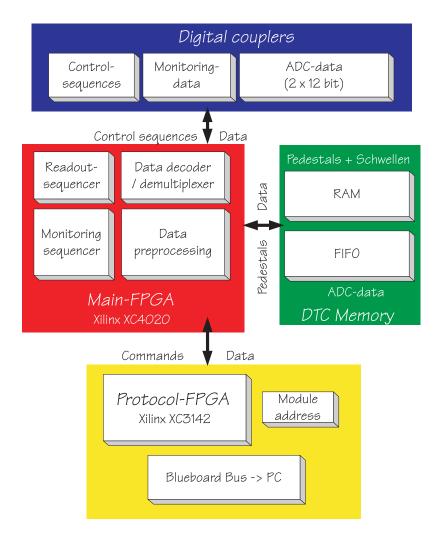

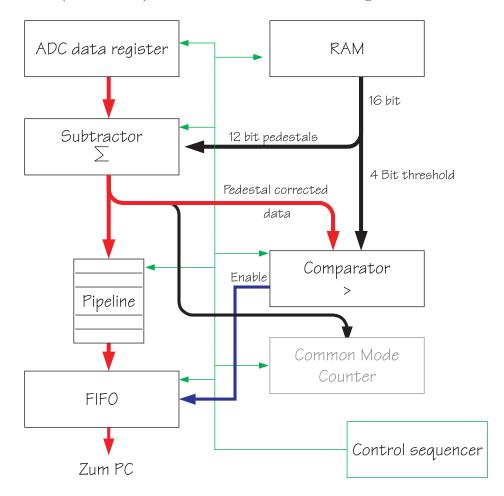

| , | 30 | Functional building blocks of the DTC                         | 3 |

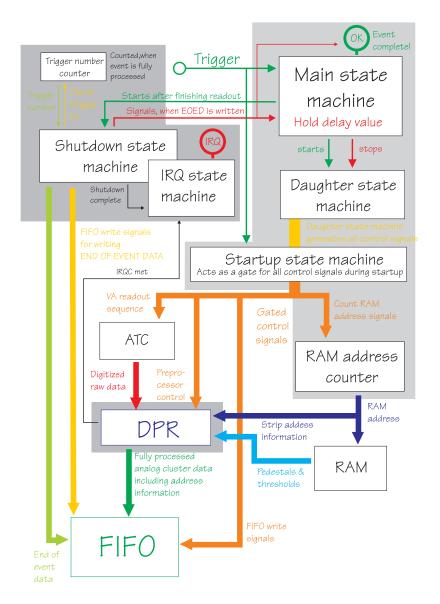

| , | 31 | Overview about the MSQ in the MFPGA 6                         | 3 |

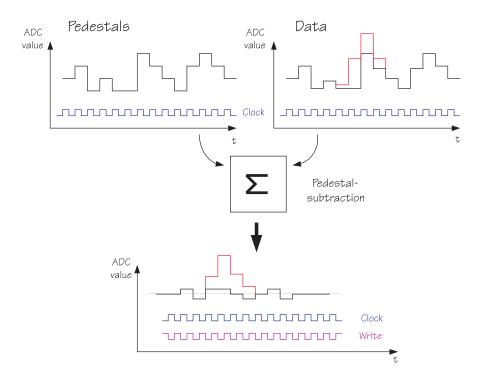

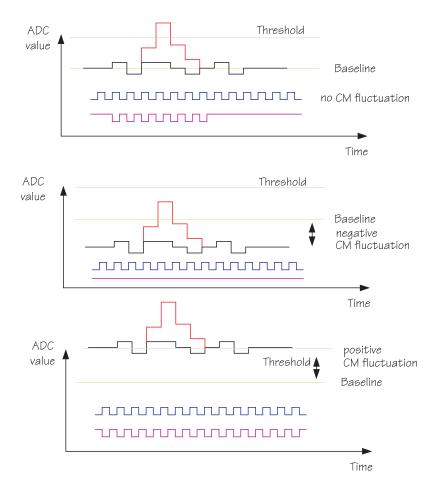

| , | 32 | The principle of pedestal subtraction 6                       | 6 |

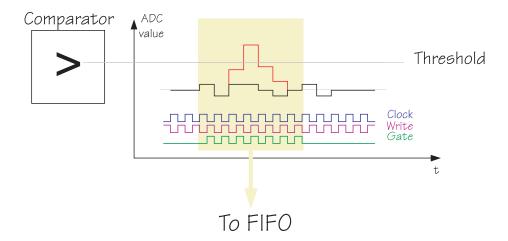

| , | 33 | Principles of hit detection and zero suppression 6            | 7 |

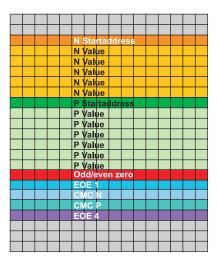

| , | 34 | Comparison between compressed and non-compressed data         |   |

|   |    | output format                                                 | 0 |

| , | 35 | Flow chart of the data preprocessing                          | 1 |

| , | 36 | Common mode fluctuations                                      | 6 |

| , | 37 | Example for an odd-even zero event                            | 0 |

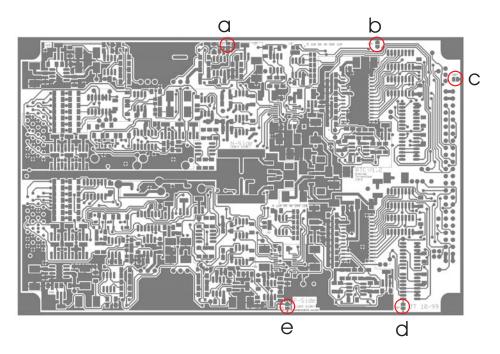

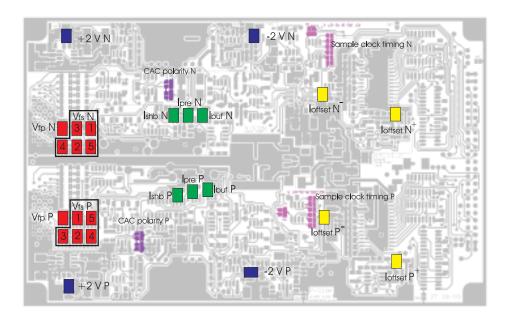

| , | 38 | ATC layout view showing component locations                   | 0 |

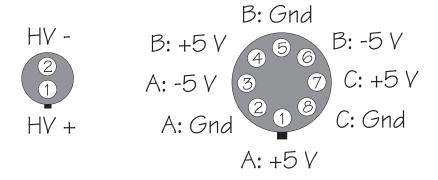

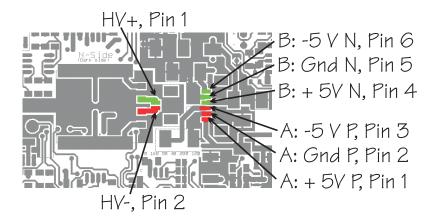

| 39 | Photo of an ATC view inside a module setup 100                       |

|----|----------------------------------------------------------------------|

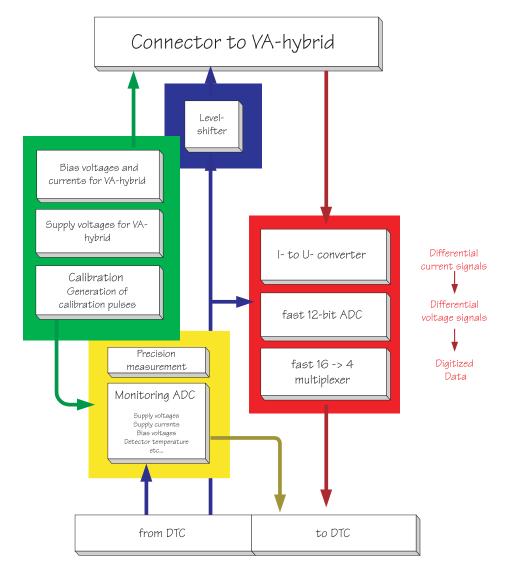

| 40 | Simplified flow diagram of one ATC compartment 101                   |

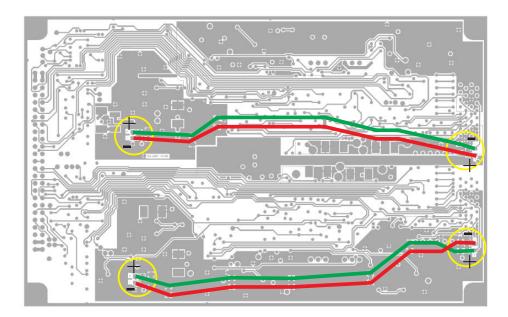

| 41 | Adding the ATC analog signal lines                                   |

| 42 | Assignment of ATC grounding pins                                     |

| 43 | Potential levels in telescope module                                 |

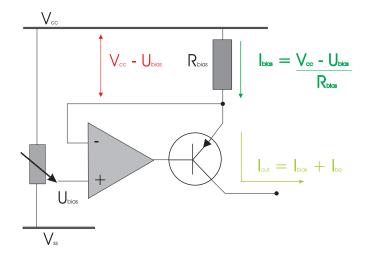

| 44 | Schematic of a bias current source                                   |

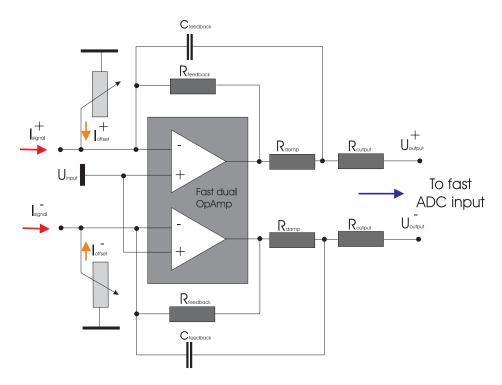

| 45 | Circuit schematics for the I2U converter circuit                     |

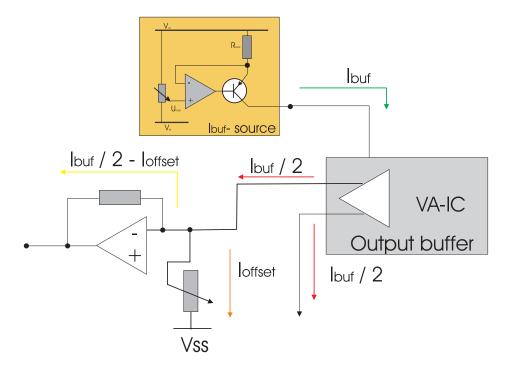

| 46 | Buffer bias current flow                                             |

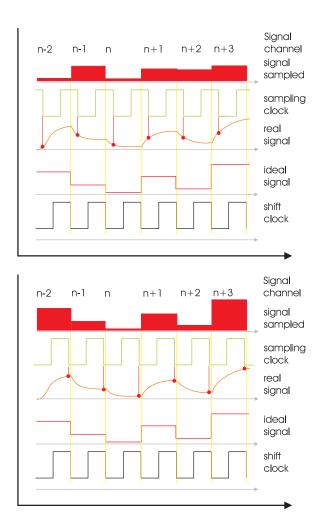

| 47 | Timing of telescope shift and sampling clock on ATC 117              |

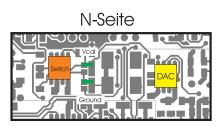

| 48 | Jumpers for clock control                                            |

| 49 | Location of all jumpers, bias and offset potentiometers on the       |

|    | ATC card                                                             |

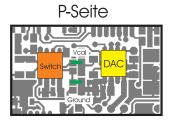

| 50 | Calibration chopper layout showing the polarity jumper settings. 121 |

| 51 | Photo of a module's power supply                                     |

| 52 | Assignment of power supply output pins                               |

| 53 | Connection between power supply and ATC                              |

| 54 | Rear view of a module's power supply                                 |

| 55 | Layout view of the TLU card                                          |

| 56 | Photo of the TLU card                                                |

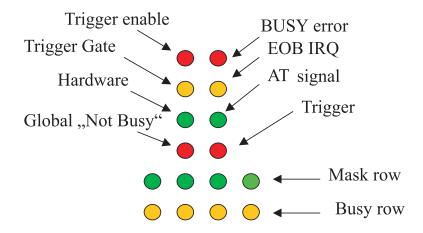

| 57 | Order and assignment of indicator LEDs on the TLU 133                |

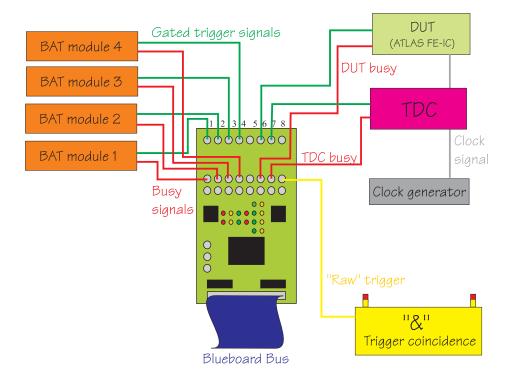

| 58 | Connection example for the TLU                                       |

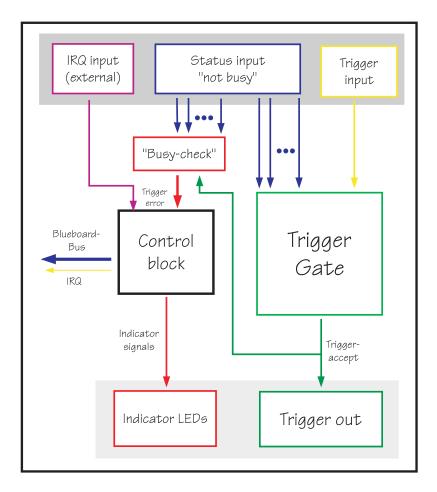

| 59 | Block diagram of TLU CFPGA implementation                            |

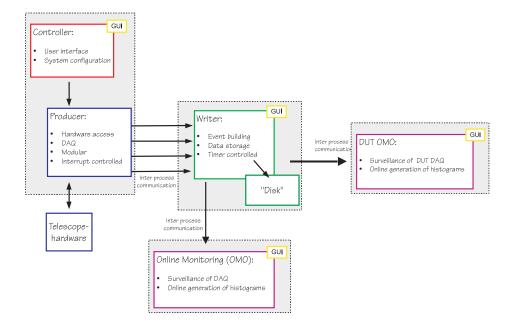

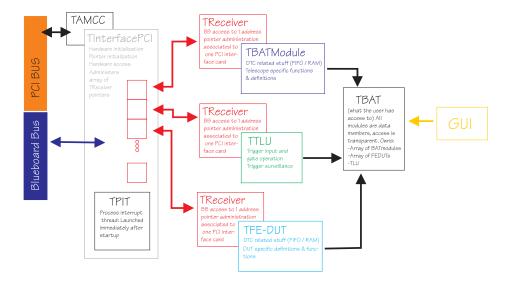

| 60 | Structure of the BATDAQ software package 146                         |

| 61 | Class hierarchy of the producer core                                 |

| 62 | Autonomous IRQ DAQ structure                                         |

| 63 | Single event DAQ structure                                           |

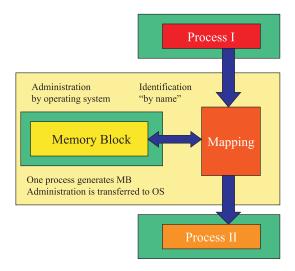

| 64 | Shared buffer concept                                                |

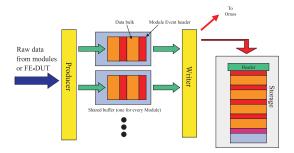

| 65 | Structure of stored data                                             |

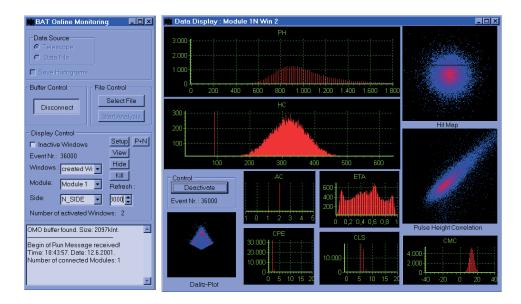

| 66 | Screenshot of the BAT OMO process                                    |

| 67 | Flow chart of general purpose offline analysis                       |

| 68 | BAT inside the testbeam area                                         |

| 69 | Modifications to be made to the ATC card 168                         |

|    |                                                                      |

LIST OF TABLES VIII

## List of Tables

| 1  | List of BB module types defined so far                        |

|----|---------------------------------------------------------------|

| 2  | Overview about BB accesses                                    |

| 3  | Overview about the parameters of the VA 2 IC 28               |

| 4  | Bias voltages and currents needed by the VA 2 IC 30           |

| 5  | Overview about the detector parameters                        |

| 6  | Example for RAM contents                                      |

| 7  | Overview about DPR operation modes                            |

| 8  | Overiew over the different IRQ rates 81                       |

| 9  | Structure of a DWORD                                          |

| 10 | IFPGA communications. Pin assignments 89                      |

| 11 | Pin assignment for FIFO part I: Data busses 91                |

| 12 | Pin assignment for FIFO part II: Control signals 92           |

| 13 | Pin assignment for RAM part I: Data / address bus 93          |

| 14 | Pin assignment for RAM part II: Control signals 94            |

| 15 | ATC I/O pin assignment part I: N-compartment 94               |

| 16 | ATC I/O pin assignment part II: P-compartment 95              |

| 17 | Overview over the different bias current sources              |

| 18 | Assignment of ATC output bits to output channels 119          |

| 19 | Assignment of ATC output bits to multiplexer control bit com- |

|    | binations                                                     |

| 20 | Assignment of ATC output data to data bus bits                |

| 21 | Assignment of ATC clock modes to control bit patterns 126     |

| 22 | Specifications of power supply NTBONN4                        |

|    |                                                               |

### 1 Introduction

When developing detector systems for ionizing radiation, testing a new device under conditions very similar to the experiment is a common problem. As far as high energy physics is concerned, the opportunity to undertake these tests is offered by testbeam facilities, which create an environment very similar to the surrounding of a high energy physics experiment. Such a testbeam facility is usually located close to a larger accelerator, extracts parts of the intensity of the main (primary) beam and converts it into a secondary beam some of whose properties, e.g. particle contents, intensity and particle energy, are well-defined.

However, when examining the characteristics of position sensitive detectors<sup>1</sup> properties of the secondary beam are not as well-known as the experimentalist would like them to be. Although a testbeam facility usually offers a variety of possibilities to steer the beam and influence the beam profile, the special kind of information which is important for this kind of test is usually not provided. The testbeam is not a continuous beam, of course, but consists of a stream of high energy particles. The passing of a single beam particle through the detector which is to be tested<sup>2</sup> is called an *event*. What is needed now is an information which allows a comparison between the event data acquired from the DUT and the "event reality". The "event reality" is the *penetration point*, the point, where in this event the particle crossed the sensitive area of the DUT and its angle of incidence. As this information is not provided by the testbeam facility, it has to be obtained elsewhere, and at this point a beam telescope enters the stage.

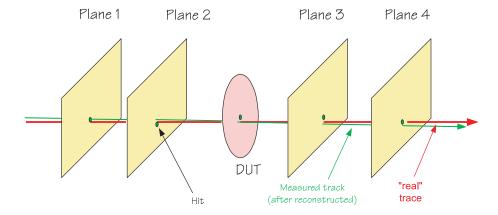

A beam telescope is a detector system which can measure the *track* of an incident ionizing particle, that is, the exact position and angle with respect to a plane of reference <sup>3</sup>, with some accuracy. From this data the penetration point on the DUT and its error can easily be calculated if the position of the DUT with respect to the POR is known. Figure 1 shows the concept of such a particle tracking detector.

Although this is the primary task of a beam telescope system, there are other requirements which arise e.g. from the fact that the error on the track measurement, and therefore on the penetration point forecast, has to be as small as possible, that the event rate, which is the number of events which can be processed, has to be high and, of course, that the system has to be

<sup>&</sup>lt;sup>1</sup>Especially their spatial resolution is what physicists are interested in here.

$<sup>^{2}</sup>$ The sensor and / or the detector system whose properties are to be determined is in the following referred to as device under test, abbr. DUT.

<sup>&</sup>lt;sup>3</sup>This plane of reference is in the following referred to as *POR*.

Figure 1: Concept of a particle tracker consisting of a number of discrete detector planes. The passing particle generates a signal in each plane, which allows the reconstruction of the penetration point with some accuracy. Evaluating the data from all detector planes, the particle track can be obtained with a simple linear regression. Of course, the position of the detector planes with respect to each other (alignment) has to be known as precise as possible. The error for this interpolated track corresponds to the error of the regression. If the alignment of the DUT with respect to the telescope is known, the DUT data and the interpolated track based on telescope data can be compared.

efficient, robust and easy to operate. In the following, some of the demands on such a telescope system are listed:

- The beam telescope itself has to influence the beam in the slightest possible way. So, the track of the incident particle can be measured as precisely as possible, and the penetration point can be predicted as accurate as possible. Influence on the beam can occur e.g. due to coulomb multiple scattering at the atoms of the material of which the telescope consists, so it is a good idea to put as little material into the beamline as possible<sup>4</sup> and to use material with low atom number to lower the cross section for multiple scattering to the lowest possible value.

- For a detailed analysis of sensor properties a lot of statistics is needed. Especially in case of semiconductor sensors, with pixel sizes at the order of 250 square microns or even smaller, it takes a long time to collect enough statistics to be able to characterize the properties of every single pixel cell in a satisfying way. The time it takes to collect this amount

$<sup>^4</sup>$ This is the reason why people say that they would favor a telescope "that isn't there at all".

3

of data depends on the readout speed of the DUT and the telescope on one side and on the beam intensity on the other. So the resulting demand to the telescope system is to allow an event rate that high that the only limit is given either by the DUT readout or the beam intensity. If this demand cannot be met, the telescope readout should at least be as fast as possible.

- One of the important parameters developers are interested in is the DUT efficiency. The detector efficiency is the fraction of events, in which the DUT was able to detect the incident particle. To measure the efficiency, one has to determine the real number of particles passing the DUT and this is only possible if the reference counter used (i.e. the telescope) is ideally 100% efficient, but at least much more efficient than the DUT.

- As the demands to as well software as hardware of the telescope system can be very different depending on which kind of DUT is to be examined, a multi-purpose-system has to offer a flexible, well-defined hardware and software interface for connecting a DUT to the system and including it in the readout chain. Besides, a possibility to connect the system to standard electronic components used for measurement and data acquisition in high energy physics (e.g. VME modules) should also be provided.

- As such a system will be used many times by many different people, the system has to be robust, easy to handle and easy to operate. The setup needed for such a system has to be as simple as possible to avoid problems in preparing the measurements. The system may travel to a lot of different testbeam facilities, so the equipment needed for full operation should be reduced to the minimum to preserve mobility.

Of course, this list is not complete. The Bonn ATLAS telescope was designed to meet most of these requirements, and where the requirements were not met, the performance compared to older systems was significantly improved.

## 2 System overview

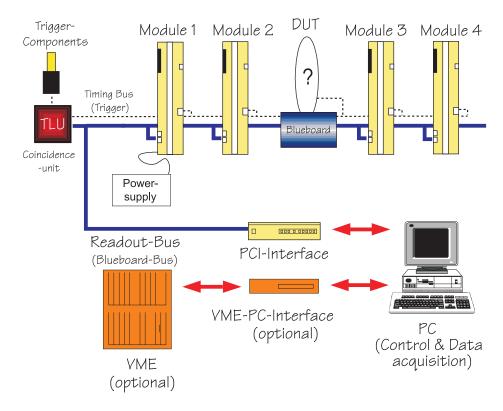

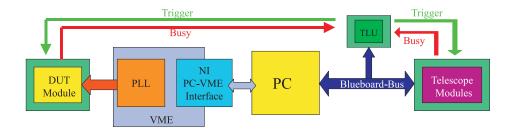

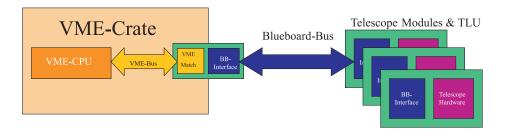

Figure 2: Schematic overview about the BAT setup. The PC controls the whole system. The blueboard bus only transfers digital data and commands. Each module and DUT has its own power supply. The connection between PC and VME is made via a commercial PC-VME interface. This is only needed if VME components are to be included into the readout chain.

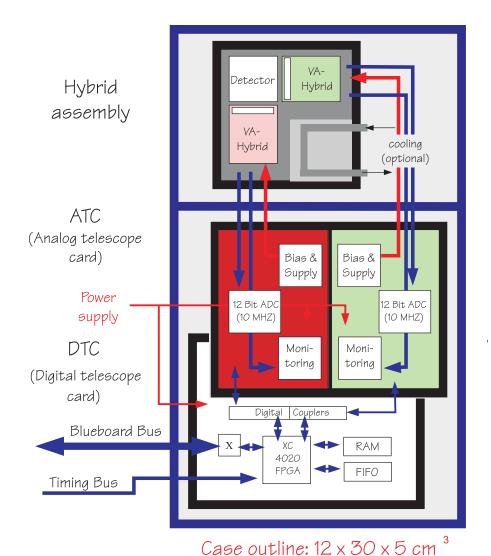

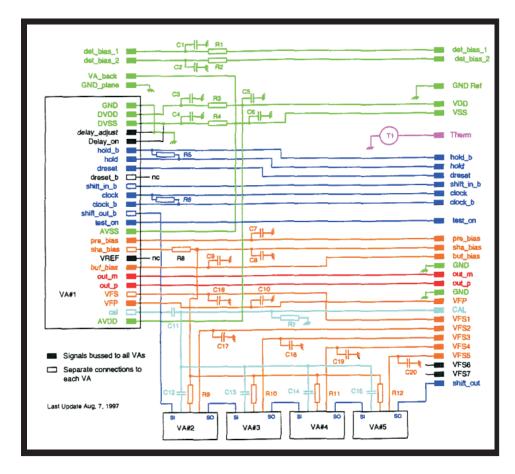

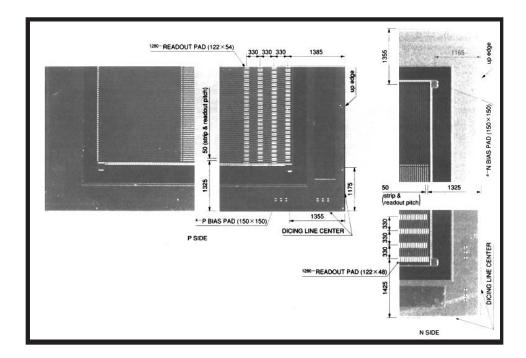

An overview about the whole BAT system is shown in fig. 2 The BAT consists of four planes of double sided silicon strip detectors each providing 640 channels / side. Each plane is read out by VA 2 ICs provided by IDE AS, Oslo. Directly connected to the front end ICs are complete analog and digital signal processing circuits enabling signal digitization and data preprocessing. Detector, front-end electronics and signal processing and digitization logic are mounted in a solid aluminum case. This is what is called a BAT module. Each module has its own power supply. It provides not only the supply voltages for the analog and digital circuits inside the module, but also the high voltage detector bias.

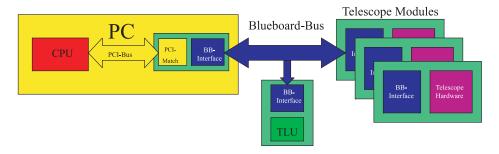

The system is fully PC based. The whole control, data acquisition and data storage software runs on a PC operating under windows NT / 9x OS. The connection to the hardware is made via the BB-PCI interface card provided

by Silicon Solutions. The BB, the Blueboard Bus, is a proprietary bus standard. All modules are connected to one another and the DAQ PC over this BB. The BB connections are shown in figure 3.

The BB is purely digital. Only digital signals and commands are exchanged between the PC and the connected modules. Thus, there is no need to transmit analog signals over long cables to external (e.g. VME) ADCs<sup>5</sup>, which improves the system's setup as well as the system's analog performance.

The trigger for the system has to be provided externally, e.g. by a trigger scintillator coincidence. This trigger signal is not to be fed directly into the BAT modules. Another module connected to the BB, the TLU (trigger logic unit), serves as trigger fan-out and as trigger controlling stage. For, if properly configured, the modules act completely independent from any external sequencer logic, such a stage is needed to enforce synchronous triggers and do a controlled start and end of run. The modules themselves receive and process the trigger. The data obtained in this way is stored in the moduleinternal memory blocks (FIFO). The module itself sends an IRQ either if one event has been successfully processed (event interrupt) or if a certain amount of data gathered in the modules FIFO (data interrupt, buffered mode). For various reasons, the buffered mode is much faster than the event IRQ mode. All that remains to the DAQ software is to read back the data from the modules, assemble them to complete events and store them somewhere. A part of the data acquired in this way can be used to display online monitoring histograms, which show the systems actual performance and allow the user to check if everything is going well.

The system offers two ways to connect devices under test (DUTs). VME based devices for example can be connected using a common VME-PC interface. This has been successfully done for several testbeam periods the BAT

<sup>&</sup>lt;sup>5</sup>This is done in most of the telescope systems currently used.

Figure 3: BAT module interconnection using the BB. The modules are all tied daisy chained to the same bus cable. The TLU has to be last module on the bus.

**Figure 4:** How to include a VME based DUT. Access to the VME resources is gained with e.g. a common PC-VME interface. Problems arise if the VME module is not capable of data buffering or IRQ generation.

was used in. The problem here is, that it is difficult to hand an IRQ on the VME bus directly to the CPU (at least for the VME-PC interfaces commonly used). So, an event-by-event readback has to be made, which significantly lowers the system's performance in speed<sup>6</sup>. The setup necessary is shown in figure 4.

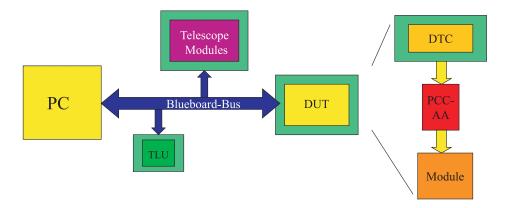

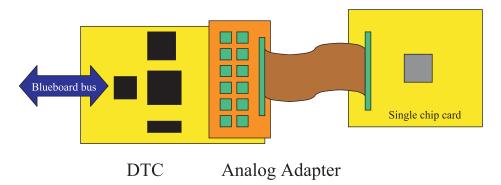

The other possibility is to connect the DUT module directly to the BB. Here, the digital logic of a BAT module (DTC) can be used as a ready-to-go, easy-to-handle interface, in which with little effort concerning FPGA programming the readout functions for the DUT can be implemented. This setup is shown in figure 5. Sometimes an analog interface card has to be made, which provides supply and bias voltages to the DUT (thus replacing the BAT analog circuits). But the great advantage is that the module created in this way can easily be integrated on the BB and in the readout

<sup>&</sup>lt;sup>6</sup>But even in this case, the performance improves compared to common systems.

**Figure 5:** How to include a BB based DUT. The module is simply tied to the BB as well. If e.g. the DTC card is used as interface to the BB, the insertion of the module to the software will be easy as well.

software. It also supports data buffering and IRQs, so the system's high speed capabilities can fully be used. This setup is shown in fig. 6.

**Figure 6:** Setup of a BB based DUT using the BAT DTC as interface to the BB. The analog adapter replaces the ATC card used in the BAT modules. This is the easiest way to include DUTs, also from the software point of view.

### 3 The Blueboard bus

All BAT modules, the TLU and sometimes also DUTs are connected to the DAQ PC via the Blueboard Bus (BB). This is a proprietary bus standard which has been developed by Silicon Solutions, a small company from Cologne. It has some similarities to SCSI, transferring differential signals over long distances with great reliability. The BB also offers flexible functions for system configuration, system administration and IRQ handling. The BB software package provided by Silicon Solutions contains debugging tools, device drivers and software libraries which offer a very transparent and easy-to-operate software interface for the operation of any kind of module. The hardware interface is also well-defined and can be adapted to the users needs with little or even no hardware effort, depending on the users requirements. In the following, the BB basics are described as far as it is necessary to understand telescope operation.

#### 3.1 BB basics.

The BB is designed to be operated from a PC platform with a PCI bus. The connection to the BB is made via the BB-PCI interface card. This card contains a Xilinx XC 3142 FPGA, which in the following be referred to as BB FPGA, and an AMCC PCI matchmaker IC. The BB FPGA has controls the interface and timing to the BB, the AMCC controls all PCI access functions. An image of the BB-PCI interface card is shown in fig. 7. The BB itself is connected to this card using 50 pol. Centronics standard connectors. The modules can either be connected using standard IDC connectors, or, if some

**Figure 7:** Picture of the BB-PCI interface card. A free standard PCI slot is needed for the installation. Supported OS are windows 95 / 98 and windows NT 4.0. Drivers for windows 2000 are not yet available.

effort is made to design a case for the modules (e.g. for the BAT modules), some customized connectors can be used<sup>7</sup>. The bus itself is made up from 50 pol. twisted pair flat ribbon cable<sup>8</sup>.

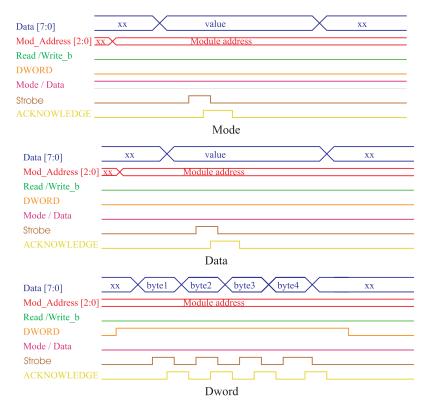

The BB consists of a bidirectional 8 bit data bus, a 3 bit address bus and several command and control signals. The most important of these signals are:

- Mode / Data (M/D)

- Read / Write (R/W)

- DWORD

- Strobe (STR)

- Acknowledge (ACK)

The data bus is either driven by the busmaster during a write access, displaying the data which is to be written, or by the accessed module during a read access, displaying the data the module has stored in its selected register. The 3 bit module address bus is controlled by the busmaster and shows the address of the module which is currently going to be accessed. The R/W line decides whether the next access will write into a register in the destination module or if a value is to be read from it. The BB supports two kinds of accesses: byte accesses transferring 8 bit each, and DWORD accesses transferring 32 bit in 4 packages of 8 bit each. The DWORD line shows which kind of access is currently performed. A byte access can occur either to the central mode address register of a connected module, selecting a register which is to be accessed next (this is a mode access), or to the selected register itself (this is a data access). The M/D line decides whether the mode address register or the register selected with the mode address register value is to be accessed. As the mode address register is usually only 8 bit wide, there is no such thing as a MODE-DWORD access. A strobe is sent during a write data access to make the accessed module accept the data currently valid on the data bus. During a read access a strobe is also sent by the busmaster, but in this case it is used to make the accessed module put the data of its selected register on the data bus. If this process is finished, the module sends an ACK signal, which indicates the busmaster, that the data currently valid on the bus is the data which is to be read back. The BB-PCI card is the only businester on the BB. It has the BB address 0 per default. As there are 7

<sup>&</sup>lt;sup>7</sup>For the BAT modules we decided to use the Centronics standard connectors.

<sup>&</sup>lt;sup>8</sup>Twisted pair is necessary because the BB transmits differential signals.

BB addresses left, up to 7 devices can be connected to the BB. In case this is not enough, more BB PCI interface card can be added to the system, if there is an appropriate number of free PCI slots. This feature has not been used for the BAT.

As described above, there are 6 different kinds of accesses to the BB:

- 1. Write mode

- 2. Write data

- 3. Read mode

- 4. Read data

- 5. Write DWORD

- 6. Read DWORD

Each of these accesses can be performed to each module connected to the BB. The connection on software side is made via the C++ software units provided by Silicon Solutions. At startup the software automatically initializes the interface hardware. Afterwards, the software scans the entire BB address range (from 0 to 7) to find out if there are modules connected to the BB and which kind of module it is. This is done by attempting to read the implementation ID, which can be done by doing a read data to MA  $0^9$ . If for a certain BB address no module is connected, there won't be an ACK signal indicating valid data on the bus, so the software knows that there is no module connected to the bus bearing this address. If a module is connected, a read access to MA 0 will yield not only an ACK answer to the strobe, but also an implementation ID. The 3 MSBs indicate the type of the connected module (there are different kinds of them), the 5 LSBs contain the firmware revision number. Module types defined so far are listed in table 1. Additionally, the figures 8 and 9 give an overview about the access timings for the different access types.

After detecting a module of a certain kind, the rest of the software is told, that a module of a certain kind exist, thus controls, windows and stuff can be prepared correctly. Additionally, certain pointers are prepared, one for each possible BB access, which, due to memory mapping, allow an access to the BB PCI interface, enabling the user to perform a certain access by simply accessing the address given in a certain pointer for this module. The

<sup>&</sup>lt;sup>9</sup>Per convention, this has to be the MA for the ID readback in all IFPGAs.

| Module type | ID |                                                                               |

|-------------|----|-------------------------------------------------------------------------------|

| PCI CARD    | 0  | The BB PCI interface itself.                                                  |

| PCI REC     | 1  | The BAT module DTC implementa-                                                |

| TECTROADD   | 2  | tion.                                                                         |

| TESTBOARD   | 2  | The standard Silicon Solutions test-<br>board. May be used as a DUT interface |

|             |    | to the BB sometimes.                                                          |

| TLU         | 4  | Trigger logic unit. Trigger controlling                                       |

|             |    | stage for telescope operation.                                                |

| FE-DUT      | 5  | Example for DUT integration. Based                                            |

|             |    | on the DTC firmware. Allows integra-                                          |

|             |    | tion of an ATLAS single chip into the                                         |

|             |    | telescope environment.                                                        |

| SPECIAL     | 6  | ID for customized devices. Implemen-                                          |

|             |    | tation case depending.                                                        |

**Table 1:** List of module types defined so far. The number given corresponds to the value of the 3 MSBs of the module firmware implementation ID, which can be read back by accessing the module's MA 0.

following pointers are initialized and automatically made available by the software:

- 1. dword

- 2. data

- 3. mode

Please note that the pointers themselves should remain unchanged. An access like \*mode = value writes the MA register of the module for which the pointer is valid, value = \*mode stores the value of the MA register in the variable value and so on, but an access like mode = value is to be avoided, for in 99 of 100 cases it results in confusion, because the pointer to the hardware resources gets lost and the system has to be re-initialized. As will be explained in the section about the software, these pointers are data members of the class TReceiver, which is, or should be, the parent class for all properly programmed BB modules. A complete description of the software implementation would exceed the scope of this manual. What should be kept in mind is that performing a certain BB access to a certain module can simply be done by accessing the address stored in the corresponding pointer for this module. A list of all accesses is given in table 2. Please note that

**Figure 8:** Signal timing on the BB (write accesses). Timing is not to scale. The WR\_ CLK is a 16 MHz clock.

for a DWORD access a 32 bit value has to be made available. Performing a DWORD access to a byte register will yield in the best case a value which consists of four times the same byte.

Another thing is also important with the DWORD access. While for a byte access each time the BB address for the module which is going to be accessed is put on the bus, this is not the case for the DWORD access<sup>10</sup>. The BB address is not changed for a DWORD access. So, before a DWORD access to a certain module, care has to be taken to perform either a mode or a (byte) data access to exactly this module to have the desired module address applied. Otherwise the access might address a completely different module. But as in most cases before starting a DWORD access a MA has to be written to select the register, to which the DWORD access is to be performed, this condition is not very difficult to meet. Care has to be taken only when BB accesses can be performed by different threads. If e.g. during a chain of DWORD accesses performed by thread A on module 1 thread B

<sup>&</sup>lt;sup>10</sup>This is due to speed the access up; writing the address takes almost as long as an entire data (byte) access.

**Figure 9:** Signal timing on the BB (read accesses). Timing is not to scale. The WR\_ CLK is a 16 MHz clock.

reads the implementation ID of module 2, you are in big trouble.

The BB has to be terminated. The terminations have to sit on the "last module", the module that sits closest to the end of the BB. The BB must only be terminated once (more than one termination resistor array will result in data transmission errors on the bus). As will be explained in the section about the TLU, the TLU was chosen to be the module that carries the termination resistors. Therefore it was given BB address 7, but this is just a convention. The BB address has nothing to do with the order of modules on the bus and can be chosen absolutely arbitrarily as long there is no software constraint on the BB address<sup>11</sup>.

## 3.2 BB Interrupts.

The BB PCI card is capable of sending IRQs directly to the PCI bus and to the CPU. There are various reasons why such an IRQ can be generated by

<sup>&</sup>lt;sup>11</sup>In fact, the software at the moment only enforces BB address 7 for the TLU.

| Code           | Access      | Description                                 |

|----------------|-------------|---------------------------------------------|

| *mode = value  | Write mode  | Value is stored in the modules              |

|                |             | MA register. Value has to be an 8 bit type. |

| value = *mode  | Read mode   | Content of modules MA register              |

|                |             | is stored in value. Value has to            |

|                |             | be an 8 bit type.                           |

| *data = value  | Write data  | Value is stored in the register             |

|                |             | currently selected in the module.           |

|                |             | Value has to be an 8 bit type.              |

| value = *mode  | Read data   | Content of the register selected in         |

|                |             | the addressed module is stored in           |

|                |             | value. Value has to be an 8 bit             |

|                |             | type.                                       |

| *dword = value | Write DWORD | Value is stored in the register             |

|                |             | currently selected in the module.           |

|                |             | Value has to be an 32 bit type.             |

| value = *dword | Read DWORD  | Content of the register selected in         |

|                |             | the addressed module is stored in           |

|                |             | value. Value has to be an 32 bit            |

|                |             | type.                                       |

**Table 2:** Overview about BB accesses. At system startup, the pointers have to be initialized properly by the software for each BB module.

the BB PCI card. The most important thing here is, that the BB FPGA can generate an IRQ which will be sent to the PCI bus and the CPU, if a certain line from the BB itself, the IRQ line, becomes active. This is the so-called BB IRQ, which can be caused by any of the modules connected. This IRQ line is shared, i.e. more than one (all, in fact) can drive on this line at the same time. The conditions which have to be met to make a module pull the IRQ line active depend on the implementation of the module's firmware and the current module settings.

The BB FPGA contains, just like the ISRs in the different telescope modules, an 8 bit interrupt status register. In contrast to the modules ISRs, which support up to 4 different IRQ addresses, the BB FPGA supports only 3 different IRQ addresses. The fourth bit is a global enable for all IRQs which can be set by the BB FPGA. These are:

• XINT (ISR bit 0). This bit is set if any of the other three bits is set for what reason ever. Indicates a kind of global BB FPGA IRQ.

- XINT TIMEOUT (ISR bit 1). This bit is set, if the strobe of a read or write access to a certain module is not answered properly with an acknowledge signal.

- XINT ERROR (ISR bit 2). This bit is set as a result of an internal error in the state machine generating BB accesses. Please refer to the manufacturer's documentation about the BB.

- XINT MODULE (ISR bit 3). This bit is set if the BB IRQ line is pulled active by one or more modules connected to the BB. This is what in the following will be referred to as BB IRQ, the interrupt on the Blueboard bus.

The enables for these IRQs are the corresponding MSBs, so bit 4 is the global enable, bit 5 is the timeout IRQ enable etc.. To enable an IRQ, one not only has to enable the corresponding ISR bit but also the global enable. Also, the AMCC IRQ has to be enabled to allow the AMCC to pass the BB FPGA IRQ to the PCI bus. But normally this is done automatically by the startup software.

As described, during startup the software performs a scan over the entire BB address range to "detect" connected modules. This is done by disabling the timeout IRQ, sending a read access to MA 0 and, after some time, reading back the BB FPGA ISR. If the timeout IRQ is detected there, there is no module connected at this address, if not, a module is connected and the result of the read address can be taken to determine the module type. The IRQ is disabled to prevent the software from reacting to this artificial timeout like on a real timeout during system operation. For system operation, of course the timeout IRQ is enabled again. During system operation, a timeout IRQ indicates something going really wrong. The possible causes for this condition normally are either missing BB cables, missing supply voltages (not necessarily for the module which has been accessed) and so on.

If the CPU detects an interrupt request on a certain interrupt, all modules sharing this interrupt are asked if it was them who generated this IRQ. If the BB PCI card is asked, the AMCC will know that the IRQ was generated by the BB FPGA and a "Handle interrupt" function will automatically be called, but to find out what the reason of the IRQ was, one has to read the BB FPGA ISR. As it is for all the modules, the ISR of the BB PCI interface can be addressed by reading MA 1 (at BB address 0, of course). Comparing the LSBs of the ISR with its MSBs one can easily find out what the reason for the IRQ has been. If, and only if, a BB IRQ has been the reason, the IRQ handler will access the ISRs of all connected modules to find out which

**Figure 10:** Setup for VME based operation of the BB and the BAT. The role of the BB busmaster is taken by the BB VME interface, which, on its part, is controlled by the VME busmaster. This VME busmaster can be an common PC VME interface or an embedded PC / VME CPU.

module sent the BB IRQ (and, of course, why). So this IRQ processing loop is, where all the changes for different DAQ modes have to be made. The loop will, after having found and processed one module's IRQ, not return to an idle state but continue its loop through all modules connected, so all pending IRQs will be processed at a time and the IRQ source does not have to be determined more often than necessary.

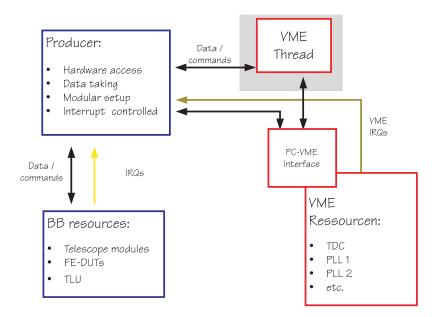

#### 3.3 The BB VME interface

As described, VME components for DUT readout can easily be taken into the readout via a PC-VME interface. DUTs can also be integrated into the BB environment by using the DTC card as an interface to the BB. There is a third way of bringing the VME-DUT world and the BB world together: The BB can be operated not using the PC as platform, but a VME-CPU, and the BB busmaster is not the BB PCI interface but a BB VME interface, whose timing and behaviour on BB side do not differ from the BB PCI interface's behaviour. On VME side, it is connected to the VME bus via a standard VME access interface circuit and can be controlled by the VME busmaster, which then is a VME CPU, an embedded PC or another PC-VME interface. A schematic overview of this setup is shown in fig. 10. As this is the solution which will be used to operate the BAT in the future by the ATLAS collaboration, such an interface is currently under development. Some re-programming will have to be done, especially concerning the IRQ handling and the software's class structure, and neither OS nor programming language are defined yet, and it is difficult to make a speed forecast, as the whole system was designed for PC based operation.

### 4 Module hardware

#### 4.1 The modules' case

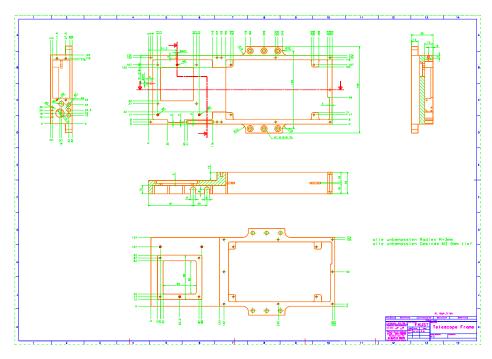

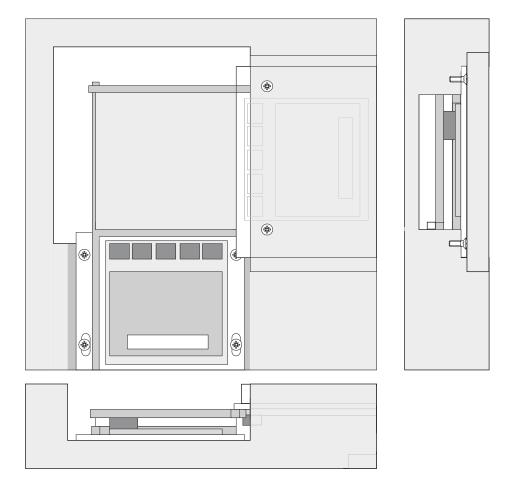

A module's case is what is visible from the outside. If the module works correctly and is properly set up, a user won't ever have to open the case and see what is inside. The case is meant to combine mechanical protection, handling fixtures and fittings, alignment marks and plugs and connectors for connecting peripherals. It has to be easy to assemble, parts have to be interchangeable, exchange should be easy and, of course, some very special demands arise from the fact that the device will be used in a very special environment. The modules consist of a solid aluminum frame, in which the different PCBs are mounted. A schematic is shown in fig. 11. The circuits will be described in detail in separate sections. A drawing of the frame (without cover plates) is shown in fig. 12. There are two compartments inside the case. The (smaller) front compartment<sup>12</sup> holds the hybrid assembly. the (larger) rear compartment<sup>13</sup> holds the ATC and the DTC PCBs. All connections to the outside needed by the PCBs are fed through fittings on the rear side of the case. Fig. 13, a schematic rear view (not to scale) of the modules rear side, shows the positions and purposes of the different connectors. Fig. 14 shows a photography of the same section. Cables from the power supplies, the TLU and the BB are connected to these plugs. The two 50 pol. IEEE 488 connectors are in- and output of the BB cable. It does not matter which BB cable is connected to which BB port. The large 8 pol. LEMO connector is for connecting the low voltage module power supplies, the small 2 pol. LEMO is for connecting the detector bias. The three single port LEMO connectors serve as in- or output for status signals. Inside the case, the BB on the DTC and the power cables on the ATC side are also connected to their PCBs using plugs. The LEMO connectors, the LED and the DTC power connections are soldered on both case and PCB side. For the newer modules the LEMO plugs are connected to the DTC using grommets. To ease assembly and to avoid wrong connections, all connectors enforce the right polarities. It is planned to replace the remaining solder connections by plugs to further increase modularity and ability to exchange parts. The four LEDs are connected with the corresponding LED on the DTC PCB. Please note that for the four modules of the prototype series sometimes the order of LED got messed up<sup>14</sup>, so it might vary from module to module. Although a

<sup>&</sup>lt;sup>12</sup>In the following, this will be referred to as detector compartment (DETC).

<sup>&</sup>lt;sup>13</sup>This will be the electronics compartment (ELEC).

<sup>&</sup>lt;sup>14</sup>This is the case especially for module 2.

Figure 11: Schematic of a BAT module setup. The two case compartments contain the hybrid assembly carrying the FE electronics and the detector and the full data acquisition electronics.

red LED in the case always corresponds to a red LED on the DTC, they are not always fixed to the same location on different modules. But the user can easily determine their function from their behaviour after reading the DTC section of this manual.

The PCBs are mounted in the ELEC as a PCB sandwich connecting the two PCBs back-to-back. The ELEC can be closed with two aluminum cover plates, one on the rear and one on the front side of the module. The cover plates provide as well mechanical and electrical protection (especially as far

**Figure 12:** Drawings of the module's frame. The layout of the cover plates is not shown. The missing covers exist of 4 parts: 2 larger aluminum plates, which serve as cover for ELEC, and a small frame and another plate, which serve as DETC cover.

Figure 13: Schematic back side view of a module showing the positions of the different connectors and indicator LEDs. For the modules of the prototype series, the positions of the latter may vary.

as the high voltage section on the ATC is concerned) as electromagnetic shielding of the components (especially important for the DETC), so care has to be taken to provide a conductive connection between the case and the cover plates (especially in case the frame and cover plates are anodized). The hybrid assembly is not directly fixed to the case. Between the screwholes in the case and the hybrid assembly three 2 mm thick washers have to be placed which decrease thermal conductivity between the hybrid assembly and the case. This is because the two ELEC PCBs generate much more heat that the hybrid assembly does; thus the ELEC is prevented from heating the hybrid assembly. It is possible to cool the hybrid assembly using an external chiller. The assembly frame for the hybrid assemblies has a pipe structure implemented for this purpose and grommets for cooling pipes have been implemented in the module's case. Small aluminum pipes were manufactured which can be attached directly to the hybrid assembly and were supposed to serve as in- and outflow for coolant of any kind, but the possibilities offered by this feature are not yet fully exploited.

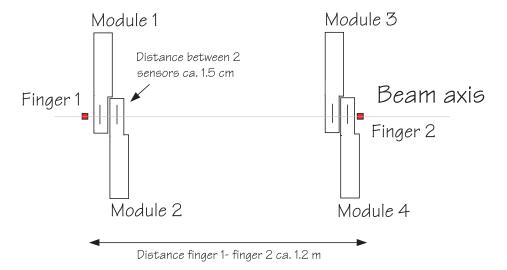

**Figure 14:** Photography of a module's back side holding the connectors. The LED are hardly visible, because they are not lit. The blue IEEE 488 connectors have been replaced later by a more reliable type which is black.

21

The cover for the DETC consist of two parts: The back side of the DETC is mostly covered by the case itself, leaving only a small window directly under the detector as pass-trough region for the beam. As this window has to be covered with as little material as possible to reduce radiation length, a frame has been manufactured which fits into a flange on the back side of the case and can be filled with material that has the desired properties, namely low radiation length, mechanical solidity and electrical shielding<sup>15</sup>. The best results were achieved with either two layers of aluminum foil or a single layer of copper plated capton. Care has to be taken here as well to provide a good electrical contact between shielding and case. The front side of the DETC is covered with an aluminum cover plate with a window left out where the detector is. This window is also to be covered with the same shielding material as is used on the back side. Also, some sealing has to be attached at the edge of the cover plate which covers the spacing between DETC and ELEC. This sealing has to be light tight and enables, if attached, the user to probe on the ATC with depleted detector and the ELEC cover on ATC side removed. The sealing reduces contributions to the detector leakage current generated by incident light and preserves normal system operation while debugging. Also it provides some protection for the DETC against dust and dirt if the ELEC cover is removed. However, care has to be taken to open the cover of the DETC only with the detector bias voltage off and when it is not avoidable. It has to be done under conditions where it can be made sure the hybrid assembly is not damaged and where it can't become dirty. Also, some precautions have to be taken while debugging on the ATC of a depleted detector module even when the DETC is closed. These will be explained in the section about the ATC. A picture of a fully covered module is shown in fig. 15. The origin of the telescope coordinates is given by the first channels on both P- and N-side hybrids. The position of this origin is also shown in fig. 15. The case also provides some fittings for the connection of the module to some support structure in the testbeam area. In fig. 15 one of the fittings is visible as the "wing" on the long side of the module. The positions of the modules relative to each other and relative to the beam and the coincidence counters depend as well on the beam profile shape and direction as on the beam parameters like beam energy. To minimize the influence of coulomb multiple scattering caused by the material unavoidably present in the beam line to the trace recognition accuracy especially at low beam energies it might be necessary to put two modules' detectors as close to each other as possible. This was done at the E3 testbeam facility in Bonn. The shape of the case was optimized for this kind of arrangement. The setup is shown in fig. 16.

<sup>&</sup>lt;sup>15</sup>The cover also has to be opaque.

**Figure 15:** Photography of a fully covered module (front side). The ELEC and DETC covers can clearly be distinguished. The beam window is covered with copper plated capton. The origin of the module coordinates (crossing of strip 1 on N side and strip 1 on P side) is indicated by an arrow.

To ease handling and to as well set up as determine the alignment of the

**Figure 16:** Testbeam setup at E3. The special arrangement of the modules is used to minimize influence of coulomb multiple scattering The shape of the modules helps to bring two modules sensors as close together as possible.

modules relative to each other and to the beam, some alignment marks at the outside of the DETC mark the position of the detector center. There are two alignment marks for each module. They are made up of two cylindrical holes in the frame. Their position on the case is at the point where the center of the sensor inside the case is meant to be for the corresponding dimension. So the position of the sensor center is at the cross-over point of the lines parallel to and through the middle of the alignment holes<sup>16</sup>. It is planned to manufacture small cones which fit into the holes and have their apex right above the hole center, so alignment will be even more easy.

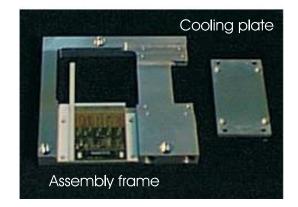

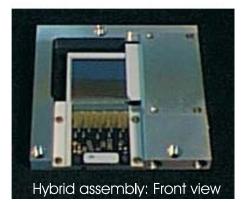

### 4.2 The hybrid assembly

The hybrid assembly is the most advanced mechanical part of the module. It carries as well the front end electronics for detector readout as the detector itself. It has to provide mechanical support for these parts and easy handling possibilities. Once a hybrid assembly is assembled, it forms a unit together with the two hybrids and the detector it is assembled with. It is not possible to disassemble an assembled hybrid assembly without at least destroying the detector. The mechanical structure is quite complex. For more details please refer to the drawings of the hybrid assembly parts. It has to bear the large area silicon strip detector, only being allowed to support it under the very edges and in no case directly under the sensitive area. To simplify bonding and to avoid putting unnecessary material into the beam line, the hybrids are mounted right angled<sup>17</sup> to each other. So no Z-print is needed at the expense of a somewhat more complicated structure of the assembly frame. The assembly frame, which is the "solid" part of the hybrid assembly, is manufactured from a monolithic aluminum block. It is designed to combine mechanical reliability, low thermal expansion and good cooling efficiency with good accessibility to ease bonding. As mentioned, the hybrid assembly can be cooled making use of a pipe structure in the assembly frame. It has to be manufactured very precisely. As the silicon detector is very thin, small mechanical tensions can be hazardous and may result in damaging or even breaking the detector. For the same reason, gluing has to be done very carefully as well.

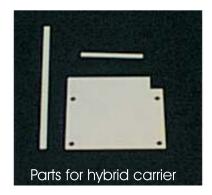

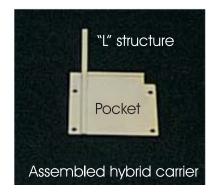

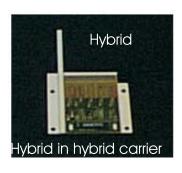

A schematic view of the hybrid assembly is given in fig. 17. An overview about the assembly steps is shown in fig. 18. The front end hybrids are not directly glued to the assembly frame. For each hybrid a hybrid carrier structure is manufactured. As the hybrids consist of a PCB glued to an aluminum oxide ceramic carrier, the hybrid carrier also consists of aluminum oxide ceramic plate, the backplane, with some drill holes used to fix the carrier to the assembly frame. 2 ceramic strips are glued to the backplane in a T-shape, thus forming either a pocket, in which the hybrid itself is fixed, and a "L" structure, which will form the support for the detector's edge on

<sup>&</sup>lt;sup>16</sup>Of course, due to assembling inaccuracies the real position might be somewhat different from the ideal position, so the actual alignment still has to be calculated from the data.

$<sup>^{17}</sup>$ The stereo angle of the detector is 90°.

Figure 17: Schematic drawing of a fully mounted hybrid assembly. Different colours indicate different parts. The pipe structure for coolant is not visible. In the projections of the assembly to the small sides, only one FE IC is shown for simplicity. For this arrangement of the hybrids the "origin" of the telescope, being the crossing of the strip centers for the strips 1 on both detector sides, is in the lower right corner of the detector.

two sides. As this gluing process has to be very precise and reproducable, a special gluing tool is used to make the parts sit at the exact position with high accuracy. The hybrid is glued to the hybrid carrier's backplane using an elastic silicon adhesive which can compensate thermal expansion. The fully assembled hybrid carrier is then fixed to the assembly frame. Four screws, which are only slightly tightened, determine its position on the assembly frame. The screw holes in the ceramic plate are quite large, so there is some fetch, but the hybrid carrier's back side is covered with thermal grease, which as well serves as an adhesive as it manages to compensate differences in the thermal expansion coefficient between the ceramic hybrid carrier and

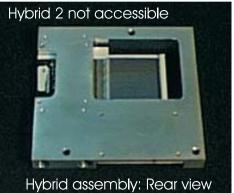

the aluminum of the assembly frame. In the next step, the sensor is glued to the L-shaped ceramic of the first hybrid carrier, and the second hybrid carrier is then inserted in its fittings on the assembly frame head first and right-angled to the first hybrid carrier and fixed with screws. The detector is glued to this hybrid carrier's "L" structure as well. Care has to be taken here, for due to the shape of the assembly frame the second hybrid won't be accessible any more after gluing (except for the FE-ICs bond pads and the connector to the ATC, of course). So, all modifications necessary for this hybrid have to be made before fixing it to the hybrid assembly. Please note that the hybrid on the first hybrid carrier should always contact the p-side of the detector<sup>18</sup>, so be careful. To make a connection between the second hybrid carrier (the one that contacts the detector n-side) and the assembly frame with good thermal conductivity, the back side of the carrier is covered with an aluminum cooling plate which is screwed to the assembly frame. The spacing between hybrid carrier ceramics and aluminum cooling plate is filled with thermal grease. The cooling plate also provides mechanical protection for the second hybrid carrier's backplane. Now the hybrid assembly is ready for bonding.

If the hybrid assembly is set up correctly, the detector surface should be on a level with the surface of the FE-ICs and the distance between the bond pads should be as small as possible on both sides. So bonding the hybrid assembly should be easy. Whenever dealing with the hybrid assembly, one has to be extremely careful not to damage the bonds or to mechanically stress the detector itself, for it is only fixated with small thin strips of "brittle" ceramics.

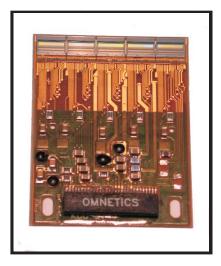

After assembling the hybrid assemblies of the prototype series it turned out that the common mode noise can be significantly reduced by adding a large additional filtering low-pass circuit for the detector bias voltage directly to the detector. The low pass capacitor had to be placed as close as possible to the hybrids, so it had to be glued directly to the assembly frame itself. A view of a fully equipped module's DETC is given in fig. 19. The cables used to connect the hybrids with the corresponding ATC compartment use small, expensive connectors manufactured by Omnetics on hybrid side. On ATC side, standard IDC connectors were used. When manufacturing the prototype series modules, it was not possible to provide the Omnetics type connectors with flat ribbon cable needed to make good contact to the IDC connectors, but with single wire contacts only. It was difficult get a reliable contact between hybrid and ATC that way. This will hopefully be fixed in later versions, either by using another type of connector on the hybrids

<sup>&</sup>lt;sup>18</sup>There is, of course, no physical reason for this. It's pure convention.

Figure 18: How to assemble a hybrid assembly. First line: Parts, of which a hybrid carrier consists and fully assembled hybrid carrier. Second line: Hybrid attached to hybrid carrier and inserted into the assembly frame. Detector and second hybrid are attached simultaneously in the next step. Third line: Fully assembled hybrid assembly viewed from both sides.

**Figure 19:** A view of a module's DETC equipped with a hybrid assembly. The hybrid assembly has an additional low pass capacitor at the right edge of the frame. The interconnection cables from the p-side hybrid to the ATC are also visible.

replacing the expensive Omnetics type or by using flat ribbon cable instead of single wires for the connection to the IDC plug.

| Gain              | $25~\mu\mathrm{A}$ / fC                                    |

|-------------------|------------------------------------------------------------|

| ENC               | $80 \pm 15 \mathrm{e^-}$ / pF @ 1 $\mu\mathrm{s}$ shaping  |

|                   | $60 \pm 11 \mathrm{e^-}$ / pF @ 2 $\mu \mathrm{s}$ shaping |

| Dynamic range     | $\pm~4~\mathrm{MIPs}$                                      |

| Peaking time      | $0.5$ - 3 $\mu { m s}$                                     |

| Power consumption | $1.2~\mathrm{mW}$ / channel                                |

| Applications      | Medium sized detectors                                     |

|                   | with $\approx 10$ pF load capacitance                      |

**Table 3:** Overview about the parameters of the VA 2 IC. ENC values are given depending on the load capacitance on the VA input.

#### 5 Front end electronics

Only a brief description of the BAT front end electronics is given here, as a much more detailed description can be found in the publications listed below. Concerning the VA 2 ICs:

• The VA 2. Specifications & manual. Version 1.4. Published by IDE on May, 14th, 1997.

Concerning the VA hybrids:

- Technical design report for BELLE readout hybrid. Author: Bjørn Magne Sundal. Published by IDE on October, 7th, 1997.

- BELLE SVD Hybrid, Conceptual design report. Version 2.3, published by IDE on August, 13th, 1997.

#### 5.1 The VA 2 IC

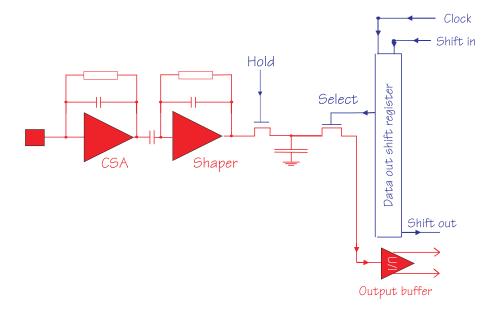

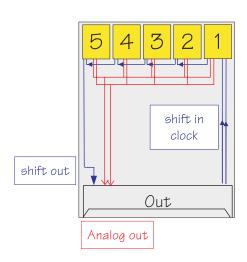

The VA 2 IC is a 128 channel low noise and low power charge sensitive preamplifier-shaper circuit with simultaneous sample and hold, serial analog readout and calibration facilities. A schematic of one channel and the chip's read out serializer circuit is shown in figure 20. An overview about the most important parameters of the VA 2 is given in table 3. The IC is controlled via 5 digital input signals:

1. Hold: (Active low) The hold signal toggles between sample and hold mode of the VA 2 circuit. With hold being inactive, the voltage signal on every channel's sampling capacitor follows the preamplifier/shaper

**Figure 20:** Simplified schematic of a single VA 2 channel and the chip serializer structure. The *hold* signal toggles between sample and hold mode. The *clock* can be operated up to a frequency of 10 MHz. Via *shift in* data can be fed into the VAs serializer shift register. The channels selected in this way put the voltage signal on their sampling capacitor to the outside using the differential analog output buffer.

output. If *hold* becomes active, the sampling capacitor is undocked from the preamplifier output and the voltage level is stored.

- 2. Shift in: (Active low) This is the input line for the IC's serializer shift register and for the IC's calibration shift register.

- 3. Clock: (Active low) This is the clock signal for both, the IC's serializer and calibration shift register.

- 4. Digital reset: (Active high) With digital reset the contents of both calibration and serializer shift register are reset to zero (zero here means inactive).

- 5. Test on: (Active high) This signal toggles, whether the serializer shift register or both serializer and calibration shift register receive the clock signal.

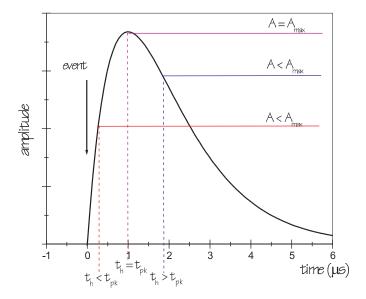

The VA 2 is equipped with a RCCR shaper for each preamplifier cell, whose shaping time can be varied with some bias parameters. The bias parameters are listed in table 4. Typical values are 1-2  $\mu$ s. The advantage of

| Name      | Task                                      | Typical value |

|-----------|-------------------------------------------|---------------|

| $V_{fp}$  | Control voltage for feedback resistor in  | -200 mV       |

|           | preamplifier                              |               |

| $I_{pre}$ | Bias current for preamplifier             | $500 \ \mu A$ |

| $V_{fs}$  | Control voltage for feedback resistor in  | 700  mV       |

|           | shaper amplifier                          |               |

| $I_{sha}$ | Bias current for shaper amplifier         | $22 \mu A$    |

| $I_{buf}$ | Bias current for differential analog cur- | $140 \ \mu A$ |

|           | rent output buffer                        |               |

Table 4: Bias voltages and currents needed by the VA 2 IC

a RCCR shaper is a peaking time  $t_{pk}$  which is nearly independent from the total signal amplitude.

The serializer shift register contains 128 cells, one for each preamplifier channel, and one analog output buffer, whose output signal consists of a differential analog signal current. Whenever the shift register cell for a channel is active, the sampling capacitor for this channel is connected with the analog output buffer's input. The (differential) current flow out of the analog output buffer is given then by

$$I_{+} = \frac{I_{buf}}{2} + \frac{I_{signal}}{2}$$

$$I_{-} = \frac{I_{buf}}{2} - \frac{I_{signal}}{2}$$

with  $I_{buf}$  being the buffer bias current, one of the VAs bias parameters, and  $I_{signal}$  the signal voltage on the sampling capacitor converted to a signal current. This signal consists of a channel specific pedestal value, which is simply the default output voltage of the preamplifier channel, and an "event part", which is generated by additional charge generated by an event on the input of the preamplifier channel.

$$I_{signal} = I_{pedestal} + I_{event}$$

For the event part of the signal current, typical gain values are 25  $\mu$ A signal current per fC injected charge. Problems arise if there is more than one shift register cell active. As it is impossible to separate the signals, care has to be taken to make sure that there is only one shift register cell activated at a time.

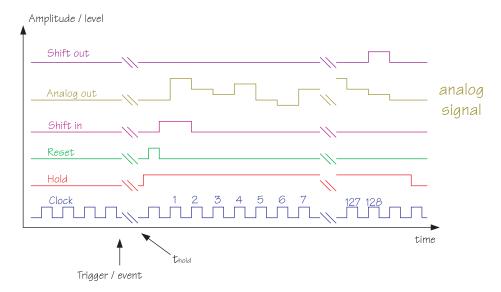

In the following, a typical readout sequence is described as it is implemented in the BAT DTC firmware. The chip is not self-triggering, so an external trigger signal is needed to activate the (external) readout sequencer. In normal (test on is inactive) operation mode, this external trigger signal indicates

**Figure 21:** Hold timing of the VA 2 IC. This is the ideal situation with  $t_{tl}$  = 0 (no trigger latecy). The peaking time can be adjusted with some bias parameters of the IC. Typical values are 1-2  $\mu$ s. Choosing hold times either too long or too short will yield in signal loss.

the occurrence of an event and start the readout sequencer. Depending on the trigger latency<sup>19</sup>  $t_{tl}$  the readout sequencer has to activate the *hold* signal together with the preamplifier signals reaching their maximum or at least as close to this point of time as possible. Ideally, the *hold* signal would be turned on when the hold time  $t_h$ , which is given by

$$t_h = t_{pk} - t_{tl}$$

has passed. Otherwise, the bad timing results in signal loss (see figure 21). To prevent unwanted data in the output serializer shift register, the sequencer gives a digital reset, and the serializer shift register is initialized with a single "one" and one clock pulse at the beginning. With another clock pulse, the next cell is selected and so on. The output signal then is a series of 128 differential analog signal currents. During the readout of a singe VA, the hold signal has to be kept active. The 128th shift register cell's output is directly connected to the shift out output pad. If all went well, a single one appears at this output after the 128 th clock pulse, indicating that now the 128th channel is active and thus the readout of the IC has been successfully completed. The hold signal can be released afterwards. A typical readout

<sup>&</sup>lt;sup>19</sup>The delay between the actual event and the arrival of the trigger signal generated by some trigger detectors.

sequence is displayed in fig. 22.

The noise behaviour and signal response of a single preamplifier channel can

**Figure 22:** Readout sequence of a VA 2 IC. Only logic levels are shown independent from the "real" signal polarity.

be observed by activating the corresponding serializer shift register cell, thus putting the voltage signal of the sampling capacitor on the output buffer, and disabling the hold signal.

When the IC is operated in test mode, the calibration register, a second 128 cell shift register running in parallel to the serializer shift register, is initialized and clocked together with the serializer shift register. If a preamplifier cell is selected with the calibration register an analog input of the VA 2, the cal line, is connected directly with the preamplifier input. Injecting small charge signals on the cal line will yield a pulse answer, which can be observed directly at the analog output as described above. This is a common procedure to calibrate the ICs and to adjust bias parameters.

The VA 2 IC is designed for medium preamplifier load capacitances. The bond pads for the preamplifier channel inputs are arranged in two staggered rows with 50  $\mu$ m pitch. For each channel, an additional "spare" bond pad is present.

#### 5.2 The BELLE hybrid

The VA 2 ICs are suitable for daisy chained readout. The shift out signal of a VA can serve as shift in signal for another VA receiving the same clock signal.

**Figure 23:** Picture and schematic view of a BELLE VA 2 hybrid. Several passive components provide decoupling of bias and supply lines. The first VA being the VA which is initialized first, is the rightmost one.

Thus, the  $2 \times 128$  cell shift registers of the 2 VA behave like a 256 cell shift register of a larger VA. If one connects the differential current output signals of the two VAs directly together<sup>20</sup>, the differential current signal observed on this line also behaves like the output signal of a 256 channel VA. Of course, not only the clocks of the 2 VAs are connected in daisy chained operation. All digital control signals are connected together with the *shift out - shift in* connection being the sole exception.

This feature is especially useful, if a detector larger than  $128 \times 50~\mu\mathrm{m}$  is to be read out. Operating two or more VAs daisy chained enables the user to read out the whole detector at once using only one sequencer and signal digitization circuit at the cost of a somewhat slower serial readout. Supply and bias voltages have to be adapted to the new higher current draw, and, as far as bias parameters and shaping times are concerned, a compromise has to be found between effort and flexibility: the preamplifier gains and, even more important, the shaping times should be adjustable to the same value for all the different VAs.

In the BAT setup, detectors of  $3.2 \times 3.2$  cm<sup>2</sup> and  $50~\mu m$  strip pitch were used, so 640 VA channels corresponding to exactly 5 ICs were needed. This was the reason why it was decided to use the BELLE SVD hybrids in the BAT setup. The BELLE hybrids were originally developed for the silicon vertex detector of the BELLE experiment at KEK in Japan. A BELLE

<sup>&</sup>lt;sup>20</sup>This would not be possible for differential voltage outputs.

hybrid carries 5 daisy chained VA ICs on a ceramic carrier together with a small 2 layer PCB providing all control signals, bias and supply voltages to the ICs. The PCB also holds some resistors and capacitors for power line and bias decoupling. All signals are fed to the hybrids by a single connector. As described, the readout is daisy chained and serial. The ceramic carrier provides good thermal conductivity to the support structure. Moreover, the small difference in the thermal expansion coefficient minimizes the stress on both sensor and FE ICs<sup>21</sup>. A photography of a BELLE hybrid together with a simplified schematic of the readout is shown in fig. 23. The full schematic of the hybrid is shown in figure 24. All control signals except for em shift in are fed to all ICs in parallel, their output signal lines are connected together. The supply voltages, preamplifier and shaper bias currents are fed to all ICs by a single connector line, so care has to be taken when designing the current sources as a current draw five times higher that the current draw of a single VA will occur on these lines. For the shaper bias current, additional in-line resistors can be used on the hybrid<sup>22</sup> to regulate the current draw to the individual VA ICs. The buffer bias current supplies the current for the VAs' analog output buffer. This current only flows if an output shift register is active. Only one VA shift register should be active at a time, so this current has to be provided only once (same current draw as for a single VA IC). The preamplifier bias voltage is also set for all VAs in common, but the

used to adjust  $t_p k$  of the different VAs to the same value. The hybrid carries an integrated calibration capacitor for each VA. Two copper layers in parallel, the space in between filled with some dielectric, form a capacitor with a capacitance of  $\approx 0.5$  fC. One side of a calibration capacitor is directly to a VA 2 calibration input, the other side is connected with the calibration capacitors of the other hybrids and a calibration signal coming from the connector. The calibration signal is terminated with a 50  $\Omega$  resistor, which has to taken into account when calculation the amount of charge generated by an applied voltage step at the calibration capacitor's input.

shaper bias voltage can be set for each VA IC individually. As the shaper bias voltage has a large influence on the peaking time, this feature can be

Although the digital signal inputs of the VA are single ended, 2 bond pads are provided on the IC for clock, hold and digital reset. One of the pads (the non-inverted signal pad, as the VA uses active low logic) is not connected to the IC's circuits. In spite of that signal lines exist on the hybrids for these "dummy" signals. By driving differential signals on these signal lines, digital

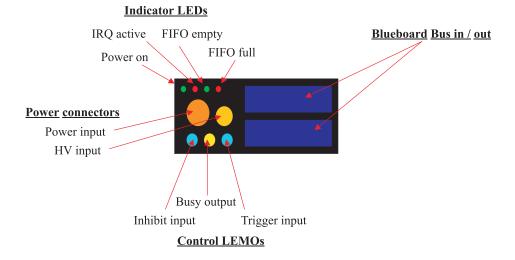

<sup>&</sup>lt;sup>21</sup>See also the section about the hybrid assembly.