# Application Brief Supporting Time and Skew Sensitive Interfaces with TI's TXV Level-Shifter Portfolio

Joshua Salinas

### Introduction

Physical layer devices (PHYs) play an important part of the Ethernet network protocol as they bridge data communication from the external world by serializing and de-serializing data over many different types of translation media. PHYs are connected to an Ethernet media access controller (MAC), which is typically integrated in an FPGA or SoC. Interface design challenges often arise as large digital devices like SoCs, ASICs, and FPGAs move to lower core voltages. Integrated and standalone MACs are often not able to support a higher I/O voltage when operating at low voltages. System designers often need to resolve I/O level mismatch between the MAC and PHY while still maintaining the signal integrity of the interface. Additionally, Ethernet interfaces like Reduced Gigabit Media Independent Interface (RGMII) have strict timing requirements, which are even harder to meet at lower voltages.

This application brief provides over the timing requirements of RGMII and show how TI's high speed TXV family can meet RGMII timing requirements while overcoming I/O voltage mismatch.

#### **RGMII Timing Requirements**

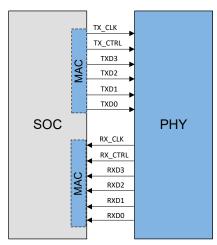

RGMII is an interface used between the MAC and PHY and allows speeds of 10 Mbps, 100 Mbps and 1000 Mbps. Figure 1 shows the connection between the MAC and PHY. The timing requirements are more strict when operating at 1000 Mbps since data is processed in Dual Data Rate (DDR) signaling while the lower speeds use Single Data Rate (SDR). 1000 Mbps timing will be used throughout this app brief since satisfying those requirements also satisfies 10 Mbps and 100 Mbps timing requirements.

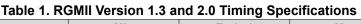

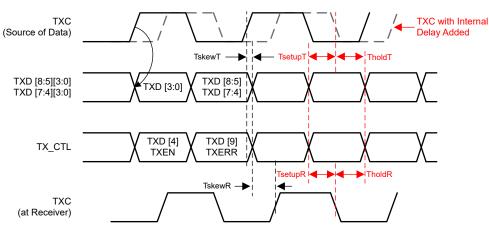

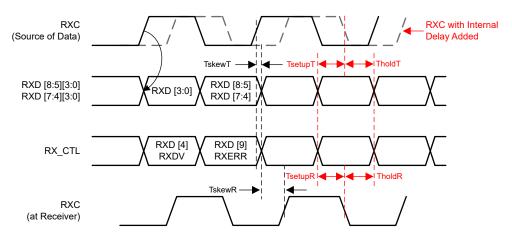

Table 1, Figure 2 and Figure 3, show the timing requirements for both RGMII Version 1.3 and 2.0 standards. Version 1.3 states skew must be introduced between the clock and data lines, typically around 1.5 to 2.0 ns. In Version 2.0, skew can be generated by either the MAC or PHY and are given by  $T_{setupT}$  and  $T_{holdT}$ . RGMII Version 2.0 timing is highlighted in red.

1

| Symbol                         | Parameter                                     | Min  | Typical | Мах  | Units |

|--------------------------------|-----------------------------------------------|------|---------|------|-------|

| T <sub>skewT</sub>             | Data to Clock Output<br>Skew (at Transmitter) | -500 | 0       | 500  | ps    |

| T <sub>skewR</sub>             | Data to Clock Input<br>Skew (at Receiver)     | 1    | 1.8     | 2.6  | ns    |

| T <sub>setupT</sub>            | Data to Clock Output<br>Setup                 | 1.2  | 2.0     |      | ns    |

| T <sub>holdT</sub>             | Data to Clock Output<br>Hold                  | 1.2  | 2.0     |      | ns    |

| T <sub>setupR</sub>            | Data to Clock Input<br>Hold                   | 1.0  | 2.0     |      | ns    |

| T <sub>holdR</sub>             | Data to Clock Input<br>Hold                   | 1.0  | 2.0     |      | ns    |

| T <sub>cyc</sub>               | Clock Cycle Duration                          | 7.2  | 8       | 8.8  | ns    |

| D <sub>cyc</sub>               | Duty Cycle for Gigabit                        | 45   | 50      | 55   | %     |

| T <sub>R</sub> /T <sub>F</sub> | Rise/Fall Time<br>(20-80%)                    |      |         | 0.75 | ns    |

### **TXV Output Skew Measurements**

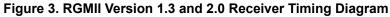

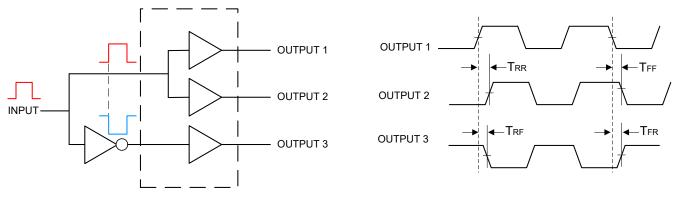

The output channel-to-channel skew,  $T_{sk(o)}$ , value found in the data sheet uses two types of skew measurements to capture the worst-case skew, output and inverting skew. An illustration for both can be found in Figure 4.

Figure 4. Output Skew (T<sub>RR</sub>/T<sub>FF</sub>) and Inverting Skew (T<sub>RF</sub>/T<sub>FR</sub>) Measurements

Output skew is the skew difference between any two outputs of the same device at identical transitions while driving identical specified loads. Output skew measurements are given by  $T_{RR}$  and  $T_{FF}$ . Inverting skew is the skew difference between two outputs of the same device with opposite input transitions while driving identical specified loads. Inverting skew measurements are given by  $T_{RF}$  and  $T_{FF}$ .

### **TXV Timing Benefit**

Table 2 gives the timing difference between the TXV family and the RGMII standard. The comparison below shows the worst case timing of the TXV does not exceed the maximum timing parameters of the RGMII standard. This leaves timing margin to the MAC, PHY and PCB, and shows the TXV product family is suitable to interface with RGMII, even at 1000 Mbps.

|                                | •                                  |                        |           |       |  |  |

|--------------------------------|------------------------------------|------------------------|-----------|-------|--|--|

| Symbol                         | Parameter                          | TXV Max <sup>1 2</sup> | RGMII Max | Units |  |  |

| T <sub>sk(o)</sub>             | Output Channel-to-<br>Channel Skew | ± 317                  | ± 500     | ps    |  |  |

| T <sub>R</sub> /T <sub>F</sub> | Rise/Fall Time (20-80%)            | 0.48                   | 0.75      | ns    |  |  |

| D <sub>cyc</sub>               | Duty Cycle                         | ± 4                    | ± 5       | %     |  |  |

Table 2. Comparison Between TXV0106/TXV0108 and RGMII Timing Specification

### Conclusion

Processors such as FPGA, SoC, and ASICs are moving to lower voltage I/Os benefiting customers by reducing power consumption. This can result in I/O voltage mismatch, however, many level-shifters are not capable in meeting strict timing requirements like rise/fall time, channel-to-channel skew and duty cycle distortion for skew sensitive interfaces. This application brief demonstrated how the TXV level-shifter family can bridge the I/O voltage gap while also delivering optimized AC performance and meeting strict timing requirements for low-skew interfaces like RGMII.

3

$V_{CCA}$  = 1.8 V,  $V_{CCB}$  = 3.3 V,  $C_{Load}$  = 5 pF, 250 Mbps for each data channel at 125°C

<sup>&</sup>lt;sup>2</sup> Different voltage and loading conditions can also be found in the timing section on the TXV0106 and TXV0108 data sheet

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated