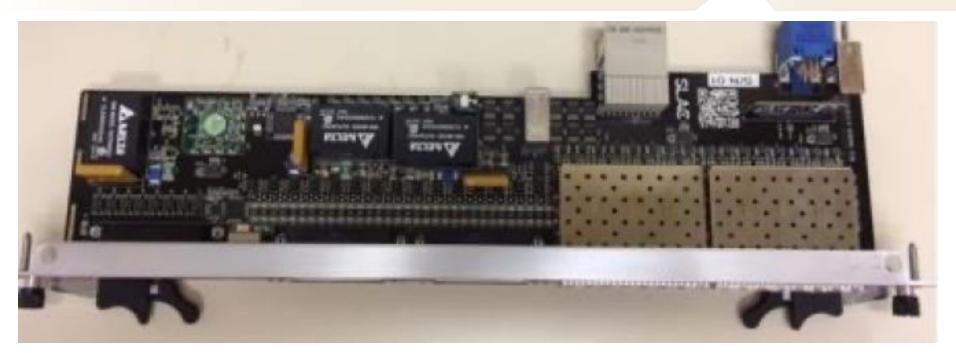

### **Most Used MPS/Timing RTM**

MPS/Timing Rear Transition Module

# **Most Used MPS/Timing RTM**

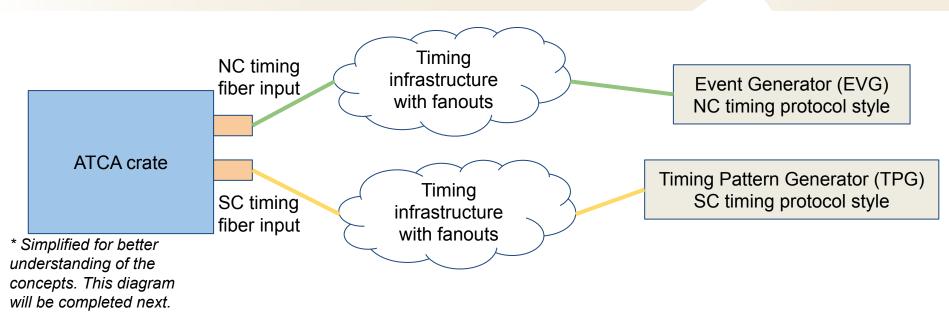

- Timing data must be consumed by all carrier boards.

- Ideally we should use one single RTM to receive timing as opposed to connecting timing RTMs to each slot.

- Saves money in RTM boards and fibers.

- Make space for application specific RTMs.

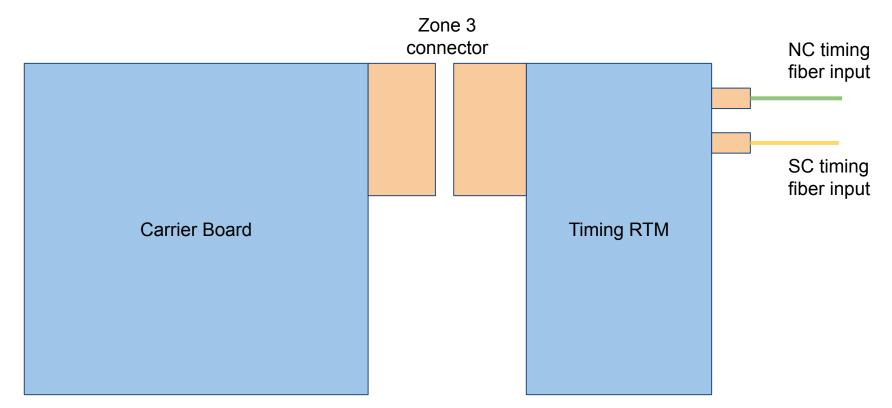

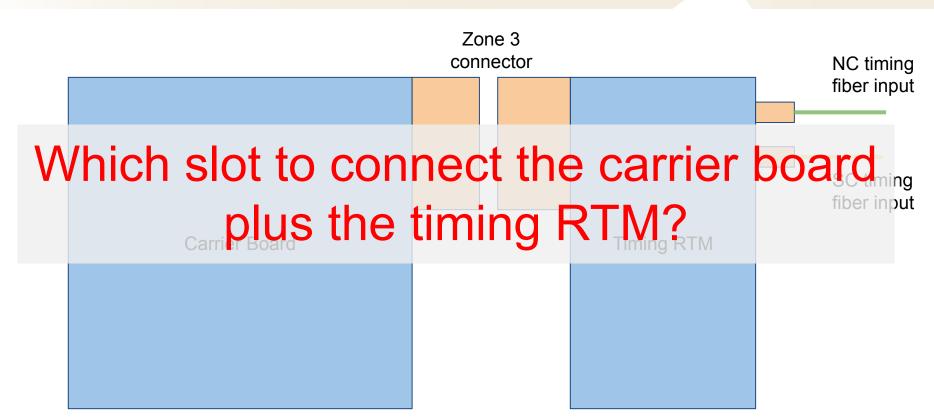

- As seen, only slots 1 and 2 are connected to all other slots.

- Slot 1 is already reserved to the Ethernet switch.

- So, the only way is to connect the timing RTM to the carrier board at slot 2.

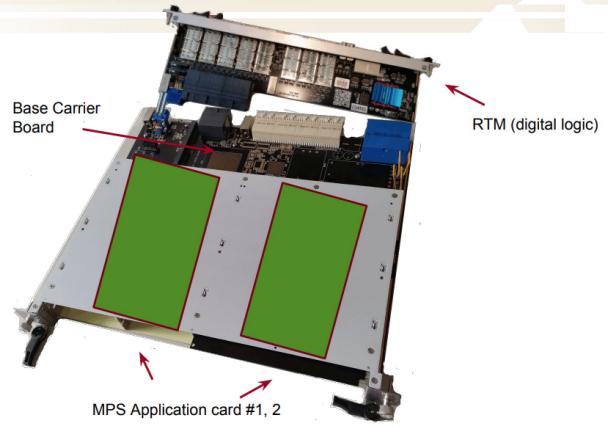

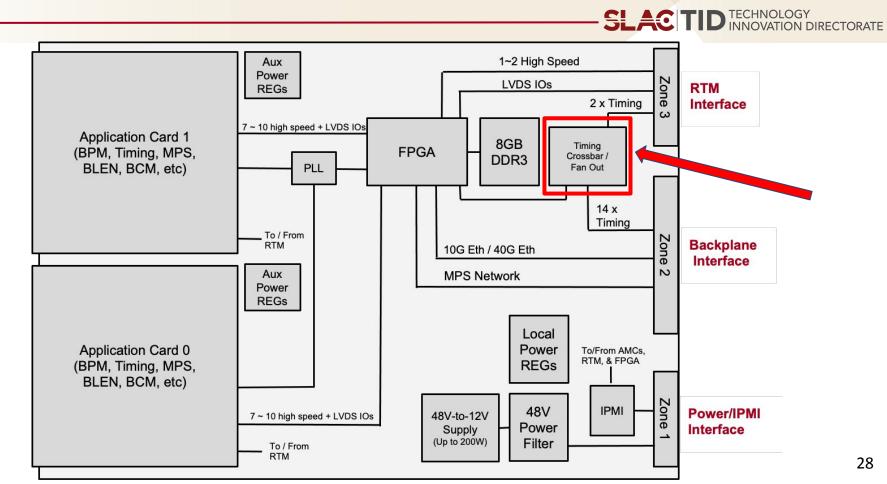

#### **AMC Carrier Board**

#### 4 sources of input

There are 4 sources of output, but only 2 are used in fact. (the other 2 go back to zone 3)

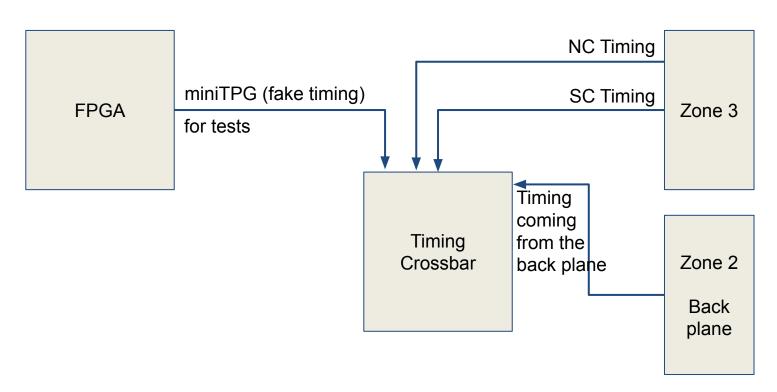

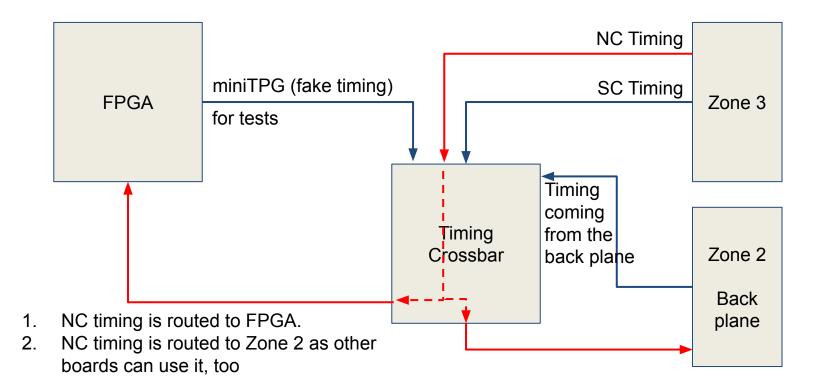

#### Configuration for carrier in slot 2 using NC timing

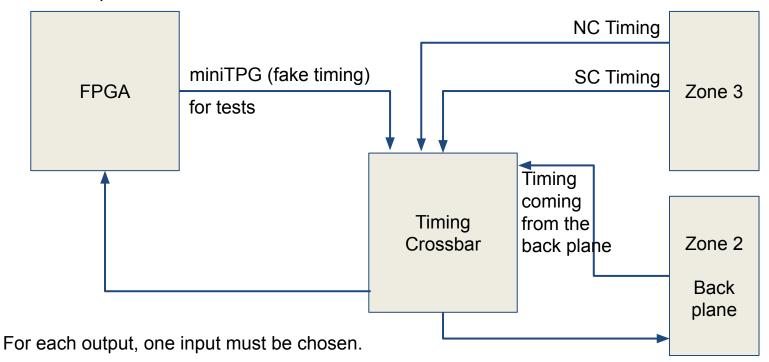

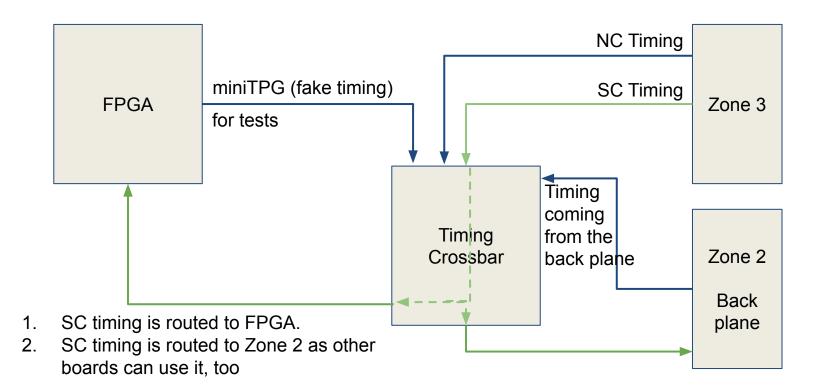

#### Configuration for carrier in slot 2 using SC timing

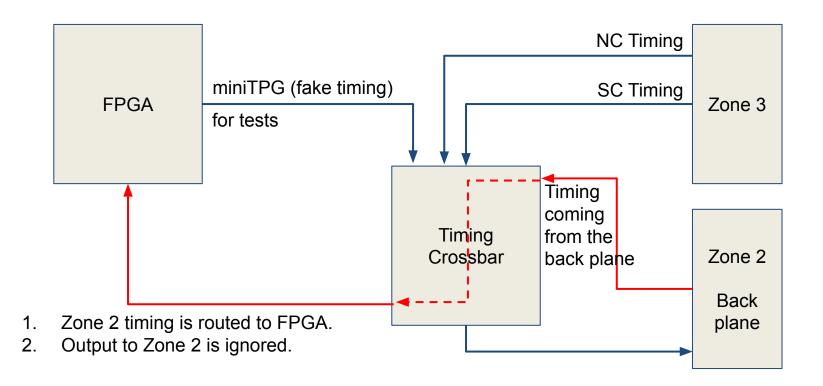

#### Configuration for carrier in other slots

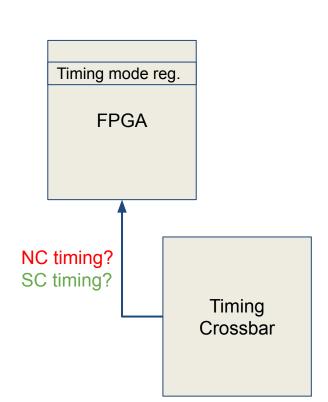

The timing mode is not auto-discovered by the FPGA. There is a register that needs to be set to make the firmware to interpret the protocol correctly.

When changing the timing mode, a few actions are needed:

- 1. Change timing mode register in the FPGA of all carrier boards installed.

- 2. Slot 2 crossbar must be set to route the correct timing mode to its own FPGA.

- 3. Slot 2 crossbar must be set to route the correct timing mode to Zone 2 as the other boards can receive them from the back plane.