# FIR Compiler v7.2

# LogiCORE IP Product Guide

**Vivado Design Suite**

**PG149 November 18, 2015**

# **Table of Contents**

#### **IP Facts**

| Chapter 1: Overview                 |       |

|-------------------------------------|-------|

| Feature Summary                     | 6     |

| Licensing and Ordering Information  | 7     |

| Chapter 2: Product Specification    |       |

| Performance                         | 8     |

| Resource Utilization                | 8     |

| Port Descriptions                   | 9     |

| Chapter 3: Designing with the Core  |       |

| Clocking                            | 12    |

| Resets                              | 12    |

| AXI4-Stream Considerations          | 13    |

| Core Features                       | 20    |

| Input and Output Sample Rate        | 67    |

| Resource Considerations             | 69    |

| Chapter 4: Design Flow Steps        |       |

| Customizing and Generating the Core | 73    |

| System Generator for DSP            | 87    |

| Constraining the Core               | 89    |

| Simulation                          | 89    |

| Synthesis and Implementation        | 90    |

| Chapter 5: C Model                  |       |

| Unpacking and Model Contents        | 91    |

| Installation                        | 93    |

| C Model Interface                   | 93    |

| MATLAB Interface                    | . 109 |

| Dependent Libraries                 | . 112 |

|                                     |       |

2

# **Chapter 6: Test Bench**

| F                                                  |     |

|----------------------------------------------------|-----|

| Demonstration Test Bench                           |     |

| Simulation                                         | 115 |

| Appendix A: Migrating and Upgrading                |     |

| Migrating to the Vivado Design Suite from ISE      | 116 |

| Upgrading within the Vivado Design Suite           | 124 |

| Appendix B: Debugging                              |     |

| Finding Help on Xilinx.com                         | 125 |

| Debug Tools                                        | 126 |

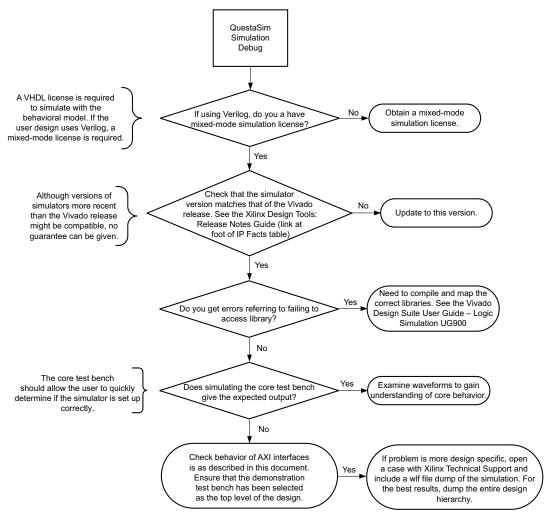

| Simulation Debug                                   | 127 |

| AXI4-Stream Interface Debug                        | 128 |

| Appendix C: Additional Resources and Legal Notices |     |

| Xilinx Resources                                   | 129 |

| References                                         | 129 |

| Revision History                                   | 130 |

| Please Read: Important Legal Notices               | 131 |

# Introduction

The Xilinx® LogiCORE™ IP FIR Compiler core provides a common interface to generate highly parameterizable, area-efficient high-performance FIR filters.

# **Features**

- AXI4-Stream-compliant interfaces

- High-performance finite impulse response (FIR), polyphase decimator, polyphase interpolator, half-band, half-band decimator and half-band interpolator, Hilbert transform and interpolated filter implementations

- Support for up to 256 sets of coefficients, with 2 to 2048 coefficients per set

- Input data up to 49-bit precision

- Filter coefficients up to 49-bit precision

- Support for up to 1024 interleaved data channels

- Support for advanced interleaved data channel sequences

- Support for multiple parallel data channels with shared control logic

- Interpolation and decimation factors of up to 64 generally and up to 1024 for single channel filters

- Support for sample frequency greater than clock frequency

- Online coefficient reload capability

- User-selectable output rounding

- Efficient multi-column structures for all filter implementations and optimizations

| LogiCORE IP Facts Table                                  |                                                                                                 |  |  |  |  |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| Core Specifics                                           |                                                                                                 |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup>                | UltraScale+™ Families<br>UltraScale™ Architecture<br>Zynq-7000 All Programmable SoC<br>7 Series |  |  |  |  |

| Supported User<br>Interfaces                             | AXI4-Stream                                                                                     |  |  |  |  |

| Resources                                                | Performance and Resource Utilization web page                                                   |  |  |  |  |

|                                                          | Provided with Core                                                                              |  |  |  |  |

| Design Files                                             | Encrypted RTL                                                                                   |  |  |  |  |

| Example Design                                           | Not Provided                                                                                    |  |  |  |  |

| Test Bench                                               | VHDL                                                                                            |  |  |  |  |

| Constraints File                                         | Not Provided                                                                                    |  |  |  |  |

| Simulation<br>Model                                      | Encrypted VHDL                                                                                  |  |  |  |  |

| Supported<br>S/W Driver                                  | N/A                                                                                             |  |  |  |  |

|                                                          | Tested Design Flows <sup>(2)</sup>                                                              |  |  |  |  |

| Design Entry                                             | Vivado® Design Suite<br>System Generator for DSP                                                |  |  |  |  |

| Simulation                                               | For supported simulators, see the Xilinx Design Tools: Release Notes Guide.                     |  |  |  |  |

| Synthesis                                                | Vivado Synthesis                                                                                |  |  |  |  |

| Support                                                  |                                                                                                 |  |  |  |  |

| Provided by Xilinx at the at the Xilinx Support web page |                                                                                                 |  |  |  |  |

#### Notes:

- For a complete listing of supported devices, see the Vivado IP catalog.

- 2. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

A wide range of filter types can be implemented in the Vivado® Integrated Design Environment (IDE): single-rate, polyphase decimators and interpolators and half-band decimators and interpolators. Structure in the coefficient set is exploited to produce area-efficient FPGA implementations. Sufficient arithmetic precision is employed in the internal datapath to avoid the possibility of overflow.

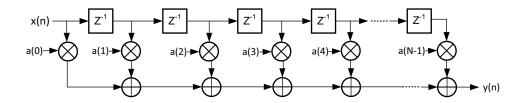

The conventional single-rate FIR version of the core computes the convolution sum defined in Equation 1-1, where N is the number of filter coefficients.

$$y(k) = \sum_{n=0}^{N-1} a(n)x(k-n)$$

$k = 0, 1, ...$  Equation 1-1

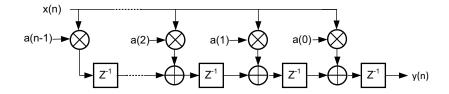

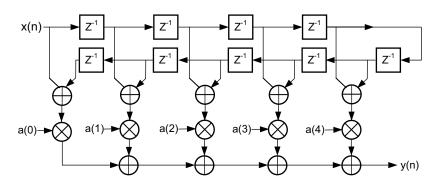

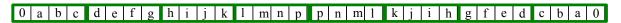

Figure 1-1 shows the conventional tapped delay line realization of this inner-product calculation, and although the illustration is a useful conceptualization of the computation performed by the core, the actual FPGA realization is quite different.

One or more time-shared multiply-accumulate (MAC) functional units are used to service the N sum-of-product calculations in the filter. The core automatically determines the minimum number of MAC engines required to meet user-specified throughput.

Figure 1-1: Conventional Tapped Delay Line FIR Filter Representation

# **Feature Summary**

Table 1-1 and Table 1-2 show the features and filter configuration support for the FIR Compiler.

# **Feature Support Matrix**

Table 1-1: Feature Support Matrix

| Feature                                                    | Systolic<br>Multiply-Accumulate | Transpose<br>Multiply-Accumulate |

|------------------------------------------------------------|---------------------------------|----------------------------------|

| Number of Coefficients                                     | 2–2048                          | 2–2048                           |

| Coefficient Width <sup>(1)</sup>                           | 2–49                            | 2–49                             |

| Data Width <sup>(1)(2)</sup>                               | 2–49                            | 2–49                             |

| Number of Interleaved Channels                             | 1–1024 <sup>(4)</sup>           | 1                                |

| Number of Parallel Data Channels <sup>(3)</sup>            | 1-16                            | 1-16                             |

| Maximum Rate Change<br>Single Channel<br>Multiple Channels | 1024<br>512                     | 1024<br>N/A                      |

| Fractional Rate Support                                    | Yes                             | No                               |

| Coefficient Reload                                         | Yes                             | Yes                              |

| Coefficient Sets                                           | 1–256                           | 1–256                            |

| Output Rounding                                            | Yes                             | Yes                              |

| Super Sample Rate <sup>(5)</sup>                           | Yes                             | No                               |

#### **Notes:**

- 1. Maximum Coefficient Width reduces by one when the Coefficients are signed. Similarly for Maximum Data Width when the Data values are signed.

- 2. The allowable range for the Data Width field in the Vivado IDE might reduce further to ensure that the accumulator width does not exceed the maximum.

- 3. Maximum Parallel Datapaths reduces to 8 when Coefficient Width or Data Width is greater than 25-bits.

- 4. Continuous 1 to 256, plus 512 and 1024.

- 5. Sample frequency greater than clock frequency.

Table 1-2 shows the classes of filters that are supported for the FIR Compiler core.

**Table 1-2:** Filter Configuration Support Matrix

| Filter Configuration             | Supported |

|----------------------------------|-----------|

| Conventional Single-rate FIR     | Yes       |

| Half-band FIR                    | Yes       |

| Hilbert Transform [Ref 1]        | Yes       |

| Interpolated FIR [Ref 2] [Ref 3] | Yes       |

| Polyphase Decimator              | Yes       |

Table 1-2: Filter Configuration Support Matrix (Cont'd)

| Filter Configuration   | Supported |

|------------------------|-----------|

| Polyphase Interpolator | Yes       |

| Half-band Decimator    | Yes       |

| Half-band Interpolator | Yes       |

The supported filter configurations are described in separate sections within this document.

#### **Notable Limitations**

In conjunction with Table 1-1 and Table 1-2, it is important to note some further limitations inherent in the core.

When selecting the Systolic Multiply-Accumulate architecture, the limitations are as follows:

- Fractional Rate filters do not currently exploit coefficient symmetry.

- Non Half-band rate change filters utilizing the advanced channel sequence feature do not exploit coefficient symmetry.

When selecting the Transpose Multiply-Accumulate architecture, the limitations are as follows:

- Symmetry is not exploited.

- Multiple interleaved channels are not supported.

Super sample rate filters (sample frequency greater than clock frequency) have the following limitations:

- Symmetry is only exploited for single rate implementations.

- Fractional rate filters are not supported.

- Half-band optimizations are not exploited.

# **Licensing and Ordering Information**

This Xilinx® LogiCORE™ IP module is provided at no additional cost with the Xilinx Vivado Design Suite under the terms of the Xilinx End User License. Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

# **Performance**

# **Maximum Frequencies**

For details about frequency, visit Performance and Resource Utilization.

# Latency

The core latency is dependent on many of the core parameters. The Implementation Details Tab on the core GUI displays the core latency value, in clock cycles, given the current configuration.

# **Throughput**

The core throughput is completely configurable; from full throughput, one clock cycle per input sample, through to a completely over-sampled implementation. Refer to Hardware Oversampling Specification on the Channel Specification Screen of the core GUI for details.

# **Resource Utilization**

For details about resource utilization, visit Performance and Resource Utilization.

# **Port Descriptions**

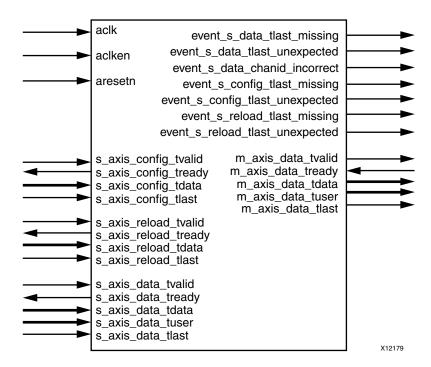

Figure 2-1 shows the schematic symbol for the interface pins for the FIR Compiler core.

Figure 2-1: FIR Compiler Core Pinout

Table 2-1 defines the FIR filter port names and port functional descriptions.

Table 2-1: Core Signal Pinout

| Name                       | Direction | Optional | Description                                                                                                                         |

|----------------------------|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| aclk                       | Input     | no       | Rising-edge clock                                                                                                                   |

| aclken                     | Input     | yes      | Active-High clock enable (optional).                                                                                                |

| aresetn                    | Input     | yes      | Active-Low synchronous clear (optional, always take priority over aclken). A minimum aresetn active pulse of two cycles is required |

| s_axis_config_tvalid       | Input     | yes      | tvalid for CONFIG channel. Asserted by external master to indicate data is available for transfer.                                  |

| s_axis_config_tready       | Output    | yes      | tready for CONFIG channel. Asserted by core to indicate core is ready to accept data.                                               |

| s_axis_config_tdata[A-1:0] | Input     | yes      | tdata for CONFIG channel. See TDATA of CONFIG Channel for internal structure and width.                                             |

| s_axis_config_tlast        | Input     | yes      | tlast for CONFIG channel. Indicates the last transfer of a reconfiguration packet.                                                  |

Table 2-1: Core Signal Pinout (Cont'd)

| Name                 | Direction | Optional | Description                                                                                                                                                                                                                                                     |

|----------------------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| s_axis_reload_tvalid | Input     | yes      | tvalid for RELOAD channel. Asserted by external master to indicate data is available for transfer.                                                                                                                                                              |

| s_axis_reload_tready | Output    | yes      | tready for RELOAD channel. Asserted by core to indicate core is ready to accept data.                                                                                                                                                                           |

| s_axis_reload_tdata  | Input     | yes      | tdata for RELOAD channel. Conveys the coefficient data stream. See TDATA of the RELOAD Channel for internal structure and width.                                                                                                                                |

| s_axis_reload_tlast  | Input     | yes      | tlast for RELOAD channel. Indicates the last transfer of a packet of coefficients.                                                                                                                                                                              |

| s_axis_data_tvalid   | Input     | no       | tvalid for input DATA channel. Asserted by external master to indicate data is available for transfer.                                                                                                                                                          |

| s_axis_data_tready   | Output    | no       | tready for input DATA channel. Asserted by core to indicate core is ready to accept data.                                                                                                                                                                       |

| s_axis_data_tdata    | Input     | no       | tdata for input DATA channel. Conveys the data stream to be filtered. See TDATA Structure for internal structure.                                                                                                                                               |

| s_axis_data_tuser    | Input     | yes      | tuser for input DATA channel. Conveys ancillary data to be passed through the core with latency equal to the input DATA to output DATA datapath and or a chan ID field to identify which Time Division Multiplexed (TDM) channel the current sample belongs to. |

| s_axis_data_tlast    | Input     | yes      | tlast for input DATA channel. This optionally indicates the last of a cycle of TDM channels or can indicate the end of an arbitrary packet in which case it is conveyed to the output with latency equal to the main data stream.                               |

| m_axis_data_tvalid   | Output    | no       | tvalid for output DATA channel. Asserted by core to indicate data is available for transfer.                                                                                                                                                                    |

| m_axis_data_tready   | Input     | yes      | tready for output DATA channel. Asserted by external slave to indicate the slave is ready to accept data.                                                                                                                                                       |

| m_axis_data_tdata    | Output    | no       | tdata for the output DATA channel. This is the filtered data stream. See TDATA Structure for internal structure.                                                                                                                                                |

| m_axis_data_tuser    | Output    | yes      | tuser for the output DATA channel. Optionally conveys a user field from the input DATA tuser port and/or a chan ID field to identify which TDM channel the current sample belongs to.                                                                           |

| m_axis_data_tlast    | Output    | yes      | tlast for the output DATA channel. Optionally indicates the last sample of a cycle of TDM channels (vector framing) or the tlast passed through the core from the input DATA channel (packet framing)                                                           |

Table 2-1: Core Signal Pinout (Cont'd)

| Name                            | Direction | Optional | Description                                                                                                   |

|---------------------------------|-----------|----------|---------------------------------------------------------------------------------------------------------------|

| event_s_data_tlast_missing      | Output    | yes      | Indicates that the input DATA tlast was not asserted when expected by an internal channel counter.            |

| event_s_data_tlast_unexpected   | Output    | yes      | Indicates that the input DATA tlast was asserted when not expected by an internal channel counter.            |

| event_s_data_chanid_incorrect   | Output    | yes      | Indicates that the chan ID field of the input DATA tuser port did not match the value of an internal counter. |

| event_s_reload_tlast_missing    | Output    | yes      | Indicates that the RELOAD tlast was not asserted when expected by an internal counter.                        |

| event_s_reload_tlast_unexpected | Output    | yes      | Indicates that the RELOAD tlast was asserted when not expected by an internal counter.                        |

| event_s_config_tlast_missing    | Output    | yes      | Indicates that the CONFIG tlast was not asserted when expected by an internal counter.                        |

| event_s_config_tlast_unexpected | Output    | yes      | Indicates that the CONFIG tlast was asserted when not expected by an internal counter.                        |

# Designing with the Core

This chapter includes guidelines and additional information to facilitate designing with the core.

# Clocking

The core uses a single clock, aclken, which is common to all the AX4-Stream interfaces and event signals.

The optional clock enable signal, aclken, is used to qualify aclk. When aclken is de-asserted the core state and outputs are halted. Asserting aclken allows the core to continue processing.

## Resets

The aresetn port is an optional active-Low input port which, when asserted for a minimum of two cycles, forces the internal control logic to the initialized condition and optionally clears the data vector of the core. Selecting data vector reset can result in the core using more FPGA logic resources.

When data vector reset has *not* been selected no internal data is cleared from the filter memories during the reset process. The filter output remains dependent on the prior input samples. The data\_valid field of the m\_axis\_data\_tuser bus, see TUSER Options, indicates when the filter data memory has been completely flushed and can be used as additional qualification of the m\_axis\_data\_tdata bus. When the Blank Output option is selected, the filter output is forced to zero until the data\_valid field of m\_axis\_data\_tuser is set (the filter output can be generated from a complete data vector).

# **AXI4-Stream Considerations**

The AXI4-Stream interfaces brings standardization and enhances interoperability of Xilinx® LogiCORE™ IP solutions. Other than general control signals such as aclk, aclken and aresetn and the event outputs, all inputs and outputs to the FIR Compiler are conveyed on AXI4-Stream channels. A channel consists of tvalid and tdata always, plus several optional ports. In the FIR Compiler, the optional ports supported are tready, tlast and tuser. Together, tvalid and tready perform a handshake to transfer a message, where the payload is tdata, tuser and tlast. The FIR Compiler operates on the data contained in the input DATA channel tdata port (s\_axis\_data\_tdata) and outputs the result in the tdata field of the output DATA channel (m axis data tdata). The FIR Compiler optionally uses the tuser and tlast fields to indicate the phase of a cycle of time-multiplexed channels. The core also provides the facility to convey a user field within tuser and the tlast signal from input DATA channel to the output DATA channel with the same latency as for tdata. This facility is intended to ease the use of the FIR Compiler in a system. For example, the FIR Compiler can be used to filter packetized data. In this example, the tlast has no bearing on the FIR, but the core can be configured to pass the tlast of the packetized data channel, saving the system designer the effort of constructing a bypass path for this information.

For further details on AXI4-Stream Interfaces see the Xilinx 7.2 (UG1037)[Ref 4] and the AMBA® AXI4-Stream Protocol Specification (ARM IHI 0051A) [Ref 5].

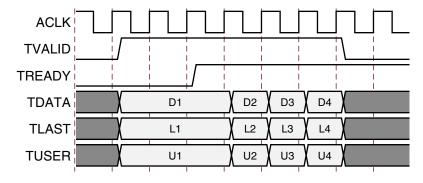

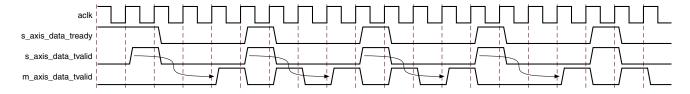

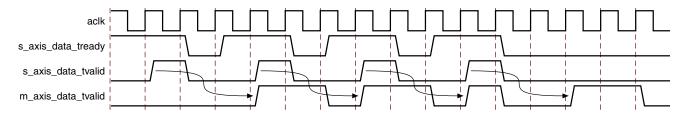

#### **Basic Handshake**

Figure 3-1 shows the transfer of data in an AXI4-Stream channel. tvalid is driven by the source (master) side of the channel and tready is driven by the receiver (slave). tvalid indicates that the value in the payload fields (tdata, tuser and tlast) is valid. tready indicates that the slave is ready to receive data. When both tvalid and tready are TRUE in a cycle, a transfer occurs. The master and slave set tvalid and tready respectively for the next transfer appropriately. Some channels can be configured to have no tready, in which case the channel behaves as through there was an implicit, permanently asserted tready.

Figure 3-1: Data Transfer in an AXI4-Stream Channel

# **Input and Output DATA Channels**

The basic operation of the FIR is for samples to enter through the input DATA channel (s\_axis\_data\_t\*) and exit through the output DATA channel (m\_axis\_data\_t\*) duly filtered. The output channel optionally supports tready which allows a resource/behavior trade-off. In circumstances where downstream slave can be guaranteed to accept the maximum bandwidth of the FIR, tready can be deselected to save resources. The input DATA channel always supports tready.

#### TREADY and TVALID

All AXI4-Stream channels support tvalid. The input DATA channel also always supports tready. The output channel optionally supports tready. Back-pressure from the output channel eventually propagates to the input DATA channel to ensure that no data is dropped.

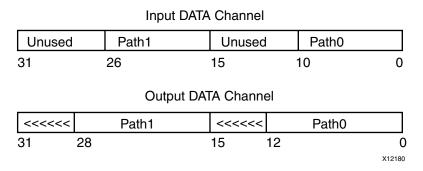

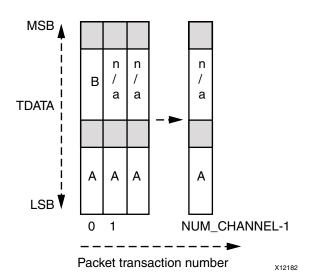

#### TDATA Structure

The input DATA and output DATA channels share a common tdata structure format, though can have different bit widths. All parallel data paths (Parallel Data Channel Filters) and parallel data samples (Super Sample Rate Filters) are contained in the tdata bus, with each path being sign extended to an 8-bit boundary. The extra bits on the input tdata are not used by the core.

Figure 3-2 shows the tdata structure for a case with 2 parallel paths (data streams). In this case, bit growth is experienced between input and output—a path width of 11 bits on the input grows to 13 bits on the output.

Figure 3-2: Tdata Structure for Input and Output DATA Channels

**Note:** The AXI4-Port Structure pane on the Implementation Details Tab of the customization GUI displays the bus structure of all AXI channels for the specified configuration.

#### TLAST Options

On the input DATA channel and output DATA channel, tlast can optionally be used to indicate the last sample in a cycle of interleaved data channels. This use is termed

'vector-based'. The input DATA and output DATA channels also support a mode in which the tlast is passed from input to output with latency equivalent to the tdata samples. This mode is termed 'packet-based' and is intended to ease system design.

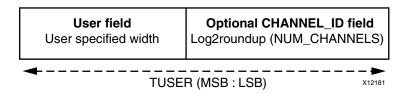

#### **TUSER Options**

The input DATA channel and output DATA channels optionally support a tuser field. For each, the tuser field can be used to convey a User Field and/or a Channel ID field. When both are selected, they are concatenated, with Channel ID in the least significant bit positions. When User Field is selected on the input channel it is automatically selected for the output channel, as this User Field, like 'packet-based' tlast is a facility whereby the User Field is passed through the core, but subject to the same latency delay as the tdata path from input to output. This is intended to ease system design. The User Field has user-selected width.

The Channel ID field has the minimum width required to describe the number of channels in a time-division multiplex cycle (log2roundup(number\_of\_channels)), for example. with 13 channels, channel ID is 4 bits wide.

The output DATA channel also includes a Data Valid field when <code>aresetn</code> has been selected without Data vector reset being selected. This field can be used for additional validation of the <code>m\_axis\_data\_tdata</code> bus. See Resets for more details. The Data Valid field occupies the LSB of <code>m\_axis\_data\_tuser</code> with the other <code>tuser</code> fields, when selected, being shifted up the bus.

Figure 3-3: tuser

When the core has been configured to implement a rate change the following rules are applied to tuser and tlast.

- When the core is configured with no rate change tuser and tlast propagate through the core unmodified.

- When the core is configured to up convert by X the input tuser and tlast are duplicated on the last sample of the corresponding block of X output samples. tuser is undefined for the other X-1 output samples.

- When the core is configured to down convert by X the tuser value for a given output sample is taken from the tuser value of the first input sample of the corresponding X input samples. tlast is OR'd over X input samples with the result being used for the tlast of the corresponding output sample.

#### **CONFIG Channel**

This control channel specifies the filter select value for each (or all) interleaved data channels and the current channel sequence value. It also activates reloaded filter coefficients.

- When the core has been specified to support multiple filter coefficients, the filter select value selects which filter should be used for each of the interleaved data channels.

- When the core has been specified to support advanced channel sequences, the channel pattern value specifies which channel sequence is to be used.

- When the core is specified to support reloadable filter coefficients, receipt of a filter configuration packet updates to (or switches in) any reloaded filter coefficient sets since the previous update.

**Note:** When the core is specified to full rate and no rate change, care must be taken to give the filter an opportunity to acknowledge/store the reloaded filters. If the Filter Configuration Channel is continuously updated, there is no opportunity to store the reloaded filters and the RELOAD channel is blocked when all the reload slots are full. The time required to process a single input vector (block of interleaved channels) is sufficient to update the reload filters.

- The channel can be configured to have a packet of length of *Number of Channels* where each transaction in the packet specifies the filter select value of the corresponding interleaved channel. The first transaction in the packet also includes the channel sequence ID, if required for the core configuration. If the core is configured to support configurable channel sequences but not multiple filter sets, then the packet length is 1.

- The channel can also be configured to have a packet length of 1 where the single transaction specifies the filter select value for all of the interleaved channels. This transaction also includes the channel pattern value, if required for the core configuration.

## **Blocking Behavior**

- The channel is non-blocking to the data channel. The data channel is not halted if no new configuration data is present.

- The channel is blocking to the RELOAD channel. When all the reload slots are full the RELOAD channel is blocked until a configuration packet is received and processed.

## Packet Consumption Rate and Synchronization

When a complete packet has been received you can specify the core to synchronize the CONFIG channel to the input Data channel in two methods:

• **Vector Synchronization (On Vector)**: Configuration packets, when available, are consumed and their contents used when the first sample of an interleaved data channel sequence is processed by the core. When the core is configured to process a single data channel configuration, packets are consumed every processing cycle of the core.

- For down sampling (decimation) implementations configuration packets are only consumed on the first phase of a down sampling period.

- Packet Synchronization (On Packet): Further qualifies the consumption of configuration packets. Packets are only consumed when the core has received a transaction on the S\_AXIS\_DATA channel where s\_axis\_data\_tlast has been asserted or following power up and reset. This option ties the rate at which configuration packets are consumed to the input DATA channel rather than to the rate at which the configuration packets are provided to the core, that is, configuration packets can be queued in advance and then used at a rate controlled by the input DATA channel.

#### **TREADY**

Inputs to the CONFIG channel are stored in a buffer until consumed. When this buffer is almost full, tready is deasserted in accordance with AXI4-Stream protocol.

#### **TLAST Options**

tlast must be asserted to indicate the last transaction in the configuration packet. If the packet is of length 1 then tlast is not required and is disabled. In this case each transaction is considered to be a complete packet. If tlast last is incorrectly asserted a warning is reported on the event interface.

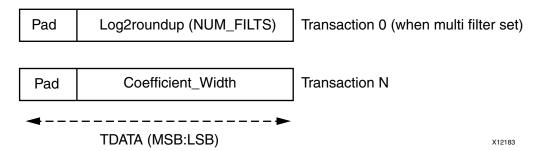

#### **TDATA**

Each field of the tdata bus is zero padded to an 8-bit boundary.

Field A = Filter Select; size log2roundup(NUM\_FILTS)

Field B = Channel pattern; log2roundup(NUM\_PATTERNS).

Figure 3-4: tdata structure for CONFIG channel

#### **RELOAD Channel**

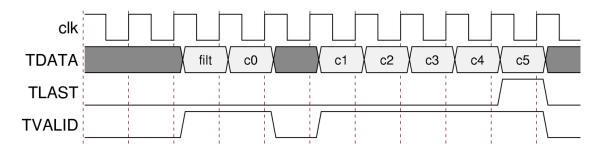

This channel is used to sequentially load a new filter set using a reload packet. A reload packet defines the coefficients of the new filter set and, when multiple filter sets have been selected, the index of the filter set being updated. The filter set index is specified in the range 0 to **Number of Coefficients Set**-1. The **Reload Slots** user parameter specifies how many reload packets can be supplied to the core (the packet queue depth) before a synchronization event occurs. A synchronization event is when the core applies all pending reload packets to the coefficient memory. A synchronization event occurs on the consumption of a configuration packet on the CONFIG channel (S\_AXIS\_CONFIG). Figure 3-7 shows the transaction sequence.

The RELOAD channel packet length is derived from the number of coefficients specified at core generation time and the filter implementation used. See sections Coefficient Reload and Coefficient Reload Tab for details on how to generate the content for the channel. As with the CONFIG channel, the last sample of the packet must be qualified by an asserted tlast. The set of data loaded into the RELOAD channel does not take action until triggered by a reconfiguration synchronization event as described in CONFIG Channel.

#### **TREADY**

When all the reload filter slots are nearly full, tready is deasserted in accordance with AXI4-Stream protocol to prevent data loss.

#### **TLAST**

As with the CONFIG channel, tlast on the RELOAD channel is associated with two event ports (event\_s\_reload\_tlast\_missing and event\_s\_reload\_tlast\_unexpected) which likewise indicate for a single cycle tlast missing or tlast asserted when not expected anomalies respectively.

#### **TDATA**

The tdata bus is zero padded to an 8-bit boundary. As this is an input, the pad bits are ignored.

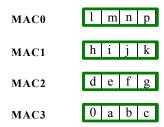

The following diagrams show the format and example timing of tdata into the RELOAD channel. When multiple filter sets have been specified Transaction 0 defines the index of the filter set being reloaded (zero indexed). When a single filter set has been specified this field/transaction is not present in the reload packet. In Figure 3-6 the filter set index (Transaction 0) is labeled as "filt" with the remaining coefficient content labeled "cn". When a single filter set has been specified the "filt" transaction is not present. See Coefficient Reload and Coefficient Reload Tab for details on how to generate the reload packet coefficient content.

Figure 3-5: tdata Format

Figure 3-6: tdata Example Timing

#### **Event Interface**

The event interface is a collection of individual pins, each of which is asserted for a single clock cycle to give external notice of an internal event. These events can be considered as errors or ignored by the external system. The individual event signals are:

event\_s\_data\_tlast\_missing: enabled when tlast is set to vector-based for the input DATA channel; this event signal is asserted on the last transaction of an incoming vector is s\_axis\_data\_tlast is not asserted.

event\_s\_data\_tlast\_unexpected: enabled when tlast is set to vector-based or packet-based when down converting for the input DATA channel; this event signal is asserted on any transaction when s\_axis\_data\_tlast asserted unexpectedly.

event\_s\_data\_chanid\_incorrect: enabled when the tuser mode selects tuser to have a chan ID field; this is asserted on every transaction when the s\_axis\_data\_tuser Channel ID field does not match the value expected by the core.

event\_s\_config\_tlast\_missing: enabled when the CONFIG channel is enabled; this signal is asserted on the last transaction of an incoming vector if s\_axis\_config\_tlast is not seen asserted.

event\_s\_config\_tlast\_unexpected: enabled when the CONFIG channel is enabled, this signal is asserted when s\_axis\_config\_tlast is seen asserted unexpectedly.

event\_s\_reload\_tlast\_missing: enabled when the RELOAD channel is enabled; this signal is asserted on the last transaction of an incoming vector if s\_axis\_config\_tlast is not seen asserted.

event\_s\_reload\_tlast\_unexpected: enabled when the RELOAD channel is enabled; this signal is asserted when s\_axis\_config\_tlast is seen asserted unexpectedly.

# **Interface Timing**

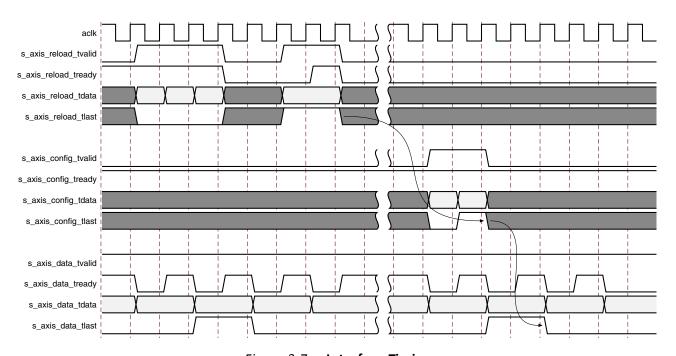

Figure 3-7 shows the sequence of events from a packet of reload data being written to the RELOAD channel (start of first arrow), which is triggered for use on the arrival and consumption of a packet on the CONFIG channel (end of first arrow and start of second arrow), and on to the data stream.

Figure 3-7: Interface Timing

# **Core Features**

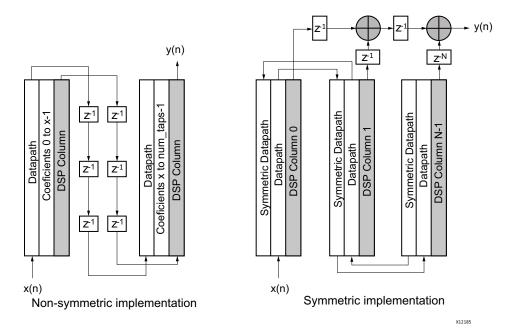

#### **Filter Architectures**

The following sections show the filter architectures available in the FIR Compiler core.

#### Multiply-Accumulate

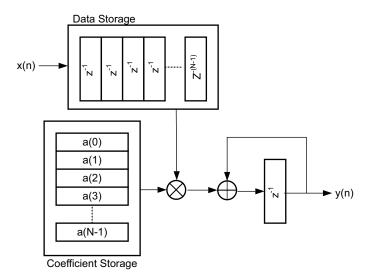

Figure 3-8 shows a simplified view of a Multiply-Accumulate (MAC)-based FIR utilizing a single MAC engine.

Figure 3-8: Single MAC Engine Block Diagram

The single implementation is extensible to multi-MAC implementations for use in achieving higher performance filter specifications (larger numbers of coefficients, higher sample rates, more channels).

The number of multipliers required to implement a filter is determined by calculating the number of multiplies required to perform the computation (taking into account symmetrical and half-band coefficient structures and sample rate changes) and then dividing by the number of clocks available to process each input sample. The available clock cycles value is always rounded down and the number of multipliers rounded up to the nearest integer. If there is a non-zero remainder, some of the MAC engines calculate fewer coefficients than others, and the coefficients are padded with zeros to accommodate the excess cycles.

The output samples reflect the padding of the coefficient vector; for this reason, the response to an applied impulse contains a certain number of zero outputs before the first coefficient of the specified impulse response appears at the output. The core automatically generates an implementation that meets the user-defined performance requirements based on the system clock rate, the sample rate, the number of taps and channels, and the rate change. The core inserts one or more multipliers to meet the overall throughput requirements.

Two MAC architectures are available in the FIR Compiler: one that implements a Systolic filter structure and the other a Transpose filter structure

#### Systolic Multiply-Accumulate

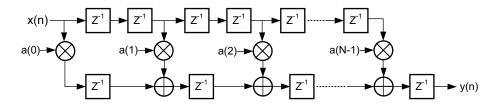

Figure 3-9 shows the Systolic Multiply-Accumulate architecture implementing a pipelined Direct-Form filter.

Figure 3-9: Pipelined Direct - Form

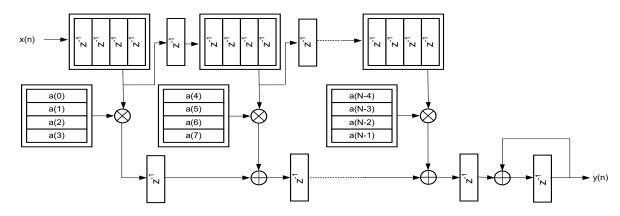

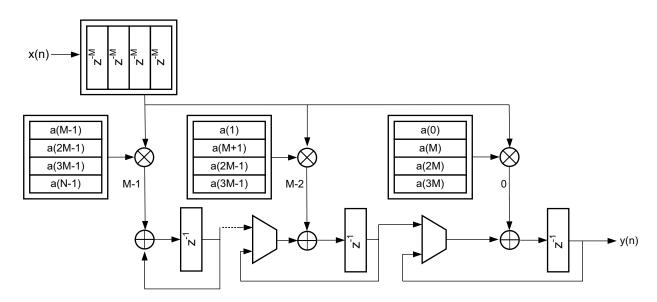

Figure 3-10 shows a multi-MAC implementation for this architecture.

Figure 3-10: Systolic Multi - MAC Implementation

The architecture is directly supported by the DSP Slice and results in area-efficient and high performance filter implementations. The structure also extends to exploit coefficient symmetry, thus providing further resource savings.

# Transpose Multiply-Accumulate

Figure 3-11 shows the Transpose Multiply-Accumulate architecture implementing a Transposed Direct-Form filter.

Figure 3-11: Transpose Direct - Form

Figure 3-12 shows a multi-MAC implementation for this architecture.

Figure 3-12: Transpose Multi - MAC Implementation

This architecture is also directly supported by the DSP Slice. This structure offers a low latency implementation, and for some configurations can also offer extra resource savings over the Systolic structure. It does not require an accumulator and can use fewer data memory resources, although it does not exploit coefficient symmetry.

# **Filter Structures and Optimizations**

This section describes the filters and how to optimize their use in the FIR Compiler.

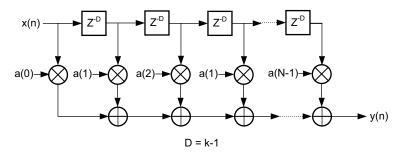

# Filter Symmetry

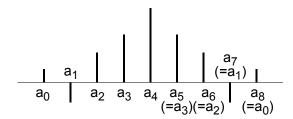

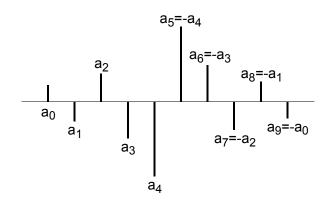

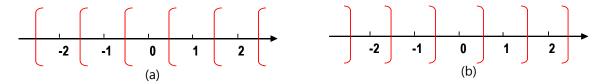

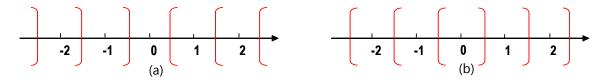

The impulse response for many filters possesses significant symmetry. This symmetry can generally be exploited to minimize arithmetic requirements and produce area-efficient filter realizations. Figure 3-13 shows the impulse response for a 9-tap symmetric FIR filter.

Figure 3-13: Symmetric FIR - Odd Number of Terms

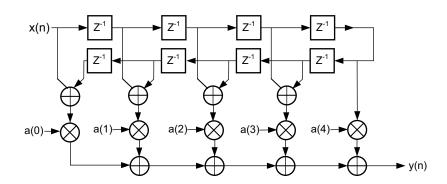

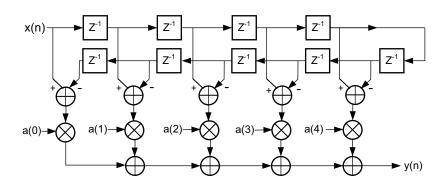

Instead of implementing this filter using the architecture shown in Figure 1-1, the more efficient signal flow-graph in Figure 3-14 can be used. In general, the former approach requires *N* multiplications and (*N*-1) additions. In contrast, the architecture in Figure 3-14

requires only [N/2] multiplications and approximately N additions. This significant reduction in the computation workload can be exploited to generate efficient filter hardware implementations.

Figure 3-14: Exploiting Coefficient Symmetry – Odd Number of Filter Taps

Coefficient symmetry for an even number of terms can be exploited as shown in Figure 3-15.

Figure 3-15: Exploiting Coefficient Symmetry – Even Number of Filter Taps

Figure 3-16 shows the impulse response for a negative, or odd, symmetric filter.

Figure 3-16: Negative Symmetric Impulse Response

This symmetry is exploited in a manner similar to that shown in Figure 3-14 and Figure 3-15. In this case, the middle layer of adders are replaced by subtracters, as shown in Figure 3-17.

Figure 3-17: FIR Architecture Exploiting Negative Symmetry

Filter coefficient symmetry is inferred by the core GUI from the coefficient definition file. You can override this inferred value. When the structure is inferred, the inferred setting is displayed in the Summary page and in the ToolTip for the Coefficient Structure field.

#### **Coefficient Padding**

When implementing a filter with symmetric coefficients using the Multiply-Accumulate architecture, you must be aware that the core reorganizes the filter coefficients if required to exploit symmetry, and this might alter the filter response. This is only necessary if the core is configured such that all processing cycles are not utilized. For example, when the core has four cycles to process each sample for a 30-tap symmetric response filter, the core pads the coefficient storage out as shown in Figure 3-18.

Resultant Impulse Response

Figure 3-18: Filter Padding to Facilitate Symmetric Structure Exploitation

The appended zeroes after the non-zero coefficients do not affect the filter response, but the prepended zero coefficients do alter the phase response of the filter implementation when compared to the ideal coefficients. There are two ways to avoid this issue: First, and

simplest, you can force the Coefficient Structure to be Non-Symmetric. This avoids the issue of prepending zero coefficients to the coefficient vector, and only appended zeroes are used to pad out the filter response to the required number of cycles. Second, and more efficient, you can increase the number of taps implemented by the filter at little or no cost in resource usage. In the previous example, the filter could process 32 taps in the same time, with the same hardware resources, and with the same cycle latency as the 30-tap implementation, and the phase response of the 32-tap filter would be unaltered.

The Vivado IDE displays the actual number of coefficients calculated on the Implementation Details tab. You can use this information to determine if you can increase the number of coefficients used by your filter definition.

#### Single-rate FIR Filter

The basic FIR filter core is a single-rate (input sample rate = output sample rate) finite impulse response filter. This is the simplest of filter types and is the default at the start of parametrization in the Vivado IDE.

#### Half-band FIR Filter

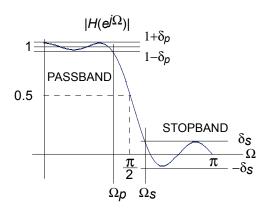

Figure 3-19 shows the general frequency response for a half-band filter.

Figure 3-19: Half-band Filter Magnitude Frequency Response

The magnitude frequency response is symmetrical about quarter sample frequency  $\pi/2$  radians. The sample rate is normalized to  $2\pi$  radians/sec. The passband and stopband frequencies are positioned such that

$$\Omega_p = \pi - \Omega_s$$

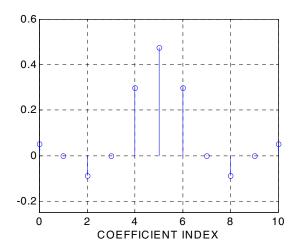

The passband and stopband ripple,  $\delta_p$  and  $\delta_s$  respectively, are equal  $\delta_p = \delta_s$ . These properties are reflected in the filter impulse response. It can be shown (in *Digital Signal Processing in Communication Systems* [Ref 3]) that approximately half of the filter coefficients are zero for an odd number of taps, as shown in Figure 3-20 for an 11-tap half-band filter.

Figure 3-20: Half-band Filter Impulse Response

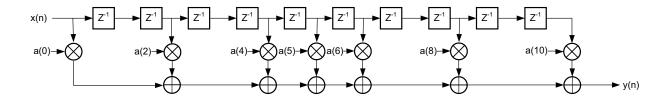

The interleaved zero values in the coefficient data can be exploited to realize an efficient realization, as shown in Figure 3-21. Note that the FIR Compiler also exploits coefficient symmetry for half-band filter structures, although this is not shown in Figure 3-21.

Figure 3-21: Half-band Filter Impulse Response

The half-band filter selection in the compiler is intended for this purpose. This filter is available in the *Coefficient Structure* field of the user interface.

**IMPORTANT:** You must supply the complete list of filter coefficients, including the 0 value samples, when using the half-band filter.

The filter coefficient file format is discussed in greater detail in Filter Coefficient Data.

# Hilbert Transform

Hilbert transformers (see *Digital Signal Processing in Communication Systems* [Ref 3]) are used in several ways in digital communication systems. An ideal Hilbert transform provides a phase shift of 90 degrees for positive frequencies and -90 degrees for negative frequencies. It can be shown (in *Digital Signal Processing in Communication Systems* [Ref 3]) that the impulse response corresponding to this frequency domain characteristic is odd-symmetric and has interleaved zeros as shown in Figure 3-21. Both the alternating zero-valued coefficients and the negative symmetry can be utilized to produce an efficient hardware realization.

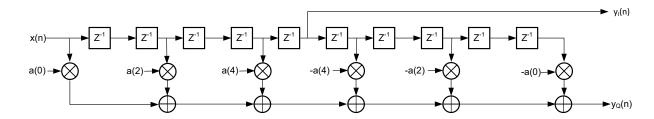

A Hilbert transformer accepts a real-valued signal and produces a complex (I,Q) output signal. The quadrature (Q) component of the output signal is produced by a FIR filter with an impulse response like that shown in Figure 3-22. The in-phase (I) component is the input signal delayed by an appropriate amount to compensate for the phase delay of the FIR process employed for generating the Q output. This is efficiently achieved by accessing the center tap of the sample history delay of the Q channel FIR filter as shown in Figure 3-23. In this figure, x(n) is the real-valued input signal, and  $y_I(n)$  and  $y_Q(n)$  are the in-phase and quadrature outputs, respectively.

Figure 3-22: Hilbert Transformer Impulse Response

Figure 3-23: Hilbert Transformer FIR Filter Realization

Figure 3-24 shows the architecture for a Hilbert transformer that exploits both the zero-valued and the negative symmetry characteristics of the impulse response.

Figure 3-24: Hilbert Transformer Exploiting Zero-valued Filter Coefficients and Negative Symmetry

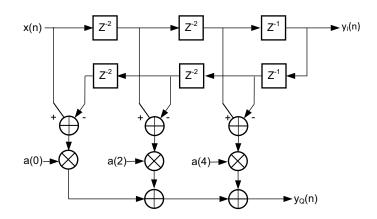

#### Interpolated FIR Filter

An interpolated FIR (IFIR) filter (see Multi-Rate Systems and Filter Banks [Ref 2]) has a similar architecture to a conventional FIR filter, but with the unit delay operator replaced by k-1 units of delay. k is referred to as the zero-packing factor. Figure 3-25 shows a N-tap IFIR filter. This architecture is functionally equivalent to inserting k-1 zeros between the coefficients of a prototype filter coefficient set.

Figure 3-25: Interpolated FIR (IFIR) - Zero-packing Factor is k

Interpolated filters are useful for realizing efficient implementations of both narrow-band and wide-band filters. A filter system based on an IFIR approach requires not only the IFIR but also an image rejection filter. References, *Multi-Rate Systems and Filter Banks* [Ref 2] and *XtremeDSP Design Manual* [Ref 6] provide the details of how these systems are realized, and how to design the IFIR and the image rejection filters.

The IFIR filter implementation takes advantage of the k-1 zeros in the impulse response to realize an area-efficient FPGA implementation. The FPGA area required by an IFIR filter is not a strong function of the zero-packing factor.

The interpolated FIR should not be confused with an interpolation filter. Interpolated filters are single-rate systems employed to produce efficient realizations of narrow-band filters and, with some minor enhancements, wide-band filters can be accommodated. There is no inherent rate change when using an interpolated filter – the input rate is the same as the output rate.

#### **Polyphase Decimator**

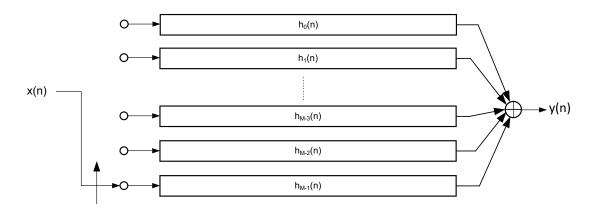

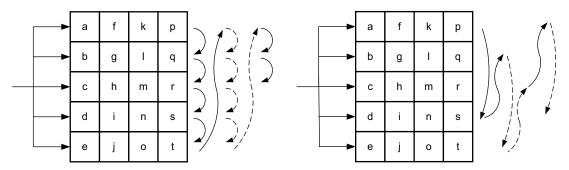

Figure 3-26 shows the polyphase decimation filter option which implements the computationally efficient *M*-to-1 polyphase decimating filter.

Figure 3-26: M-to-1 Polyphase Decimating Filter

A set of N prototype filter coefficients  $a_0, a_1, ..., a_{N-1}$  is mapped to the M polyphase subfilters  $h_0(n), h_1(n), ..., h_{M-1}(n)$  according to Equation 3-1.

$$h_i(r) = a(i + Mr)$$

$i = 0, 1, ..., M-1$   $r = 0, 1, ..., \frac{N}{M}$  Equation 3-1

The polyphase segments are accessed by delivering the input samples x(n) to their inputs using an input commutator which starts at the segment index i = M-1 and decrements to index 0. After the commutator has executed one cycle and delivered M input samples to the filter, a single output is taken as the summation of the outputs from the polyphase segments. The output sample  $f_s'$  rate is  $f_s' = \frac{f_s}{M}$  where  $f_s$  is the sample rate of the input data stream  $f_s(n)$ ,  $f_s(n)$  and  $f_s(n)$  where  $f_s(n)$  is the sample rate of the input data stream  $f_s(n)$  and  $f_s(n)$  are  $f_s(n)$  and  $f_s(n)$  are  $f_s(n)$  are  $f_s(n)$  are  $f_s(n)$  are  $f_s(n)$  and  $f_s(n)$  are  $f_s(n)$  are  $f_s(n)$  and  $f_s(n)$  are  $f_s(n)$  are  $f_s(n)$  and  $f_s(n)$  are  $f_s(n)$  and  $f_s(n)$  are  $f_s(n)$  are  $f_s(n)$  and  $f_s(n)$  are  $f_s(n)$  and  $f_s(n)$  are  $f_s(n)$  and  $f_s(n)$  are  $f_s(n)$  are  $f_s(n)$  and  $f_s(n)$  are  $f_s(n)$  and  $f_s(n)$  are  $f_s(n)$  are  $f_s(n)$  and

Observe that each of the polyphase segments is operating at the low output sample rate  $f_s'$  (compared to the high input sample rate  $f_s$ ), and a total of N operations is performed per output point.

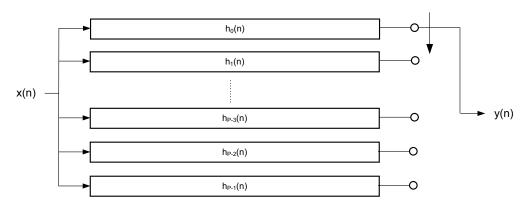

#### Polyphase Interpolator

Figure 3-27 shows the polyphase interpolation filter option which implements the computationally efficient 1-to-*P* interpolation filter.

Figure 3-27: 1-to-P Polyphase Interpolator

A set of N prototype filter coefficients  $a_0, a_1, ..., a_{N-1}$  is mapped to the P polyphase subfilters  $h_0(n), h_1(n), ..., h_{p-1}(n)$  according to Equation 3-1, as in the decimation case.

Each new input sample x(n) engages all of the polyphase segments in parallel. For each input sample delivered to the filter, P output samples, one from each segment, are delivered to the filter output port, as indicated by the commutator in Figure 3-27.

The output sample  $f'_s$  rate is  $f'_s = f_s P$  where  $f_s$  is the sample rate of the input data stream f(n), f(n), f(n) observe each of the polyphase segments operating at the low input sample rate  $f_s$  (compared to the high output sample rate  $f'_s$ ) and a total of f'(n) operations performed per output point.

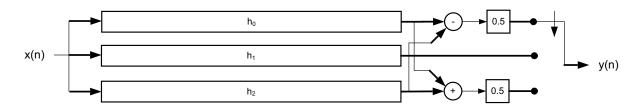

#### **Polyphase Interpolator Exploiting Symmetric Pairs**

The symmetric pairs technique (see Symmetry Exploitation in Digital Interpolators/ Decimators [Ref 7]) is used to exploit coefficient symmetry when implementing an Interpolation filter in the Systolic Multiply-Accumulator architecture. When P polyphase subfilters are generated from symmetric filter coefficients, not all the subfilters contain a set of coefficients that are themselves symmetric. The symmetric pairs technique observes that adding and subtracting two corresponding non-symmetric phases produces two new phases containing symmetric coefficients.

The following example demonstrates this technique for a 15-tap interpolate by 3 filter. The filter coefficients, a, b, c, d, e, f, g, h, g, f, e, d, c, b, a produce the following subfilters:

$$h_0 = a, d, g, f, c$$

$$h_1 = b, e, h, e, b$$

$$h_2 = c, f, g, d, a$$

Subfilters  $h_0$  and  $h_2$  are not symmetric. Applying the symmetric pairs technique produces the following subfilters:

$$h_0 = a+c, d+f, d,g, f+d, c+a$$

$$h_1 = b, e, h, e, b$$

$$h_2 = c-a, f-d, g-g, d-f, a-c$$

Now both  $h_0$  and  $h_2$  are symmetric with  $h_2$  being negative symmetric. The filter can now be implemented utilizing symmetry, giving the associated resource savings. The output from subfilters  $h_0$  and  $h_2$  must be added and subtracted and then scaled by a factor of 0.5 to produce the original filter output. Figure 3-28 shows the resulting structure.

Figure 3-28: Symmetric Pairs

**Note:** For some configurations an extra DSP Slice is required to implement the recombination of the phases.

**Note:** When interpolating by 2 with an odd number of symmetric coefficients, this technique is not required as the resulting polyphase subfilters are symmetric.

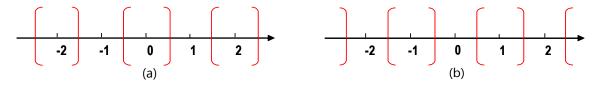

#### **Coefficient Padding**

As with the general symmetric filter case, if the combination of rate and number of filter taps results in a subfilter which is not fully populated with coefficients, the reorganization of the filter coefficients results in a change in the phase response of the filter. The impulse response is shifted by several output samples as a result. In the 14 tap, interpolate by 4 case, padding a zero coefficient to the front of the coefficient response would be required to align the phases such that symmetry can be exploited, resulting in a smaller implementation, but this results in a different phase response for the filter. The methods to avoid this change in response, if such a change cannot be accommodated in your application system, are also similar to the general symmetry case; you can either force non-symmetric structure implementation or make use of the extra coefficients which can be supported in the structure. Figure 3-29 shows several example cases in and is extensible to larger filters.

# Symmetric Pair 21 taps, Interpolate by 3 21 taps, Interpolate by 3 (no padding) Symmetric Pair Even Sym Define a d g i i f c Even Sym Define Symmetric Pair Symmetric Pair

Figure 3-29: Filter Padding to Facilitate Symmetric Pairing

#### **Half-band Decimator**

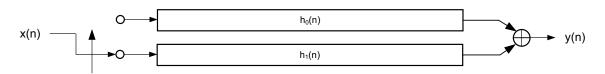

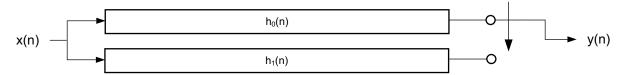

The half-band decimator is a polyphase filter with an embedded 2-to-1 down-sampling of the input signal. Figure 3-30 shows the structure.

Figure 3-30: Half-band Decimation Filter

The filter is very similar to the polyphase decimator described in Polyphase Decimator with the decimation factor set to M=2. However, there is a subtle difference in the implementation that makes the half-band decimator a more area-efficient 2-to-1 down-sampling filter when the frequency response reflects a true half-band characteristic.

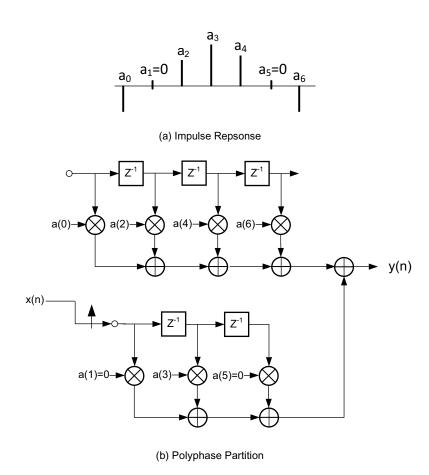

The frequency and time response of a half-band filter are shown in Figure 3-19 and Figure 3-20, respectively. Observe the alternating zero-valued coefficients in the impulse response. Figure 3-30 details a 7-tap half-band polyphase filter when the coefficients are

allocated to the two polyphase segments  $h_0(n)$  and  $h_1(n)$  shown in Figure 3-30. Figure 3-31 (a) is the filter impulse response ( $a_1 = 0 = a_5$ ). Figure 3-31 (b) provides a detailed illustration of the polyphase subfilters and shows how the filter coefficients are allocated to the two polyphase arms.

In the bottom arm,  $h_1(n)$ , the only non-zero coefficient, is the center value of the impulse response  $a_3$ . Figure 3-31 (c) shows the optimized architecture when the redundant multipliers and adders are removed and coefficient symmetry is exploited. The final structure has a reduced computation workload in contrast to a more general 2:1 down-sampling filter.

The number of multiply-accumulate (MAC) operations required to compute an output sample has been lowered by a factor of approximately two. In this figure, the high density of zero-valued filter coefficients is exploited in the FPGA realization to produce a minimal area implementation.

Figure 3-31: 7-Tap Half-band Decimation Filter

(c) Reduced Complexity (Hardware Optimized) Realization

Figure 3-31: 7-Tap Half-band Decimation Filter

#### Half-band Interpolator

Just as the half-band decimator is an optimized version of the more general polyphase decimation filter, the half-band interpolator is a special case of a polyphase interpolator. Figure 3-32 shows the half-band interpolator.

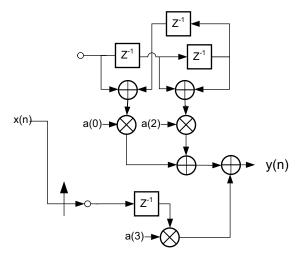

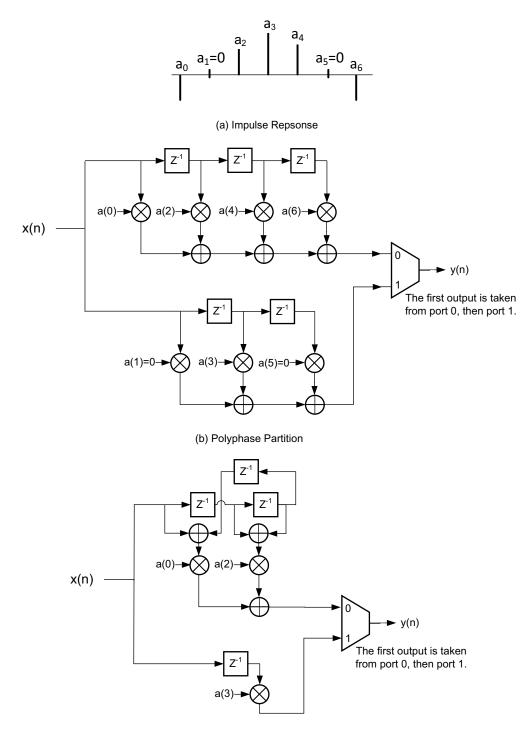

Figure 3-32: Half-band Interpolation Filter

The coefficient set for a true half-band interpolator is identical to that of a half-band decimator with the same specifications. The large number of zero entries in the impulse response is exploited in exactly the same manner as with the half-band decimator to produce hardware-optimized half-band interpolators. The process is presented in Figure 3-33. Figure 3-33(a) is the impulse response, Figure 3-33(b) shows the polyphase partition, and Figure 3-33(c) is the optimized architecture that has taken full advantage of the 0 entries in the coefficient data, along with coefficient symmetry.

The high density of zero-valued filter coefficients is exploited in the FPGA realization to produce a minimal area implementation.

(c) Reduced Complexity (Hardware Optimized) Realization

Figure 3-33: 7-Tap Half-band Interpolation Filter

## Small Non-zero Even Terms in a Half-band Filter Impulse Response

Certain filter design software can result in small non-zero values for the odd terms in the half-band filter impulse response. In this situation, it can be useful to force these values to

0 and re-evaluate the frequency response to assess if it is still acceptable for the intended application. If the odd terms are not identically zero, the hardware optimizations described previously are not possible. If the small non-zero value terms cannot be ignored, the general polyphase decimator or interpolator described in Polyphase Decimator and Polyphase Interpolator, using a rate change of two, is more appropriate.

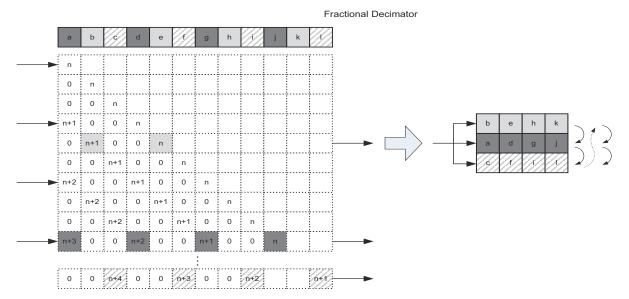

#### **Fixed Fractional Rate Resampling Filters**

FIR filters that implement resampling of a data stream at a fixed fractional rate P/Q, where P and Q are integers up to 64, are available for the Systolic Multiply-Accumulate architecture. In Figure 3-34, the operation of an interpolation filter with interpolation rate P=5 is contrasted conceptually with the operation of a fixed fractional rate filter with rate P/Q=5/3.

Figure 3-34: Interpolation Filters for Integer and Fractional Rates

The normal (integer rate) interpolator passes the input sample to all P phases and then produces an output from each of the phase arms of the polyphase filter structure. In the fractional rate version, the output is taken from a phase arm which varies according to a stepping sequence with step size Q.

Figure 3-35 illustrates how the fractional rate decimator structure is implemented for a rate change of P/Q = 3/5. Input samples are fed into the data vector until enough samples are received to generate the current output given the interpolation and decimation rate. In this example, two new input samples are required to generate the first two outputs, with the third output requiring only a single input. To generate each output, the data vector samples are applied to the corresponding coefficients.

Figure 3-35: Decimation Filter for Fractional Rates

Symmetry is not currently exploited when using the fractional rate structures.

### **Filter Coefficient Data**

The filter coefficients are supplied to the FIR Compiler using a coefficient file with a .coe extension. This is an ASCII text file with a single-line header that defines the radix of the number representation used for the coefficient data, followed by the coefficient values themselves. This is shown in Figure 3-36 for an *N*-tap filter.

```

radix=coefficient_radix;

coefdata=

a(0),

a(1),

a(2),

...

a(N-1);

```

Figure 3-36: Filter Coefficient File Format

The filter coefficients can be supplied as integers in either base-10, base-16, or base-2 representation. This corresponds to *coefficient\_radix*=10, *coefficient\_radix*=16, and *coefficient\_radix*=2 respectively. Alternatively, the coefficients can be entered as real numbers (specified to a minimum of one decimal place) in base-10 only. If you enter signed negative symmetric hexadecimal coefficients, each value should be sign-extended to the boundary of the most significant nibble or hex character. This ensures that coefficient structure inference can be performed correctly (this includes Hilbert transform filter types, which are also negative symmetric).

The coefficient values can also be placed on a single line as shown in Figure 3-37.

```

radix=coefficient_radix;

coefdata=a(0),a(1),a(2),...,a(N-1);

```

Figure 3-37: Filter Coefficient File Format – Coefficient Data on a Single Line

### Single-rate FIR

The coefficient file for the single-rate FIR filter is straightforward and consists of a one-line header followed by the filter coefficient data. For example, the filter coefficient file for an 8-tap filter using a base-10 representation for the coefficient values is shown in Figure 3-38:

```

radix=10;

coefdata=20,-256,200,255,255,200,-256,20;

```

Figure 3-38: Filter Coefficient File – 8-Tap Filter, Base-10 Coefficient Values

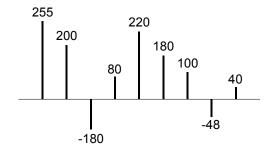

Irrespective of the filter possessing positive or negative symmetry, the coefficient file should contain the complete set of coefficient values. The filter coefficient file for the non-symmetric impulse response shown in Figure 3-39 is presented in Figure 3-40.

Figure 3-39: Non-symmetric Impulse Response

```

radix=10;

coefdata=255,200,-180,80,220,180,100,-48,40;

```

Figure 3-40: Coefficient File for the Non-symmetric Impulse Response

The coefficient file for the negative-symmetric filter characterized by the impulse response in Figure 3-41 is shown in Figure 3-42.

Figure 3-41: Negative Symmetric Impulse Response

```

radix=10;

coefdata=30,-40,80,-100,-200,200,100,-80,40,-30;

```

Figure 3-42: Coefficient File for the Negative Symmetric Impulse Response

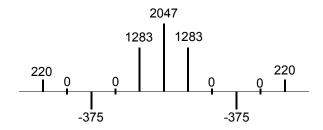

#### **Half-band Filter**

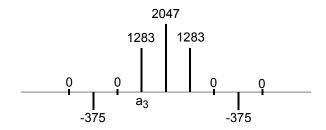

As previously described, every second filter coefficient for a half-band filter with an odd number of terms is zero. When specifying the filter coefficient data for this filter class, the zero value entries must be included in the coefficient file. For example, the filter coefficient file that specifies the filter impulse response in Figure 3-43 is shown in Figure 3-44.

Figure 3-43: 11-Tap Half-band Filter Impulse Response

```

radix=10;

coefdata=220,0,-375,0,1283,2047,1283,0,-375,0,220;

```

Figure 3-44: Coefficient File for the Half-band Filter Impulse Response

The filter coefficient set is parsed by the FIR Compiler. If either the alternating zero entries are absent or the coefficient set is not even-symmetric, this condition is flagged as an error and the filter is not generated. A dialog box is presented to indicate the issue under these circumstances.

Technically, the zero-valued entries for a half-band filter can occur at the filter impulse response extremities as shown in Figure 3-45. However, observe that these values do not contribute to the result.

Figure 3-45: 9-Tap Half-band Filter Impulse Response

This condition is detected when the filter is specified. If the number of taps is such that the zero-valued coefficients form the first and last entry of the impulse response, the filter length is reported as an invalid value. The number of taps N for a half-band filter must obey N=3+4n, where n=0,1,2,3,... For example, a half-band filter can have 11, 15, 19, and 23 taps, but not 9, 13, 17, or 21 taps.

### **Hilbert Transform**

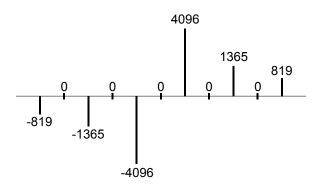

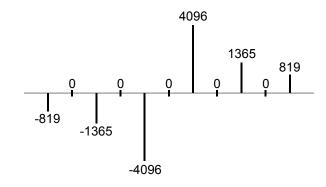

The impulse response for a 10-term approximation to a Hilbert transformer is shown in Figure 3-46. The odd-symmetry and zero-valued coefficients are both exploited to generate an efficient FPGA realization. The coefficient data file for the Hilbert transform must contain the zero-valued entries. For example, the .coe file corresponding to Figure 3-46 is shown in Figure 3-47.

Figure 3-46: Hilbert Transform Impulse Response

radix=10; coefdata=-819,0,-1365,0,-4096,0,4096,0,1365,0,819;

Figure 3-47: Coefficient File for the Hilbert Transformer Impulse Response

In practice, some optimization methods used for designing a Hilbert transform can lead to the presence of small even-numbered coefficients. If the *Hilbert Transform* filter class is used in the FIR Compiler, you must force these terms to zero.

Just like the half-band filter, the zero-valued entries for a Hilbert transformer can occur at the filter impulse response extremities. However, these values do not contribute to the result.

This condition is detected when the filter is specified. If the number of taps is such that the zero-valued coefficients form the first and last entry of the impulse response, the filter length is reported as an invalid value. The number of taps N for a Hilbert transformer must obey N=3+4n, where n=0,1,2,3,... For example, a Hilbert transform filter can have 11, 15, 19, and 23 taps, but not 9, 13, 17, or 21 taps.

### **Interpolated Filter**

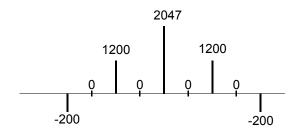

A previous section explained that an IFIR filter is similar to a conventional FIR, but with the unit delay operator replaced by k-1 units of delay. k is referred to as the zero-packing factor. One way to realize this substitution is by the insertion of k-1 zeros between the coefficient values of a prototype filter. When specifying an IFIR architecture, the full set of prototype coefficients is supplied in the coefficient file, without the zeros implied by the zero-packing factor. The zero-packing factor is defined through the filter user interface. For example, consider the filter coefficient data in the .coe file shown in Figure 3-48.

```

radix=10;

coefdata=-200,1200,2047,1200,-200;

```

Figure 3-48: Prototype Coefficient Data for IFIR Example

If a zero-packing factor of k=2 is specified, the equivalent filter impulse response is shown in Figure 3-49.

Figure 3-49: Equivalent IFIR Impulse Response for the Coefficient Data Shown in Figure 3-48 with a Zero-packing Factor k=2

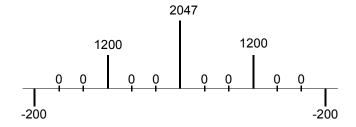

If the zero-packing factor is changed to k=3, the impulse response is as shown in Figure 3-50.

Figure 3-50: Equivalent IFIR Impulse Response for the Coefficient Data Shown in Figure 3-48 with a Zero-packing Factor k=3

These examples use a symmetrical prototype impulse response; this is not a restriction of the filter core. The prototype filter coefficient set can be symmetrical, non-symmetrical, or negative-symmetric.

### Multiple Coefficient Sets

For multiple coefficient filters, a single .coe file is used to specify the coefficient sets. Each coefficient set should be appended to the previous set of coefficients.

For example, if a 2-coefficient set, 10-tap symmetric filter was being designed and coefficient set #0 was: coeff data = -1, -2, -3, 4, 5, 5, 4, -3, -2, -1;

and coefficient set #1 was:

then the .coe file for the entire filter would be:

All coefficients sets in a multiple set implementation must exhibit the same symmetry. For example, if even one set of a multi-set has non-symmetric coefficient structure, then all sets are implemented using that structure. All coefficient sets must also be of the same vector length. If one coefficient set has fewer coefficients, it must be zero padded – either appended with zeros when non-symmetric or prepended and appended with an equal number of zeros when symmetric. See the Coefficient Padding section for further information.

### **Coefficient Specification Using Non-integer Real Numbers**

As indicated previously, you can specify the coefficient values as non-integer real numbers, with the radix set to 10. For example:

```

radix = 10;

coefdata = 0.08659436542927, 0.00579513928555, -0.06734424313287,

-0.04031582111240;

```

The coefficients are then quantized by the core to produce the binary coefficient values used in the filter, based on your specified coefficient bit width. This allows you to supply floating-point values derived from a chosen filter design tool and explore the costs and benefits between performance and resource usage by altering the coefficient bit width and observing the alteration in the quantified frequency response in comparison to the ideal response. The basic quantization function is selected by setting the Quantization field to Quantize\_Only. See Coefficient Quantization for further details.

The integer values used in the filter implementation can be determined by examining the main core MIF file (<component\_name>.mif) which is generated in the project directory. The MIF file is always in binary format.

#### Interleaved Data Channel Filters

The FIR Compiler core provides support for processing multiple input sample streams using the same implementation. Each input stream is filtered using the same filter configuration (rate change, etc.) using the currently selected filter coefficient set.

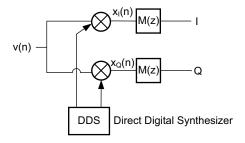

In many applications, the same filter must be applied to several data streams. A common example is the simple digital down converter shown in Figure 3-51. Here a complex base-band signal  $(n) = x_l(n) + jx_Q(n)$  is applied to a matched filter M(z). The in-phase and quadrature components are processed by the same filter.

Figure 3-51: Digital Down Converter

One solution to this issue is to employ two separate filters; however, this can waste logic resources. A more efficient design can be realized using a filter architecture that shares logic resources between multiple time division multiplexed (TDM) sample streams. As more channels are processed by the core, the sample throughput is commensurately reduced. For

example, if the sample rate for a single-channel filter is  $f_s$ , a two-channel version of the same filter processes two sample streams, each with a sample rate of  $f_s/2$ . A three-channel version of the filter processes three data streams and supports a sample rate of  $f_s/3$  for each of the streams.

A multichannel filter implementation is very efficient in resource utilization. A filter with two or more channels can be realized using a similar amount of logic resources to a single-channel version of the same filter, with proportionate increase in data memory requirements. The trade-off that needs to be addressed when using multichannel filters is one of sample rate versus logic requirements. As the number of channels is increased, the logic area remains approximately constant, but the sample rate for an individual input stream decreases. The number of channels supported by a filter core is specified in the filter Customize IP dialog box. The FIR Compiler supports two multichannel implementation: Basic and Advanced.

#### Basic

The basic implementation processes interleaved data channels sequentially; channel 0, channel 1, channel 2, ..., channel N-1, where N=N = Number of Channels. This implementation uses minimal resources.

#### **Advanced**

The advanced implementation provides a list of predefined interleaved data channel sequences, or patterns, from which multiple patterns can be selected during core customization. The specified patterns can then be selected during core operation using the CONFIG Channel.

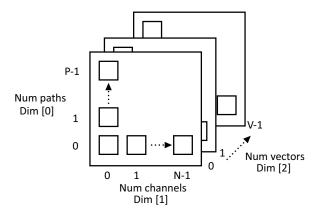

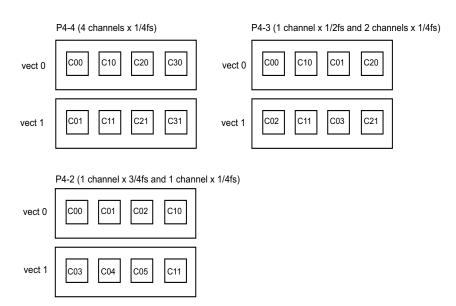

When the core is configured to support one channel with a sample frequency of  $f_S$  the same hardware resources (DSP Slice and Memory) can support two channels with a sample frequency of  $f_S/2$ , 4 channels with a sample frequency of  $f_S/4$  or 1 channel with a sample frequency  $f_S/2$  and 2 channels with a sample frequency  $f_S/4$ . The Advanced implementation supports each of these configurations with an associated interleaved channel sequence that can then be selected, dynamically, during core operation through the CONFIG Channel.

**IMPORTANT:** Switching between channel sequences causes the data vector of all channels to be cleared/reset.

Table 3-1 lists all the supported interleaved channel patterns. The full pattern list is also displayed on the Vivado IDE.

Although the hardware resources (DSP Slice and Memory) remain the same as the equivalent Basic implementation, the Advanced Implementation requires additional logic resources. For the patterns highlighted in Table 3-1, the memory requirements might also increase and further logic resources might be required.

Table 3-1: Advanced Interleaved Data Channel Patterns

| No.<br>Chans. | Seq.<br>ID | Description                                                       | Interleaved Channel Pattern |

|---------------|------------|-------------------------------------------------------------------|-----------------------------|

| 4             | P4-0       | 1 Channel at fs                                                   | 0000                        |

| 4             | P4-1       | 2 Channels at 1/2fs                                               | 0 1 0 1                     |

| 4             | P4-2       | 1 Channel at 3/4fs,<br>1 Channel at 1/4fs                         | 0 0 0 1                     |

| 4             | P4-3       | 1 Channel at 1/2fs,<br>2 Channels at 1/4fs                        | 0102                        |

| 4             | P4-4       | 4 Channels at 1/4fs                                               | 0123                        |

| 6             | P6-0       | 1 Channel at fs                                                   | 00000                       |

| 6             | P6-1       | 2 Channels at 1/2fs                                               | 010101                      |

| 6             | P6-2       | 1 Channel at 2/3fs,<br>1 Channel at 1/3fs                         | 000011                      |

| 6             | P6-3       | 3 Channels at 1/3fs                                               | 012012                      |

| 6             | P6-4       | 1 Channel at 2/3fs,<br>2 Channels at 1/6fs                        | 000012                      |

| 6             | P6-5       | 1 Channel at 1/2fs,<br>3 Channels at 1/6fs                        | 010203                      |

| 6             | P6-6       | 2 Channels at 1/3fs,<br>2 Channels at 1/6fs                       | 012013                      |

| 6             | P6-7       | 1 Channel at 1/3fs,<br>3 Channels at 1/6fs                        | 012034                      |

| 6             | P6-8       | 6 Channels at 1/6fs                                               | 0 1 2 3 4 5                 |

| 8             | P8-0       | 1 Channel at fs                                                   | 0 0 0 0 0 0 0               |

| 8             | P8-1       | 1 Channel at 3/4fs,<br>1 Channel at 1/4fs                         | 0000011                     |

| 8             | P8-2       | 2 Channels at 1/2fs                                               | 01010101                    |

| 8             | P8-3       | 1 Channel at 3/4fs,<br>2 Channels at 1/8fs                        | 0000012                     |

| 8             | P8-4       | 1 Channel at 1/2fs,<br>2 Channels at 1/4fs                        | 01020102                    |