# **The Reconfigurable Cluster Element**

An I/O System On Chip

# **Cluster Element (CE) User Guide**

Document Version: Document Issue: Document Edition: Document Status: Document ID: Document Date: 0.9 3 English First release to reviewers XXX-TD-xxxxx December 18, 2008

This document has been prepared using the Software Documentation Layout Templates that have been prepared by the IPT Group (Information, Process and Technology), IT Division, CERN (The European Laboratory for Particle Physics). For more information, go to http://framemaker.cern.ch/.

# Abstract

To be written.

# Hardware compatibility

This document assumes the following hardware revisions: TBD.

# Intended audience

TBW.

# **Conventions used in this document**

Certain special typographical conventions are used in this document. They are documented here for the convenience of the reader:

- Field names are shown in bold and italics (*e.g.*, *respond* or *parity*).

- Acronyms are shown in small caps (*e.g.*, SLAC or CDS).

- Hardware signal or register names are shown in Courier bold (*e.g.*, RIGHT\_FIRST or LAYER\_MASK\_1)

# References

- 1 Preliminary Product Specification of the *Xilinx* Virtex-4 Family Overview, dated June 17, 2005

- 2 *Infiniband* Architecture Specification Volume 1, Release 1.2. Dated October 2004 (final release).

- 3 *Xilinix* Virtex-4 Family Overview, Preliminary Product specification, dated February 10, 2006

# **Document Control Sheet**

| Table 1 | Document | Control Sheet |

|---------|----------|---------------|

|---------|----------|---------------|

| Document   | Title:               | The Reconfigurable Cluster                 | The Reconfigurable Cluster Element Cluster Element (CE) User Guide |                    |  |  |  |  |  |  |  |

|------------|----------------------|--------------------------------------------|--------------------------------------------------------------------|--------------------|--|--|--|--|--|--|--|

|            | Version:             | 0.9                                        |                                                                    |                    |  |  |  |  |  |  |  |

|            | Issue:               | 3                                          |                                                                    |                    |  |  |  |  |  |  |  |

|            | Edition:             | English                                    |                                                                    |                    |  |  |  |  |  |  |  |

|            | ID:                  | XXX-TD-xxxxx                               |                                                                    |                    |  |  |  |  |  |  |  |

|            | Status:              | First release to reviewers                 |                                                                    |                    |  |  |  |  |  |  |  |

|            | Created:             | February 9, 2002                           |                                                                    |                    |  |  |  |  |  |  |  |

|            | Date:                | December 18, 2008                          |                                                                    |                    |  |  |  |  |  |  |  |

|            | Access:              | Z:\Private\DTK\RCE\UG\V5\frontmatter.fm    |                                                                    |                    |  |  |  |  |  |  |  |

|            | Keywords:            | CSC ROD                                    |                                                                    |                    |  |  |  |  |  |  |  |

| Tools      | DTP System:          | Adobe FrameMaker                           | Version:                                                           | 6.0                |  |  |  |  |  |  |  |

|            | Layout<br>Template:  | Software Documentation<br>Layout Templates | Version:                                                           | V2.0 - 5 July 1999 |  |  |  |  |  |  |  |

|            | Content<br>Template: |                                            | Version:                                                           |                    |  |  |  |  |  |  |  |

| Authorship | Coordinator:         | Michael Huffer, SLAC                       |                                                                    |                    |  |  |  |  |  |  |  |

|            | Written by:          | Michael Huffer                             |                                                                    |                    |  |  |  |  |  |  |  |

|            | Reviewed by:         | N/A                                        |                                                                    |                    |  |  |  |  |  |  |  |

|            | Approved by:         | N/A                                        |                                                                    |                    |  |  |  |  |  |  |  |

# **Document Status Sheet**

#### Table 2 Document Status Sheet

| Title:                               | The Record | The Reconfigurable Cluster Element Cluster Element (CE) User Guide |                                                          |  |  |  |  |  |  |  |

|--------------------------------------|------------|--------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|--|--|

| ID:                                  | XXX-TD->   | XXX-TD-xxxxx                                                       |                                                          |  |  |  |  |  |  |  |

| Version Issue Date Reason for change |            |                                                                    |                                                          |  |  |  |  |  |  |  |

| 0.1                                  | 0          | 4/16/2009                                                          | Initial draft                                            |  |  |  |  |  |  |  |

| 0.9                                  | 3          | 5/28/2014                                                          | Corrected typos and figures 5 and 35. Corrected Table 9. |  |  |  |  |  |  |  |

# **Table of Contents**

| Abstract                          | • | • | 3    |

|-----------------------------------|---|---|------|

| Hardware compatibility            | • | • | 3    |

| Intended audience                 |   | • | 3    |

| Conventions used in this document |   | • | 3    |

| References                        | • | • | 4    |

| Document Control Sheet.           |   | • | 5    |

| Document Status Sheet             |   |   |      |

|                                   | • | • | . 11 |

| List of Tables                    | • | • | . 13 |

| Chapter 1<br>Overview             |   |   | 15   |

| 1.1 Introduction                  |   |   |      |

| 1.2 The CE (Cluster Element)      |   |   |      |

| 1.3 Frames                        |   |   |      |

| 1.3.1 Frame size                  |   |   | . 17 |

| 1.3.2 Frame header and payload    |   | • | . 18 |

| 1.3.3 Frame type                  |   | • | . 18 |

| 1.4 Register Conventions          | • | • | . 18 |

| 1.4.1 FIFO access                 | • | • | . 19 |

| 1.4.2 Fields                      |   |   |      |

| 1.5 Plugs and Sockets             | • | • | . 20 |

| The Plug/Socket Interface                | • |   | • |   | • | • | • | • | • | • | • | • | • | 23 |

|------------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| 2.1 Overview                             |   |   |   |   |   |   |   |   |   |   |   |   |   | 23 |

| 2.1.1 Outbound Header Transfer Engine .  |   |   |   |   |   |   |   |   |   |   |   |   |   | 24 |

| 2.1.2 Outbound Payload Transfer Engine . |   |   | • |   |   |   |   |   |   |   |   |   |   | 25 |

| 2.1.3 Outbound Frame Descriptors         |   |   |   |   |   |   |   |   |   |   |   |   |   | 26 |

| 2.1.4 Inbound Header Transfer Engine     |   |   |   |   |   |   |   |   |   |   |   |   |   | 28 |

| 2.1.5 Inbound Payload Transfer Engine .  |   |   |   |   |   |   |   |   |   |   |   |   |   | 28 |

| 2.1.6 Inbound Frame Descriptors          |   |   |   |   |   |   |   |   |   |   |   |   |   | 30 |

| 2.2 Outbound Interface                   |   |   |   |   |   |   |   |   | • |   | • | • |   | 31 |

| 2.2.1 Transactions                       | • |   |   |   |   |   |   |   |   |   |   | • |   | 34 |

| 2.2.1.1 Free descriptor                  |   |   |   | • |   |   |   |   | • |   | • | • |   | 34 |

| 2.2.1.2 Transmit frame with only header  |   |   |   |   |   |   |   |   |   |   |   |   |   | 34 |

| 2.2.1.3 Transmit frame                   |   |   |   |   |   |   |   |   |   |   |   |   |   | 35 |

| 2.2.1.4 Transmit and rendezvous frame    |   |   |   |   |   |   |   |   |   |   |   |   |   | 37 |

| 2.3 Inbound interface                    |   |   |   |   |   |   |   |   |   |   |   |   |   | 38 |

| 2.3.1 Transactions                       |   |   |   |   |   |   |   |   |   |   |   |   |   | 41 |

| 2.3.1.1 Free descriptor                  |   |   |   |   |   |   |   |   |   |   |   |   |   | 41 |

| 2.3.1.2 Flush frame payload              |   |   |   |   |   |   |   |   |   |   |   |   |   | 41 |

| 2.3.1.3 Receive frame payload            |   |   |   |   |   |   |   |   |   |   |   |   |   | 42 |

| 2.3.1.4 Receive payload and rendezvous   |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| 2.3.1.5 Rendezvous frame                 |   |   |   |   |   |   |   |   |   |   |   |   |   | 44 |

| 2.4 Management                           |   |   |   |   |   |   |   |   |   |   |   |   |   | 45 |

| 2.4.1 Transitions                        |   |   |   |   |   |   |   |   |   |   |   |   |   | 46 |

| 2.4.1.1 Online to offline                |   |   |   |   |   |   |   |   |   |   |   |   |   | 46 |

| 2.4.1.2 Offline to online                |   |   |   |   |   |   |   |   |   |   |   |   |   | 46 |

| 2.4.1.3 Offline to disabled              |   |   |   |   |   |   |   |   |   |   |   |   |   | 46 |

| 2.4.1.4 Disabled to offline              |   |   |   |   |   |   |   |   |   |   |   |   |   | 46 |

| 2.4.2 Operations                         |   |   |   |   |   |   |   |   |   |   |   |   |   | 47 |

| 2.4.2.1 Plug-in reset                    |   |   |   |   |   |   |   |   |   |   |   |   |   | 47 |

| 2.4.2.2 Bringing a plug-in online        |   |   |   |   |   |   |   |   |   |   |   |   |   | 47 |

| 2.4.2.3 Reset a plug-in while online .   |   |   |   |   |   |   |   |   |   |   |   |   |   | 47 |

| 2.5 Registers                            |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| 2.5.1 Outbound Free-List                 |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| 2.5.2 Outbound Work-List                 |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| 2.5.3 Inbound Pending-List               |   |   |   |   |   |   |   |   |   |   |   |   |   | 50 |

| 2.5.4 Inbound Work-List                  |   |   |   |   |   |   |   |   |   |   |   |   |   | 52 |

| 2.5.5 Plug-in Management                 |   |   |   |   |   |   |   |   |   |   |   |   |   | 53 |

| 2.6 Interrupt Sources                    |   |   |   |   |   |   |   |   |   |   |   |   |   | 53 |

| -                                        |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| Chapter 3                                |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| The Rendezvous Interface                 |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

| 3.1 Overview                             | • | • | • | • | · | • | • | • | • | • | • | • | • | 55 |

| 3.1.1 Rendezvous and extended context    |    |   |       |   |   |   |   |   |   |   |   |   |   | 57 |

|------------------------------------------|----|---|-------|---|---|---|---|---|---|---|---|---|---|----|

| 3.1.2 Rendezvous and frame transfer-faul | lt | • |       |   |   |   |   |   |   |   |   |   |   | 58 |

| 3.2 Channel Interface                    |    | • |       |   |   |   |   |   |   |   |   |   |   | 59 |

| 3.3 Registers                            |    | • |       |   |   |   |   |   |   |   | • |   |   | 60 |

| 3.3.1 Rendezvous Pending-List            |    | • |       |   |   |   |   |   |   |   | • | • |   | 60 |

| 3.3.2 Transfer-fault Pending-List        |    | • |       |   |   |   |   |   |   |   |   |   |   | 61 |

| 3.4 Interrupt Sources                    | •  | • | <br>• | • | • | • | • | • | • | • | • | • | • | 62 |

| Chapter 4                                |    |   |       |   |   |   |   |   |   |   |   |   |   |    |

| The Interrupt Interface                  | •  | • |       |   | • |   |   |   | • |   | • | • |   | 65 |

| 4.1 Interrupt Sources                    |    | • |       |   |   |   |   |   |   |   | • |   |   | 65 |

| 4.1.1 Interrupt Groups                   |    | • |       |   |   |   |   |   |   |   | • |   |   | 66 |

| 4.1.2 Interrupt Remapping                |    | • |       |   |   |   |   |   |   |   | • | • |   | 66 |

| 4.2 Registers                            |    | • |       |   | • |   |   |   |   |   | • |   |   | 68 |

| 4.2.1 Source remap                       |    | • |       |   | • |   |   |   |   |   | • |   |   | 68 |

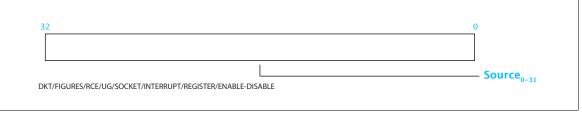

| 4.2.2 Source Group Enables               |    |   |       |   |   |   |   |   |   |   |   |   |   | 68 |

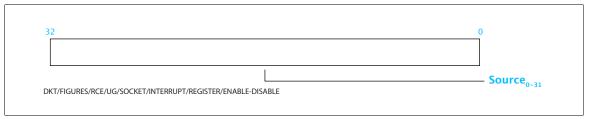

| 4.2.3 Source group disables              | •  |   |       | • | • | • |   |   |   |   | • | • |   | 69 |

| Chapter 5                                |    |   |       |   |   |   |   |   |   |   |   |   |   |    |

| The Bootstrap Support Interface          |    | • |       |   |   |   |   |   |   |   | • |   |   | 71 |

| 5.1 Overview                             |    |   |       |   |   |   |   |   |   |   |   |   |   | 71 |

| 5.2 Registers                            |    |   |       |   |   |   |   |   |   |   |   |   |   | 72 |

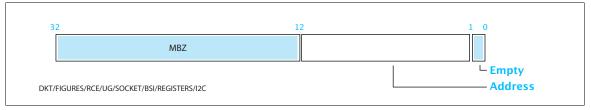

| 5.2.1 I2C Signal                         |    |   |       |   |   |   |   |   |   |   |   |   |   | 72 |

| 5.2.2 Configuration                      |    |   |       |   |   |   |   |   |   |   |   |   |   | 72 |

| 5.3 Interrupt Sources                    | •  |   | <br>• |   | • | • |   |   |   |   | • | • | • | 73 |

| Appendix A                               |    |   |       |   |   |   |   |   |   |   |   |   |   |    |

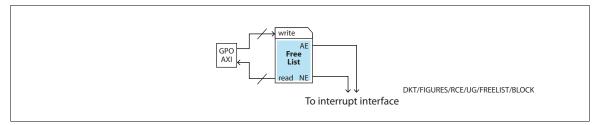

| Utility Free-list Interface              | •  | • | <br>• | • | • | • | • | • | • | • | • | • | • | 75 |

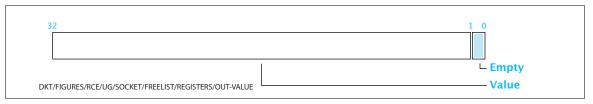

| A.1 Registers                            | •  | • |       | • | • | • | • |   |   | • | • | • | • | 75 |

| A.1.1 Allocate from Utility Free-List    |    | • |       |   | • |   |   |   |   |   | • |   |   | 76 |

| A.1.2 Return to Utility Free-List        |    | • |       |   | • | • |   |   |   |   | • | • |   | 77 |

| A.2 Interrupt Sources                    | •  | • |       | • | • | • | • | • |   | • | • | · | • | 77 |

| Appendix B                               |    |   |       |   |   |   |   |   |   |   |   |   |   |    |

| Register Map                             |    | • |       |   |   |   |   |   |   |   | • |   |   | 79 |

### List of Figures

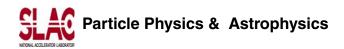

| Figure 1  | p. 16 | RCE block diagram                                         |

|-----------|-------|-----------------------------------------------------------|

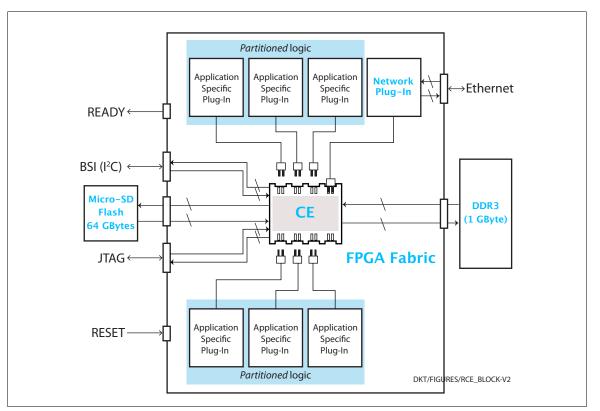

| Figure 2  | p. 17 | CE block diagram                                          |

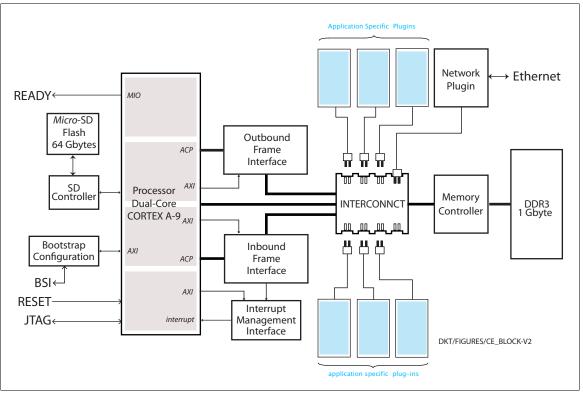

| Figure 3  | p. 21 | Block diagram of the Plug wrapper                         |

| Figure 4  | p. 24 | Block diagram of the Socket and its interfaces            |

| Figure 5  | p. 27 | Outbound frame descriptors.                               |

| Figure 6  | p. 31 | Inbound frame descriptors.                                |

| Figure 7  | p. 33 | Outbound descriptors and instructions.                    |

| Figure 8  | p. 34 | Free outbound descriptor (opcode = 0)                     |

| Figure 9  | p. 35 | Transmit outbound frame with only header (opcode = 1)     |

| Figure 10 | p. 36 | Transmit outbound frame (opcode = 2)                      |

| Figure 11 | p. 37 | Transmit and rendezvous outbound frame (opcode = 3)       |

| Figure 12 | p. 40 | Inbound descriptors and instructions.                     |

| Figure 13 | p. 41 | Free inbound descriptor (opcode = 0)                      |

| Figure 14 | p. 42 | Flush inbound frame payload (opcode = 1)                  |

| Figure 15 | p. 42 | Receive inbound frame payload (opcode = 2)                |

| Figure 16 | p. 43 | Receive inbound payload and rendezvous frame (opcode = 6) |

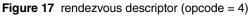

| Figure 17 | p. 44 | rendezvous descriptor (opcode = 4)                        |

| Figure 18 | p. 49 | Returned value from outbound free-list.                   |

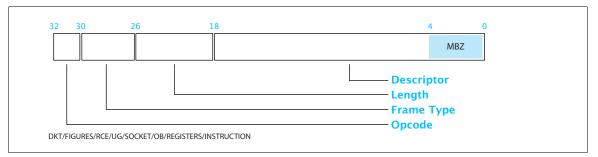

| Figure 19 | p. 49 | Outbound instruction.                                     |

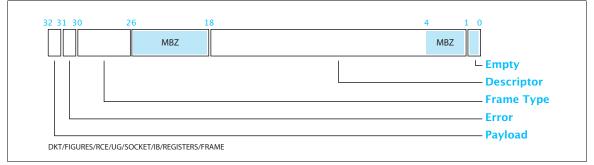

| Figure 20 | p. 51 | Returned value from inbound pending-list.                 |

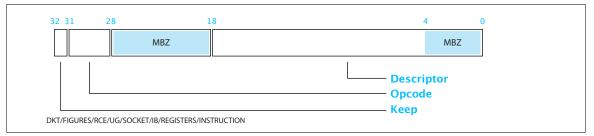

| Figure 21 | p. 52 | Inbound instruction.                                      |

| Figure 22  | p. 53 | Plug-in Management Register                       |

|------------|-------|---------------------------------------------------|

| Figure 23  | p. 56 | Block diagram of the Rendezvous Interface         |

| Figure 24  | p. 58 | Socket descriptor, rendezvous channel and context |

| Figure 25  | p. 59 | Rendezvous with transfer fault                    |

| Figure 26  | p. 60 | Block diagram of the Rendezvous Channel           |

| Figure 27  | p. 61 | Rendezvous extended context register              |

| Figure 28  | p. 61 | Transfer fault register                           |

| Figure 29  | p. 66 | Block diagram of an Interrupt Group               |

| Figure 30  | p. 67 | Block diagram of the Interrupt interface.         |

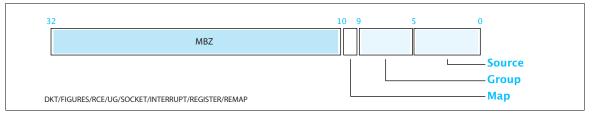

| Figure 31  | p. 68 | Source Interrupt remap register                   |

| Figure 32  | p. 69 | Interrupt group enables                           |

| Figure 33  | p. 70 | Interrupt group disables                          |

| Figure 34  | p. 71 | Block diagram of the Boot Support Interface       |

| Figure 35  | p. 72 | I2C Signal                                        |

| Figure 36  | p. 72 | BSI Configuration                                 |

| Figure A.1 | p. 75 | The utility Free-list                             |

| Figure A.2 | p. 76 | Value removed from utility free-list.             |

| Figure A.3 | p. 77 | Value inserted to utility free-list.              |

# **List of Tables**

| Table 1   | p. 5  | Document Control Sheet                      |

|-----------|-------|---------------------------------------------|

| Table 2   | p. 6  | Document Status Sheet                       |

| Table 3   | p. 32 | Outbound opcodes                            |

| Table 4   | p. 39 | Inbound Opcodes                             |

| Table 5   | p. 45 | Plug-in state                               |

| Table 6   | p. 48 | Socket Register Map                         |

| Table 7   | p. 54 | Socket Interrupt Source Map                 |

| Table 8   | p. 62 | Rendezvous Interrupt Source Map             |

| Table 9   | p. 65 | Interrupt sources                           |

| Table 10  | p. 67 | Interrupt group address and interrupt lines |

| Table A.1 | p. 76 | Utility Free-list Register Map              |

| Table A.2 | p. 78 | Free-list Interrupt Source Map              |

| Table B.1 | p. 79 | Register Map                                |

# Chapter 1 Overview

## 1.1 Introduction

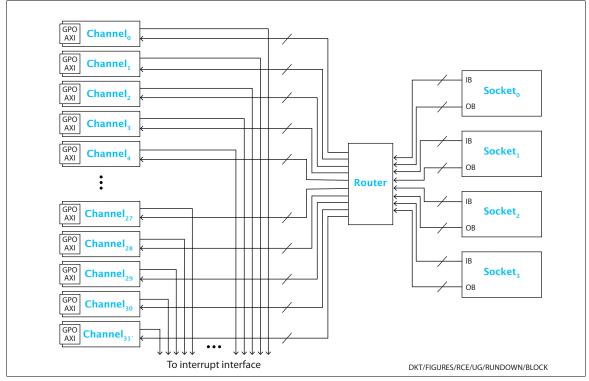

For the purposes of this document a *Protocol-Plug-In* is defined as simply an arbitrary set of application specific logic, coresident with an RCE's FPGA fabric, but which, requires the exchange of information between it and its corresponding RCE. In turn, that requirement implies the necessity for a common, abstract communication mechanism between plug-in and RCE. That abstract model is the *Plug* and *Socket*. The *Plug* is a set of *Core* IP, provided by the system to the user which wraps a common communication interface around their specific plug-in. Once wrapped, that plug-in can subsequently, independent of implementation or specific function, be "plugged into" one of the *four* (4) predefined *Sockets* contained on an RCE, thus enabling communication between it and its RCE. The relationship between the RCE, its sockets and plug-ins and their corresponding plugs is illustrated in Figure 1:

Figure 1 RCE block diagram

TBD

## 1.2 The CE (Cluster Element)

TBD. The relationship between the CE, its sockets and its plug-ins is illustrated in Figure 2:

Figure 2 CE block diagram

TBD

## 1.3 Frames

Data are exchanged between CE and plug-in as indivisible units of *Frames*. A frame is simply a set of arbitrary data characterized by content, size and type. Frames sent by the CE to a plug-in for *transmission* are *outbound* frames. Frames *received* by a plug-in and sent to the CE are *inbound* frames. Outbound frames are described in Section 2.2 and inbound frames in Section 2.3.

#### 1.3.1 Frame size

A frame's size is always specified in units of *bytes* (8-bits). Frames are allowed to vary in size from transfer to transfer and/or by specific plug-in. The minimum sized frame, whether inbound or outbound, is *one* (1) *byte* while the maximum sized frame is determined by the specific plug-in.

#### **1.3.2 Frame header and payload**

TBD

#### 1.3.3 Frame type

A frame's *Type* is a *small*<sup>1</sup> enumeration assigned to a frame. The enumeration for an *outbound* frame would be assigned (typically) by plug-in specific software in the CE, while for an *inbound* frame that assignment is the responsibility of the plug-in. Enumerations classify a frame's contents and in turn that classification may be used to vector a frame to its appropriate content specific processing. For an inbound frame that processor is within the plug-in, while for an outbound frame that processor is (typically) plug-in specific software in the CE.

For example, assume a plug-in that requires configuration information from the CE before it may transfer frames. To satisfy that requirement the appropriate configuration information could be built and sent to the plug-in packaged as an outbound frame. The plug-in would differentiate configuration frames from transmission frames by assigning a different enumeration to each type. Or, as a further example, assume the same plug-in accumulates state information as it transfers frames, for example, the number of frames it has transmitted or received. The CE wishes to sample those counters. In such a case the CE builds and sends to the plug-in an outbound frame requesting the current value of that counter. The plug-in responds by sampling that counter, saving that sample within an inbound frame and sending that frame back to the CE. Plug-in specific software on the CE would differentiate that frame from frames received by the plug-in through different enumeration values.

## **1.4 Register Conventions**

The firmware interface to the CE consists of *registers* mapped to the processor's GPO AXI bus (see Appendix B, "Register Map"). Registers on this bus are all *thirty-two* (32) bits wide. Registers are accessed through either load or store instructions whose target is the address of the specified register. Load instructions are used to *read* a register and Store instructions are used to *write* a register. Although all of I/O space is nominally marked read/writable, side effects may occur to a accessed register which is naturally read or write *only*. Specifically for write-only registers load instructions will return an indeterminate value and for read-only registers store instructions will fail and the value to be written is silently discarded.

<sup>1.</sup> Contained in a 4-bit field.

#### 1.4.1 FIFO access

Many registers are in fact mapped to FIFOS. Side effects to these types of registers may occur depending on access type and whether the FIFO's *read* or *write* port is mapped to the bus. Specifically, for a register mapped to a FIFO's *write* port:

- The FIFO is treated as a *Write-Only* register.

- Store instructions to a *non-empty* FIFO insert one, 32-bit entry onto the FIFO.

- Store instructions to a *full* FIFO fail. The state of the FIFO is unchanged and the value to be written is silently discarded.

- Load instructions return an indeterminate value. The state of the FIFO is unchanged.

And for a register mapped to a FIFO's *read* port:

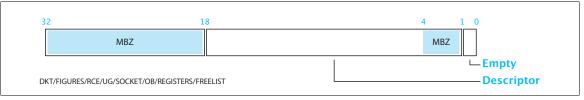

- The FIFO is treated as a *Read-Only* register.

- Load instructions to a *non-empty* FIFO remove one entry from the FIFO and return that entry as a single, 32-bit value. The *low-order* bit of the returned value is always *zero* (0).

- Load instructions to a *empty* FIFO return a single, 32-bit value. The *low-order* bit of the returned value is always *one* (1). The remaining high-order 31 bits are unspecified, but should be *zero* (0). The state of the FIFO is unchanged.

- Store instructions fail. The state of the FIFO is unchanged and the value written is silently discarded.

#### 1.4.2 Fields

Many, if not most of the registers described in this document are further broken down into *fields*, where a field is specified as a bit offset and length (in number of bits). Any field used as a boolean has a width of one (1) bit. A value of *one* (1) is used to indicate its *set* or *true* sense and a value of *zero* (0) to indicate its *clear* or *false* sense. Field numbering (bit offsets) for registers are such that *zero* (0) corresponds to a register's *Least-Significant-Bit* (LSB) and thirty-one (31) corresponds to a register's *Most-Significant-Bit* (MSB). Bit offsets are always specified in decimal, unless otherwise noted. There are four types of generic fields:

**Not defined:** Undefined fields are identified as *Must Be Zero* (MBZ) and are illustrated *blued out*. MBZ fields will:

- read back as zero

- ignore writes

- reset to zero

**Read/Write:** Read/Write fields will, on *Reset*, be set to *zero*.

**Selective Set and Clear (SSC):** SSC fields are used where it is necessary to change one or more fields of a register and leave the remaining fields unchanged<sup>1</sup>. These fields will always have a complementing **Enable** field. This field will have the same width as its corresponding SSC field. The **Enable** field for any arbitrary SSC field is computed by shifting the field's offset *left* by 16 bits (decimal). An **Enable** field is illustrated *lightly* blued-out. It satisfies the following conventions:

- may only be *set*, clearing the field is ignored

- reads back as zero

- SSC fields will:

- ignore writes, *unless* their corresponding field enables are also asserted

- reset to zero, unless otherwise documented

- **Read-Only:** Read-only fields are illustrated *lightly* blued-out with their value. *Read-Only* fields will:

- ignore writes

- reset to *zero*, unless otherwise documented

### 1.5 Plugs and Sockets

The RCE specifies a common framework for the exchange of information between application specific logic and the CE. That framework is based on a *Plug* and *Socket* model. In that model the *Plug* is a set of common *Core* IP provided by the framework which an application uses to *wrap* their specific logic. Any logic so wrapped is called *Plug-Specific-Logic* (PSL) while the combination of plug wrapper and PSL is called a *Plug-in*.

In turn, the CE contains a set of predefined Sockets. A socket has two functions, it:

- Provides a site to connect a plug-in to the CE

- Defines an I/O model for software resident on the CE's processor to send and receive arbitrary data from a connected plug-in.

Once wrapped, all PSLs, independent of their logic, appear and function the same to the CE. That is, they all share a common interface which allows their logic to "plug in" to any one of the CE's four available *sockets*. Once plugged in, that logic is able to transparently exchange information between it and the CE.

The relationship between the CE with its sockets and the plug-in with its plug and application specific logic is illustrated in Figure 3:

<sup>1.</sup> Sometimes referred to as *indivisible* read/modify/write.

Figure 3 Block diagram of the Plug wrapper

TBD

# Chapter 2 The Plug/Socket Interface

## 2.1 Overview

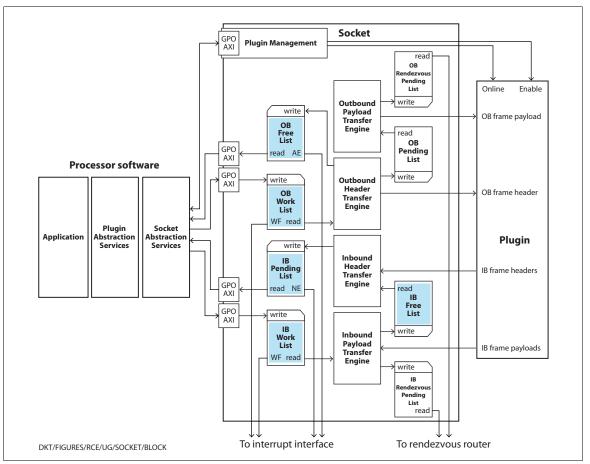

The socket is the *firmware* interface responsible for mediating frame transfer between processor software and plug-in. Figure 4 below is a block diagram illustrating the relationship between processor code, socket and plug-in:

Figure 4 Block diagram of the Socket and its interfaces

Inside the socket are four *engines*, two to manage outbound frame transfers and two to manage inbound transfers. Each engine operates completely independently, allowing for concurrent inbound and outbound transfers. Each of the four engines is briefly summarized below.

### 2.1.1 Outbound Header Transfer Engine

In conjunction with the outbound payload transfer engine described in Section 2.1.2 below, the outbound *header* transfer engine moves outbound frames from processor to plug-in for transmission. Its principal responsibility is to transfer a frame *header* from descriptor to plug-in.

Both outbound header transfer engine and outbound payload transfer engine coordinate their operation though their socket's *outbound pending-list*. The pending-list is a *512* entry FIFO with its *write* port connected to this engine and its *read* port connected to the payload engine. Entries in this list correspond to the contents of an outbound descriptor's *header* (see Section 2.1.3).

A transfer is initiated by scheduling an *outbound instruction* to the engine. An instruction contains both *opcode* and *operand*. The instruction's opcode determines the specific operation required of the engine. The set of operations the engine supports is enumerated within Table 3 on page 32.

The operand describes the frame to transmit. That description is contained in a small, fixed size buffer called an *outbound frame descriptor* and is described in Section 2.1.3. Descriptors are allocated from the socket's *free-list*. The free-list is a *512* entry FIFO with its *write* port connected to the engine and its *read* port mapped to a GPO AXI register. Reading from this register allocates a descriptor.

Once allocated and initialized outbound instructions are queued to the engine's *work-list* for execution. The work-list is also a *512* entry FIFO. However, unlike the socket's free-list its *write* port is mapped to a GPO AXI register and its *read* port is connected to the engine. Writing this register *inserts* an entry on the FIFO and consequently queues an instruction. Note that as the work-list *is* a FIFO, instructions are always executed in the order they were queued.

The engine executes one instruction at a time. Execution is initiated when three conditions are met:

- The engine is idle.

- The socket's outbound pending-list is not *full*.

- The socket's outbound work-list is not *empty*.

When those conditions are met, the engine removes from its work-list an entry containing the instruction to execute. The instruction is both decoded and executed. Execution involves inserting the *header* of the instruction's descriptor onto the socket's pending-list and copying its *body* to the socket's plug-in. After execution the engine deallocates the descriptor by inserting it onto the socket's free-list and returns to idle.

Note, the free and work lists allow processor software to issue transfer requests concurrently with respect to their processing. The segregation of header and payload provides separation of protocol processing from its content without the need to partition these functions into either separate tasks or processes.

The outbound interface is described in further detail in Section 2.2.

### 2.1.2 Outbound Payload Transfer Engine

In conjunction with the outbound header engine described in Section 2.1.1 above, the outbound *payload* transfer engine moves outbound frames from processor to plug-in for transmission. Its principal responsibility is to transfer a frame's *payload* from processor memory to plug-in.

Both outbound payload transfer engine and outbound header transfer engine coordinate their operation though their socket's *outbound pending-list*. The pending-list is a 512 entry FIFO with

its *read* port connected to this engine and its *write* port connected to the header engine. Entries in this list correspond to the *contents* of an outbound descriptor's header (see Section 2.1.3).

The engine processes one header at a time. Processing is initiated when four conditions are met:

- The engine is idle.

- The socket's outbound pending-list is not *empty*.

- The socket's plug-in is not *full*.

- The socket's outbound rendezvous-pending-list is not *full*.

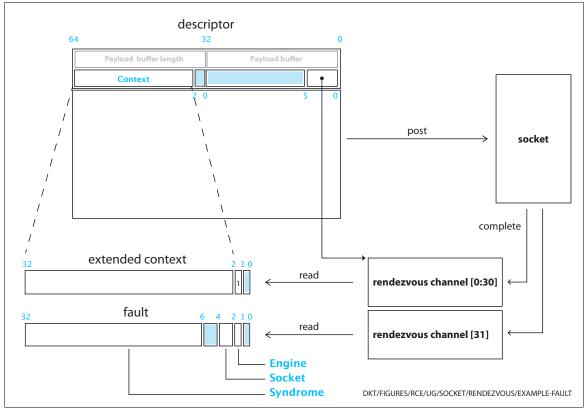

When those conditions are met, the engine removes an entry from the socket's pending-list. That entry contains the header contents to process. It specifies at a minimum, a reference to a buffer containing a payload to be moved to the plug-in for transmission. First the payload is processed. After payload processing completes, the engine will:

- Based on header, conditionally inserts a rendezvous message on the socket's outbound rendezvous-pending-list. This signals a rendezvous (see Section 3.1.1).

- Based on payload processing status, conditionally inserts a frame transfer-fault message on the socket's outbound rendezvous-pending-list. This signals a frame transfer-fault (see Section 3.1.2).

- Returns to idle.

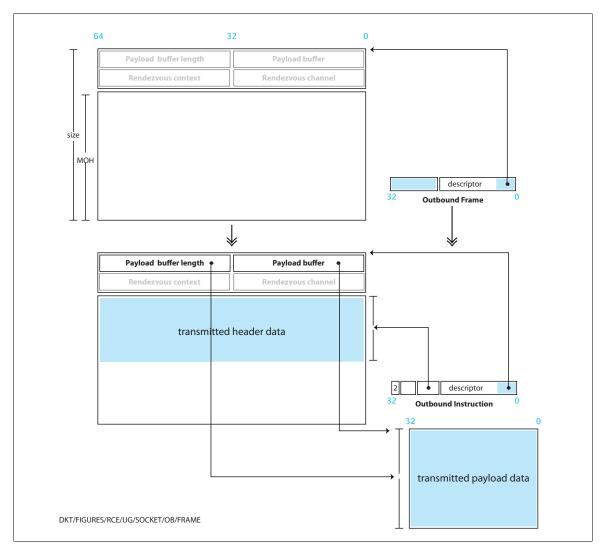

#### 2.1.3 Outbound Frame Descriptors

A frame's transmission state is maintained by the *outbound frame descriptor*. Its principal function is to specify an outbound frame's header and payload<sup>1</sup>. Descriptors are fixed size buffers containing an integral number of *quadwords*<sup>2</sup>. They must also be quadword aligned and located within the processor's 256 KBytes of *On-Chip-Memory* (OCM). The socket interface communicates descriptors through its interface by *reference*. A reference is expressed as a *byte* offset from the starting location of the OCM. Note that location and quadword alignment dictate that a reference is an *18-bit* quantity whose low-order *four* (4) bits are always *zero* (0).

Each socket manages an ensemble of descriptors whose members are all the same size. However for that ensemble, while their size is fixed, their number varies as a function of socket as determined by software at processor boot time. Descriptor management is orchestrated through a *free-list* held by the socket. Software *allocates* from this free-list and the socket's transfer engine *returns* descriptors to this free-list. See Section 2.5.1 for a discussion of that free-list.

Descriptors contain a quadword *header* followed by a fixed size *body*. Body size is equal to the MOH (*Maximum-Outbound-Header*) of a socket's plug-in (see Section 1.3.2). A frame's header is always contained by *value* in a descriptor's body and its payload, if present by *reference* in its

<sup>1.</sup> When present.

<sup>2.</sup> Sixteen (16) *bytes* or 128 *bits*

header. Figure 5 on page 27 illustrates a hypothetical descriptor as first allocated and then subsequently initialized and deallocated:

Figure 5 Outbound frame descriptors.

The figure shows that descriptor size is the sum of header and body and its body size is equal to a plug-in's MOH. Each allocated descriptor corresponds to a frame to be transmitted. After allocation the descriptor is initialized. The header data for a frame is copied to the descriptor's body and its header contains the reference to its payload. Once initialized, the descriptor is used to build and queue an instruction to the transfer engine for execution.

### 2.1.4 Inbound Header Transfer Engine

In conjunction with the inbound payload engine described in Section 2.1.5 below, the inbound *header* transfer engine transfers received inbound frames from plug-in to processor. Its principal responsibility is to transfer a frame's *header* from plug-in to descriptor.

Both inbound header transfer engine and inbound payload transfer engine coordinate their operation though their socket's *inbound pending-list*. The free-list is a 512 entry FIFO with its *read* port connected to this engine and its *write* port connected to the payload engine. Entries in this list are a *reference* to an inbound frame descriptor. The descriptor is a small, fixed size buffer described in Section 2.1.6. Removing from this list *allocates* a descriptor and inserting onto this list *frees* a descriptor.

The engine processes frames *one* at a time. Processing is initiated when four conditions are met:

- The engine is idle.

- The socket's free-list is not *empty*.

- The engine's pending-list is not *full* (see below).

- The socket's plug-in has at least one frame to transfer.

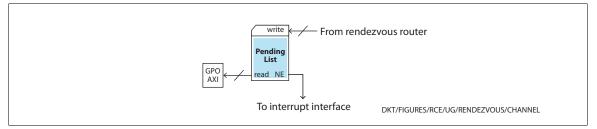

When those conditions are met the engine allocates a descriptor from the socket's free-list. Once allocated, the engine moves the frame's header from plug-in to the descriptor's body. and concludes by inserting a reference to the descriptor on the socket's *pending-list*. The pending-list is also a *512* entry FIFO however, its *write* port is connected to the engine and its *read* port is mapped to a GPO AXI register. Note that as the pending-list *is* a FIFO, descriptors are always received in the order they arrive at the plug-in.

To initiate processing of an inbound frame processor software reads the socket's pending-list register. Reading this register removes a descriptor reference from the socket's pending-list. Note that the pending-list FIFO has its *Not-Empty* flag connected to a processor interrupt.

The inbound interface is described in further detail in Section 2.3.

#### 2.1.5 Inbound Payload Transfer Engine

In conjunction with the inbound header engine described in Section 2.1.4 above, the inbound *payload* transfer engine transfers received inbound frames from plug-in to processor. Its principal responsibility is to move a frame's *payload*.

Both inbound payload transfer engine and inbound header transfer engine coordinate their operation though their socket's *inbound free-list*. The free-list is a *512* entry FIFO with its *write* port connected to this engine and its *read* port connected to the header engine. Entries in this list are a *reference* to an inbound frame descriptor. The descriptor is a small, fixed size buffer described in Section 2.1.6. Removing from this list *allocates* a descriptor and inserting onto this list *frees* a descriptor.

A transfer is initiated by processor software by scheduling an *inbound instruction* to the engine. An instruction contains both *opcode* and *operand*. Its opcode specifies the operation required of the engine. The set of operations supported by an inbound engine is enumerated in Table 4 on page 39.

The operand describes where to place in memory a received payload. That description is contained in a small, fixed size structure called an *inbound frame descriptor* that is described in Section 2.1.6. Descriptors were returned by reading from the inbound pending-list (see Section 2.1.4).

Once allocated and initialized work instructions are queued to the engine's *work-list* for execution. The work-list is also a *512* entry FIFO. However, unlike the socket's free-list its *write* port is mapped to a GPO AXI register and its *read* port is connected to the engine. Writing this register *inserts* an entry on the FIFO and consequently schedules an instruction. Note that as the work-list *is* a FIFO, instructions are always executed in the order they were queued.

The engine executes one instructions at a time. Execution is initiated when four conditions are met:

- The engine is idle.

- The socket's inbound free-list is not *full*.

- The socket's inbound rendezvous-pending-list is not full.

- The socket's inbound work-list is not *empty*.

When those conditions are met, the engine removes from its work-list an entry containing the instruction to execute. The instruction is decoded and executed. Execution first involves, conditionally processing the plug-in's payload by either transfer to memory or discard. After payload processing the engine:

- Based on instruction, conditionally inserts a rendezvous message on the socket's inbound rendezvous-pending-list. This signals a rendezvous (see Section 3.1.1).

- Based on payload processing status, conditionally inserts a frame transfer-fault message on the socket's inbound rendezvous-pending-list. This signals a frame transfer-fault (see Section 3.1.2).

- Based on instruction, inserts the descriptor it on the socket's inbound free-list. This

deallocates the descriptor.

- Returns to idle.

Note, the pending and work lists allow processor software to build transfer requests concurrently with respect to their processing. The segregation of header and payload provides separation of protocol processing from its content without the need to partition these functions into either separate tasks or processes.

The inbound interface is described in further detail in Section 2.3.

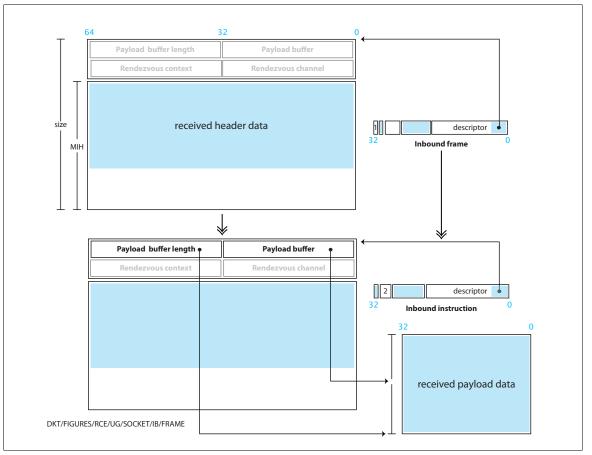

#### 2.1.6 Inbound Frame Descriptors

A frame's reception state is maintained by the *inbound frame descriptor*. Its principal function is to specify an inbound frame's header and payload<sup>1</sup>. Descriptors are fixed size buffers containing an integral number of *quadwords*<sup>2</sup>. They must also be quadword aligned and located within the processor's 256 KBytes of *On-Chip-Memory* (OCM). The socket interface communicates descriptors through its interface by *reference*. A reference is expressed as a *byte* offset from the starting location of the OCM. Note that location and quadword alignment dictate that a reference is an *18-bit* quantity whose low-order *four* (4) bits are always *zero* (0).

Each socket manages an ensemble of descriptors whose members are all the same size. However for that ensemble, while their size is fixed, their number varies as a function of socket and is determined by software at processor boot time. Descriptor management is orchestrated through a *free-list* held by the socket. Software *allocates* from this free-list and the socket's transfer engine *returns* descriptors to this free-list. See Section 2.5.1 for a discussion of that free-list.

Descriptors contain a quadword *header* followed by a fixed size *body*. Body size is equal to the MIH (*Maximum-Inbound-Header*) of a socket's plug-in (see Section 1.3.2). A frame's header is always contained by *value* in a descriptor's body and its payload, if present by *reference* in its header. Figure 6 on page 31 illustrates a hypothetical descriptor as retrieved from the socket's pending-list and then subsequently initialized and deallocated:

<sup>1.</sup> When present.

<sup>2.</sup> Sixteen (16) *bytes* or 128 *bits*

Figure 6 Inbound frame descriptors.

The figure shows that descriptor size is the sum of its header and body and its body size is equal to a plug-in's MIH. Each descriptor returned from the pending-list corresponds to one received inbound frame and its header is contained in the descriptor's body.

In this example the received frame contains a payload. After reception the header is decoded to resolve the placement of the frame's payload and once resolved a reference to the receive buffer is copied to the descriptor's header. The initialized descriptor is used to build the instruction to queue to the transfer engine for execution.

## 2.2 Outbound Interface

As described in Section 2.1.1 a socket's outbound interface employs its outbound *work* and *free* list FIFOs. Consequently, its corresponding processor interface consists simply of two GPO AXI registers (see Appendix B, "Register Map"). The *read* port of the *free-list* FIFO is mapped to a *read-only* register while the *write* port of the *work-list* FIFO is mapped to a *write-only* register.

Therefore, for each socket the interface provides processor software with two operations: *Removal* from its free-list and *insertion* onto its work-list. Section 1.4.1 describes the access policy for FIFOs mapped to registers.

An entry inserted on a socket's work-list is an *outbound instruction*. An instruction serves two purposes: First, it specifies a potential transmit function. That function is encoded as an *opcode* and *operand*. The opcode specifies the type of transfer required of the engine and the operand is a reference to an *outbound descriptor* (see Section 2.1.3) containing the frame to transfer. Second, the instruction directs the engine, once transfer is complete to return its corresponding descriptor back to the transfer engine's free-list. Table 3 on page 32 enumerates the allowed transfer functions along with their associated encoding, while Section 2.5.2 defines the structure of an instruction.

| TABLE 3 | Outbound opcodes |

|---------|------------------|

|         |                  |

| Opcode | Description and transfer engine action                                                                                                                                                                                                                                                                                                                              | See:            |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0      | The instruction's descriptor defines <i>neither</i> a frame nor rendezvous. The entire contents of the instruction's descriptor are ignored and the engine returns the descriptor to its free-list.                                                                                                                                                                 | Section 2.2.1.1 |

| 1      | The instruction's descriptor specifies a frame containing <i>only</i> a header. The engine transfers the frame to its corresponding plug-in for transmission. On completion the engine returns the descriptor to its free-list.                                                                                                                                     | Section 2.2.1.2 |

| 2      | The instruction's descriptor specifies a frame containing <i>both</i> header and payload. The engine gathers the frame and transfers it to its corresponding plug-in for transmission. On completion the engine returns the descriptor to its free-list.                                                                                                            | Section 2.2.1.3 |

| 3      | The instruction's descriptor specifies a frame containing <i>both</i> header and payload as well as rendezvous. The engine gathers the frame and transfers it to its corresponding plug-in for transmission. On completion, it inserts the specified rendezvous context onto the specified rendezvous channel and returns the descriptor to its outbound free-list. | Section 2.2.1.4 |

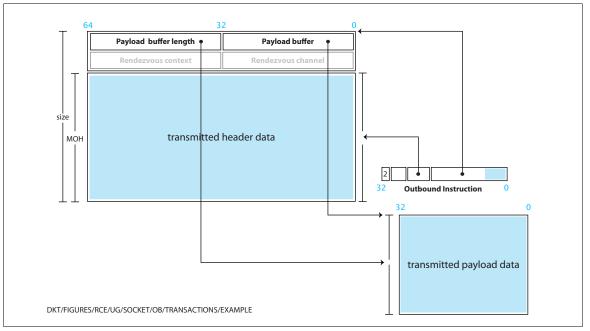

Figure 7 on page 33 expresses the relationship between instruction and descriptor:

Figure 7 Outbound descriptors and instructions.

This example illustrates an instruction to transmit a frame containing *both* header and payload. This corresponds to an opcode *two* (2) instruction with the instructions's descriptor *containing* the frame's header in its body and *pointing* to its payload in its header. Note, for this example, the length of the frame's header is equal to the plug-in's MOH.

A socket's outbound free-list is initially populated by posting opcode *zero* (0) instructions to its *work-list*. Each instruction adds one descriptor to the socket's free-list. Once populated, frame transmission is a straightforward three step process:

- *Allocate* a descriptor by removing from the socket's outbound free-list. The returned value is a reference to a descriptor used to specify the frame transmitted. The structure of a value returned from a free-list is described in Section 2.5.1.

- Convert the descriptor reference to an address. Initialize that descriptor with the frame to be transmitted. Note that a descriptor always contains, if present, the frame's *header* by *value* and if present, its *payload* by *reference*. Section 2.2.1 specifies proper construction of a descriptor's header for each type of instruction.

- Build an outbound instruction using the initialized descriptor. Post the instruction to the transfer engine by inserting it on the engine's outbound work-list (see Section 2.5.2).

Note that although the socket's outbound transfer engine processes only one outbound instruction at a time and always in the order requested this does not imply the processor is necessarily blocked waiting on the transfer engine to complete. Instead, the socket's pending FIFO allows for an asynchronous I/O model in which instructions are *queued* while the engine

is busy processing a transaction. The maximum number of outstanding transactions permitted determined by the initial population of the socket's free-list.

## 2.2.1 Transactions

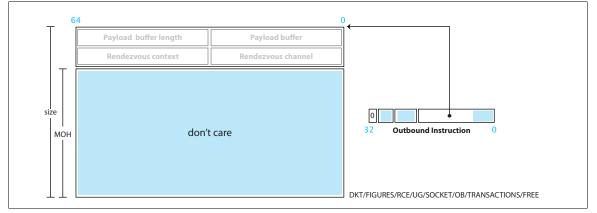

#### 2.2.1.1 Free descriptor

Figure 8 illustrates an instruction which does *not* transmit a frame and *only* frees a previously allocated descriptor buffer. The instruction contains a reference to a valid *outbound* descriptor (see Section 2.1.3) and an opcode (see Table 3 on page 32) with a value of *zero* (o). The descriptor reference was acquired from a socket's free-list as described in Section 2.5.1.

Figure 8 Free outbound descriptor (opcode = 0)

Note that for this type of instruction both **Length** and **Frame Type** fields are ignored by the transfer engine, but should be *zero* (0). Note also that the contents of the descriptor's header and body are ignored by the transfer engine. This instruction serves two purposes:

- To initially populate a socket's outbound free-list after a reset (see Section 2.2).

- To handle an error in descriptor construction which must abort transmission.

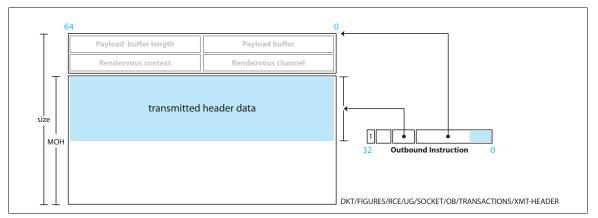

#### 2.2.1.2 Transmit frame with only header

Figure 9 illustrates an instruction which transmits an outbound frame. However that frame is wholly contained in the instruction's descriptor body. The instruction contains a reference to a valid *outbound* descriptor (see Section 2.1.3) and an opcode (see Table 3 on page 32) with a value of *one* (1). The descriptor reference was acquired from a socket's free-list as described in Section 2.5.1.

**Figure 9** Transmit outbound frame with only header (opcode = 1)

For this type of instruction both **Length** and **Frame Type** fields must contain valid values. The **Length** field must:

- be expressed in units of *quadwords*.

- be equal to the size of the transmitted frame's header.

- not be *zero* (0).

- not exceed the plug-in's MOH (see Section 2.2).

If any of these constraints are violated the socket's resulting behaviour is undefined.

The behaviour of a plug-in processing a frame whose type it does not support is unspecified.

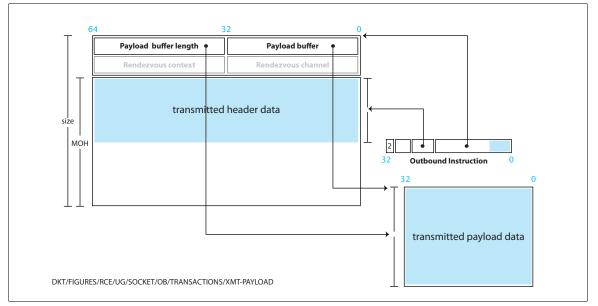

#### 2.2.1.3 Transmit frame

Figure 10 illustrates an instruction which transmits an outbound frame. That frame contains both header and payload. The instruction contains a reference to a valid *outbound* descriptor (see Section 2.1.3) and an opcode (see Table 3 on page 32) with a value of *two* (2). The descriptor reference was acquired from a socket's free-list as described in Section 2.5.1.

Figure 10 Transmit outbound frame (opcode = 2)

For this type of instruction both **Length** and **Frame Type** fields must contain valid values. The **Length** field must:

- be expressed in units of *quadwords*.

- be equal to the size of the transmitted frame's header.

- not exceed the plug-in's MOH (see Section 2.2).

If any of these constraints are violated the socket's resulting behaviour is *undefined*.

The behaviour of a plug-in processing a frame whose type it does not support is *unspecified*.

As is the case for the transmission of any outbound frame, header data is contained within the body of the instruction's descriptor. However, unlike an opcode 1 instruction (see Section 2.2.1.2), *zero* is a valid length. If its **Length** field has a *zero* (0) value the transmitted frame contains *only* payload.

The descriptor's header contains a valid *payload reference*. That reference occupies the header's first quadword and contains two 32-bit (*word*) fields whose interpretation is as follows:

**Payload buffer:** This field contains a *physical* address pointing to a buffer containing the frame's payload. No restrictions are placed on its alignment. The transfer engine assumes the buffer has either previously been flushed or is located in uncached memory. Transfer behaviour is undefined if neither constraint is met. A buffer's *length* is determined by the field below.

**Payload length:** This field contains the length of the payload whose data are pointed to by the field above. Lengths are expressed in units of *bytes* (8-bits) and range from a value of *zero* (0) to the MOF of the plug-in associated with the socket (see Section 1.3.2). A value of zero is allowed, but will *not* incur a transfer. The behaviour of a transfer which exceeds MOF is undefined, as is the behaviour of a transfer exceeding the processor's physical address space.

The contents of the rendezvous reference in the descriptor's header are ignored by the transfer engine and need not be initialized to any known value.

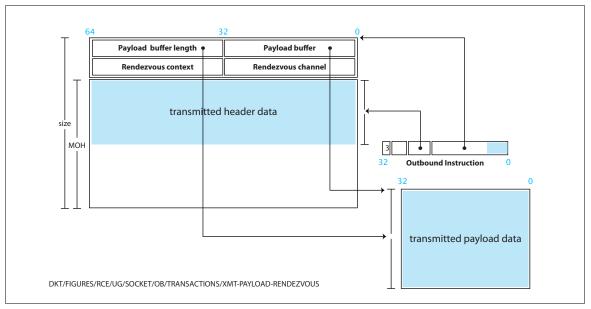

#### 2.2.1.4 Transmit and rendezvous frame

Figure 11 illustrates an instruction which transmits an outbound frame. That frame contains both header and payload. However, once its transfer is complete the transfer engine arranges and starts a rendezvous (see Chapter 3). The instruction contains a reference to a valid *outbound* descriptor (see Section 2.1.3) and an opcode (see Table 3 on page 32) with a value of *three* (3).

Figure 11 Transmit and rendezvous outbound frame (opcode = 3)

For this type of instruction both **Length** and **Frame Type** fields must contain valid values. The **Length** field must:

- be expressed in units of *quadwords*.

- be equal to the size of the transmitted frame's header.

- not exceed the plug-in's MOH (see Section 2.2).

If any of these constraints are violated the socket's resulting behaviour is undefined.

The behaviour of a plug-in processing a frame whose type it does not support is *unspecified*.

As is the case for the transmission of any outbound frame, header data is contained within the body of the instruction's descriptor. However, unlike an opcode 1 instruction (see Section 2.2.1.2), *zero* is a valid length. If its **Length** field has a *zero* (0) value the transmitted frame contains *only* payload.

The descriptor's header contains a valid *payload reference*. That reference occupies the header's first quadword and contains two 32-bit (*word*) fields whose interpretation is as follows:

- **Payload buffer:** This field contains a *physical* address pointing to a buffer containing the frame's payload. No restrictions are placed on its alignment. The transfer engine assumes the buffer has either previously been flushed or is located in uncached memory. Transfer behaviour is undefined if neither constraint is met. A buffer's *length* is determined by the field below.

- **Payload length:** This field contains the length of the payload whose data are pointed to by the field above. Lengths are expressed in units of *bytes* (8-bits) and range from a value of *zero* (0) to the MOF of the plug-in associated with the socket (see Section 1.3.2). A value of zero is allowed, but will *not* incur a transfer. The behaviour of a transfer which exceeds MOF is undefined, as is the behaviour of a transfer exceeding the processor's physical address space.

The descriptor's header also contains a valid *rendezvous reference*. A rendezvous is described in Chapter 3. A rendezvous reference occupies the header's *second* quadword and contains two 32-bit (*word*) fields. Section 3.1.1 describes these two fields as well as their interpretation.

# 2.3 Inbound interface

As described in Section 2.1 a socket's inbound interface employs its inbound *pending* and *free* list FIFOs. Consequently its corresponding processor interface consists simply of two GPO AXI registers (see Appendix B, "Register Map"). The *read* port of a *pending-list* FIFO is mapped to a *read-only* register while the *write* port of a *free-list* FIFO is mapped to a *write-only* register. Therefore, for each socket the interface provides processor software with two operations: *Removal* from its pending-list and *insertion* onto its work-list. Section 1.4.1 describes the access policy for FIFOs mapped to registers.

For each frame received from a socket's plug-in its corresponding inbound *header* transfer engine allocates a descriptor from the socket's free-list, moves the frame's header to the body of the descriptor and inserts the constructed descriptor onto the engine's pending-list.

Frames are received by removal from the engines's pending-list. Each removed entry corresponds to a single inbound frame. Once removed, the frame's payload must be disposed by the engine and the frame's descriptor returned to the socket's free-list. To dispose a payload the engine can be instructed to either move it or discard it. If moved, its destination in memory is specified as a parameter to the engine.

Payload and descriptor disposal are bound together in a single operation by inserting an *inbound instruction* onto the engine's work-list. That instruction includes not only the descriptor to deallocate but also an opcode specifying the engine's disposal instructions. Table 4 on page 39 enumerates the allowed opcodes while Section 2.5.3 defines the structure of an instruction.

| Opcode | Description and transfer engine action                                                                                                                                                                                                                                                                                                                                                                  | See:            |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0      | The descriptor contains <i>neither</i> payload nor rendezvous information. Conditionally return the descriptor to its socket's free-list.                                                                                                                                                                                                                                                               | Section 2.3.1.1 |

| 1      | The descriptor specifies <i>neither</i> receive buffer nor rendez-<br>vous. The engine discards ( <u>flushes</u> ) the payload of the<br>socket's oldest pending inbound frame. Conditionally,<br>return the descriptor to its socket's free-list.                                                                                                                                                      | Section 2.3.1.2 |

| 2      | The descriptor specifies a receive buffer. The engine<br><u>moves</u> the payload of its oldest pending inbound frame<br>to the specified receive buffer. If that payload is larger<br>than the receive buffer the payload is silently truncated.<br>Conditionally, return the descriptor to its socket's<br>free-list.                                                                                 | Section 2.3.1.3 |

| 3      | <i>Reserved</i> . The descriptor contains <i>neither</i> payload nor ren-<br>dezvous information. Conditionally the engine returns<br>the descriptor to the socket's free-list.                                                                                                                                                                                                                         | N/A             |

| 4      | The descriptor does <i>not</i> specify a receive buffer, but does specify a rendezvous. On completion, insert the rendezvous context onto the rendezvous channel. Conditionally return the descriptor to its socket's free-list.                                                                                                                                                                        | Section 2.3.1.5 |

| 5      | <i>Reserved</i> . The descriptor contains <i>neither</i> payload nor ren-<br>dezvous information. Conditionally return the descrip-<br>tor to its socket's free-list.                                                                                                                                                                                                                                   | N/A             |

| 6      | The descriptor specifies both a receive buffer and rendez-<br>vous. The engine <u>moves</u> the payload of its oldest pend-<br>ing inbound frame to the receive buffer. If the payload is<br>larger than the receive buffer the payload is truncated.<br>On completion, insert the rendezvous context onto the<br>rendezvous channel. Conditionally return the descriptor<br>to its socket's free-list. | Section 2.3.1.4 |

| 7      | <i>Reserved</i> . The descriptor contains <i>neither</i> payload nor ren-<br>dezvous information. Conditionally, return the descrip-<br>tor to its socket's free-list.                                                                                                                                                                                                                                  | N/A             |

TABLE 4

Inbound Opcodes

Figure 12 on page 40 expresses the relationship between instruction and descriptor:

Figure 12 Inbound descriptors and instructions.

This example illustrates the reception of a frame containing *both* header and payload. For this example the length of the frame's header is equal to the plug-in's *Maximum-Inbound-Header* (MIH).

The inbound free-list is initially populated by posting instruction *zero* (0) entries to the socket's inbound *free-list*. Once its free-list is populated frame reception is a straightforward three step process:

- Wait for an inbound frame by removing an entry from a socket's inbound pending-list. The structure of an entry on this list is specified in Section . If the list is not empty the returned value contains a reference to an inbound frame descriptor. It also contains a flag indicating whether or not the frame has a payload. For this example, that flag is assumed *true*.

- Convert the descriptor reference to an address. The descriptor body contains the frame's header. Decode the header to determine where to place the frame's payload. Initialize the descriptor with a reference to a buffer to receive the payload.

- Construct an instruction using the initialized descriptor. Post the instruction to the socket's *payload* transfer engine by inserting the instruction on its inbound free-list (see Section 2.5.4).

Note that although the socket processes only a single inbound instruction at a time and always in the order received this does not imply the processor is necessarily blocked waiting on the transfer engine to complete. Instead, the socket's pending FIFO allows for an asynchronous I/O model in which transfer instructions are *queued* while the engine is busy processing a transaction. The maximum number of outstanding transactions permitted determined by the initial population of the socket's free-list.

# 2.3.1 Transactions

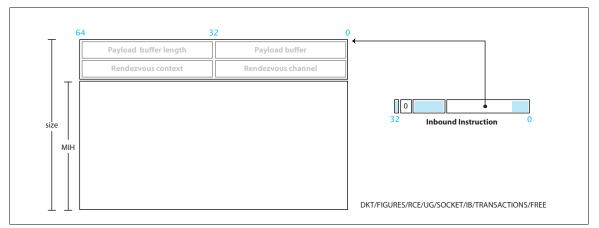

#### 2.3.1.1 Free descriptor

Figure 13 illustrates an instruction which does *not* consume an inbound payload and *conditionally* frees a previously allocated inbound descriptor. The instruction contains a reference to a valid *inbound* descriptor (see Section 2.1.6) and an opcode (see Table 4 on page 39) with a value of *zero* (0). The descriptor reference was acquired from a socket's pending-list as described in Section .

Figure 13 Free inbound descriptor (opcode = 0)

Note that the contents of the descriptor's header and body are ignored by the transfer engine. This instruction serves two purposes:

- To initially populate a socket's inbound free-list after a reset (see Section 2.3).

- To free a received frame which *only* contains a header.

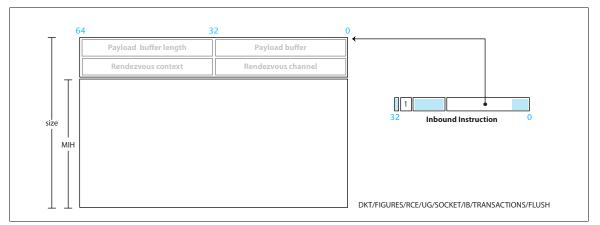

#### 2.3.1.2 Flush frame payload

Figure 14 illustrates an instruction which *discards* an inbound payload and *conditionally* frees a previously allocated inbound descriptor. The instruction contains a reference to a valid *inbound* descriptor (see Section 2.1.6) and an opcode (see Table 4 on page 39) with a value of *one* (1). The descriptor reference was acquired from a socket's pending-list as described in Section .

**Figure 14** Flush inbound frame payload (opcode = 1)

Note that the contents of the descriptor's header and body are ignored by the transfer engine.

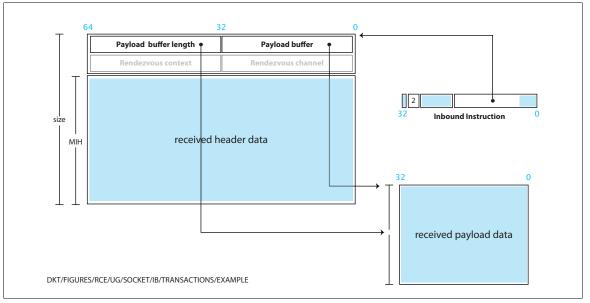

#### 2.3.1.3 Receive frame payload

Figure 15 illustrates an instruction which receives an inbound frame's payload and *conditionally* frees a previously allocated inbound descriptor. The instruction contains a reference to a valid *inbound* descriptor (see Section 2.1.6) and an opcode (see Table 4 on page 39) with a value of *two* (2). The descriptor reference was acquired from a socket's pending-list as described in Section .

Figure 15 Receive inbound frame payload (opcode = 2)

The descriptor's header contains a valid *payload reference*. That reference occupies the header's first quadword and contains two 32-bit (*word*) fields whose interpretation is as follows:

- **Payload buffer:** This field contains a *physical* address pointing to a receive buffer to contain the frame's payload. No restrictions are placed on its alignment. The transfer engine assumes the buffer has either previously been flushed or is located in uncached memory. Transfer behaviour is undefined if neither constraint is met. A buffer's *length* is determined by the field below.

- **Payload length:** This field contains the length of the receive buffer described by the field above. Lengths are expressed in units of *bytes* (8-bits) and range from a value of *zero* (0) to the MIF of the plug-in associated with the socket (see Section 1.3.2). A value of zero is permitted, but will discard the entire payload. If such behaviour is required, see Section 2.3.1.2. The behaviour of a transfer which exceeds MIF is undefined, as is the behaviour of a transfer exceeding the processor's physical address space.

The contents of the rendezvous reference in the descriptor's header are ignored by the transfer engine and need not be initialized to any known value.

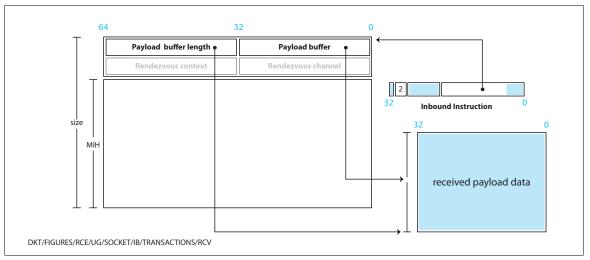

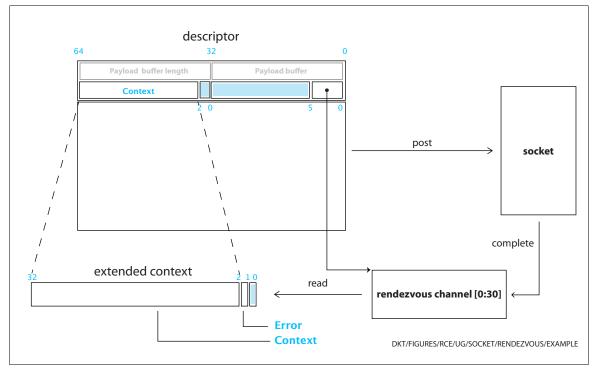

#### 2.3.1.4 Receive payload and rendezvous frame

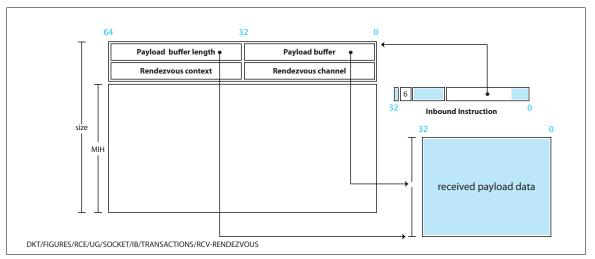

Figure 16 illustrates an instruction which receives an inbound frame's payload and *conditionally* frees a previously allocated inbound descriptor. However, additionally, once transfer is complete the instruction arranges and starts a rendezvous (see Chapter 3). The instruction contains a reference to a valid *inbound* descriptor (see Section 2.1.6) and an opcode (see Table 4 on page 39) with a value of *six* (6). The descriptor reference was acquired from a socket's pending-list as described in Section .

Figure 16 Receive inbound payload and rendezvous frame (opcode = 6)

The descriptor's header contains a valid *payload reference*. That reference occupies the header's first quadword and contains two 32-bit (*word*) fields whose interpretation is as follows:

- **Payload buffer:** This field contains a *physical* address pointing to a receive buffer to contain the frame's payload. No restrictions are placed on its alignment. The transfer engine assumes the buffer has either previously been flushed or is located in uncached memory. Transfer behaviour is undefined if neither constraint is met. A buffer's *length* is determined by the field below.

- **Payload length:** This field contains the length of the receive buffer described by the field above. Lengths are expressed in units of *bytes* (8-bits) and range from a value of *zero* (0) to the MIF of the plug-in associated with the socket (see Section 1.3.2). A value of zero is permitted, but will discard the entire payload. If such behaviour is required, see Section 2.3.1.2. The behaviour of a transfer which exceeds MIF is undefined, as is the behaviour of a transfer exceeding the processor's physical address space.

The descriptor's header also contains a valid *rendezvous reference*. A rendezvous is described in Chapter 3. A rendezvous reference occupies the header's *second* quadword and contains two 32-bit (*word*) fields. Section 3.1.1 describes these two fields as well as their interpretation.

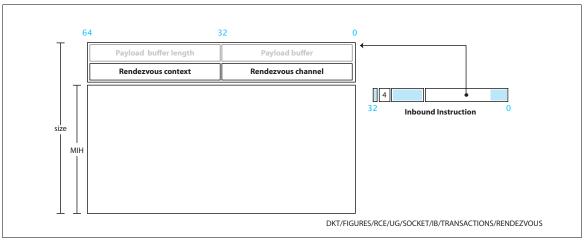

#### 2.3.1.5 Rendezvous frame

Figure 17 illustrates an instruction which arranges and begins a rendezvous (see Chapter 3) and *conditionally* frees a previously allocated inbound descriptor. The instruction contains a reference to a valid *inbound* descriptor (see Section 2.1.6) and an opcode (see Table 4 on page 39) with a value of *four* (4). The descriptor reference was acquired from a socket's pending-list as described in Section .

The contents of the payload reference in the descriptor's header are ignored by the transfer engine and need not be initialized to any known value. However, the descriptor's header does contains a valid *rendezvous reference*. A rendezvous is described in Chapter 3. A rendezvous reference occupies the header's *second* quadword and contains two 32-bit (*word*) fields. Section 3.1.1 describes these two fields as well as their interpretation.

# 2.4 Management

The socket interface provides the capability to *reset* a plug-in as well as conditionally mask *off* its inbound data. Those capabilities are expressed by modelling plug-in behaviour as an abstract *Finite State Machine* with *three* states. Those states are:

- **Online:** This is a plug-in's nominal state. In this state a plug-in receives inbound data and transmits outbound data. The plug-in may *not* be reset from this state.

- **Offline:** This is a plug-in's setup state. In this state a plug-in ignores inbound data, however continues to receive and process outbound frames. While in this state inbound frames *solicited* through an outbound frame may be posted to the socket. A plug-in may be reset *only* from this state. This state is used to resolve two race conditions: First, the race between the *setup* of a plug-in with its *use* and second, the race between a plug-in *reset* and its subsequent use.

- **Disabled:** This is a transitory state. In this state the plug-in ignores *both* inbound and outbound data. A plug-in *is* reset from this state. Note: this is a plug-in's *initial* state. It is brought to this state after POR<sup>1</sup> and connection to its corresponding socket.

The *Plug-in Management* register of a socket's interface is used to manage its corresponding plug-in. The register contains two, single-bit fields. Setting and clearing these fields drives the plug-in through its various states, while reading the register returns the plug-in's current state. Table 5 on page 45 enumerates the correspondence between register fields and state, while the register itself is specified and described in Section 2.4.1.

| Register       | Fields |                     |

|----------------|--------|---------------------|

| Enabled Online |        | Corresponding State |

| False          | False  | Disabled            |

| True           | False  | <u>Offline</u>      |

| False          | True   | N/A                 |

| True           | True   | <u>Online</u>       |

TABLE 5 Plug-in state

Note that a state which has the plug-in <u>online</u>, but *not* enabled is prohibited. As well, only four transitions are allowed between the three states. These transitions are enumerated and described in Section 2.4.1. The socket interface enforces the allowed states and their corresponding transitions. Any transaction which would set register fields to an invalid state is silently rejected with the plug-in remaining in its current state.

<sup>1.</sup> Power-On-Reset

The three canonical operations necessary to successfully manage a plug-in are implemented through a combination of sequencing state and transition. Those operations are described in Section 2.4.2.

# 2.4.1 Transitions

#### 2.4.1.1 Online to offline

The plug-in is in its <u>online</u> state (see Table 5 on page 45). To transit the plug-in to <u>offline</u>:

- *Clear* the **Online** field of a socket's plug-in register. Clearing this field will cause the plug-in to emit an inbound *marker* frame. The format and structure of this frame is plug-in specific.

- Wait for the plug-in's inbound marker frame. This operation is plug-in specific. Once a marker is received the plug-in's inbound pipeline is drained and will not emit further frames until the plug-in is brought <u>online</u>.

- Exit.

#### 2.4.1.2 Offline to online

The plug-in is in its <u>offline</u> state (see Table 5 on page 45). To transit the plug-in to <u>online</u>:

- *Set* the **Online** field of a socket's plug-in register.

- Exit.

#### 2.4.1.3 Offline to disabled

The plug-in is in its <u>offline</u> state (see Table 5 on page 45). To transit the plug-in to <u>disabled</u>:

- *Clear* the **Enabled** field of a socket's plug-in register. Clearing this field *holds* the plug-in within reset, where it ignores inbound data as well as outbound frames.

- Exit.

#### 2.4.1.4 Disabled to offline

The plug-in is in its <u>disabled</u> state (see Table 5 on page 45). To transit the plug-in to <u>offline</u>:

- Set the Enabled field of a socket's plug-in register. Setting this field *removes* the plug-in from being held in reset, triggering its plug-in specific reset logic.

- Exit.

# 2.4.2 Operations

#### 2.4.2.1 Plug-in reset

A plug-in must be <u>offline</u> in order to be reset. To reset:

- Transit the plug-in to <u>disabled</u> (see Section 2.4.1.3).

- Transit back to <u>offline</u> (see Section 2.4.1.4).

- Return the plug-in's reset status (this operation is plug-in specific) and exit.

#### 2.4.2.2 Bringing a plug-in online

The plug-in begins its life <u>disabled</u> with its inbound pipeline drained. To bring the socket and its corresponding plug-in <u>online</u>:

- Transit the plug-in to <u>offline</u> (see Section 2.4.1.4). This transition will *reset* the plug-in.

- Initialize the plug-in's corresponding socket.

- If the plug-in did *not* reset, transit back to <u>disabled</u> (see Section 2.4.1.3) and exit.

- Initialize the plug-in as appropriate (this operation is plug-in specific).

- If the plug-in did *not* initialize, transit back to <u>disabled</u> (see Section 2.4.1.3) and exit.

- Transit the plug-in to <u>online</u> (see Section 2.4.1.2).

- Exit.

#### 2.4.2.3 Reset a plug-in while online

The plug-in begins in its <u>online</u> state. To reset:

- Transit the plug-in to <u>offline</u> (see Section 2.4.1.1).

- Reset the plug-in (see Section 2.4.2.1).

- If the plug-in did *not* reset, exit.

- Reinitialize the plug-in as appropriate (this operation is plug-in specific).

- If the plug-in did *not* initialize, exit.

- Transit the plug-in to <u>online</u> (see Section 2.4.1.2).

- Exit.

# 2.5 Registers

The interface defines *four* (4) sockets. Each socket is accessed through *five* registers located in the processor's GPO AXI space. Appendix B specifies the base address for each of the four sockets. Table 6 on page 48 enumerates the relative address of the five registers with respect to any one of the four bases.

| Offset <sup>1</sup> | Description                    | Access     | See:          |

|---------------------|--------------------------------|------------|---------------|

| 00                  | Outbound Free-List             | Read/Only  | Section 2.5.1 |

| 04                  | Outbound Work-List             | Write/Only | Section 2.5.2 |

| 08                  | Inbound Pending-List Read/Only |            | Section 2.5.3 |

| 12                  | Inbound Work-List Write/Only   |            | Section 2.5.4 |

| 16                  | Reserved                       | N/A        | N/A           |

| 20                  | Reserved                       | N/A        | N/A           |

| 24                  | Reserved                       | N/A        | N/A           |

| 28                  | Plug-in Management             | Read/Write | Section 2.5.5 |

TABLE 6

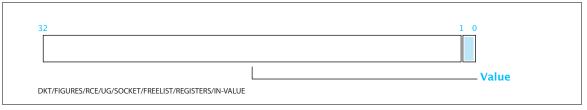

Socket Register Map

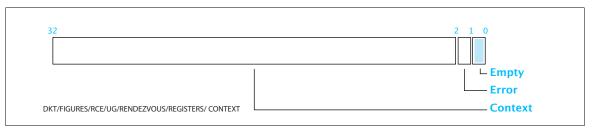

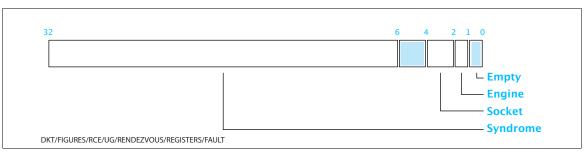

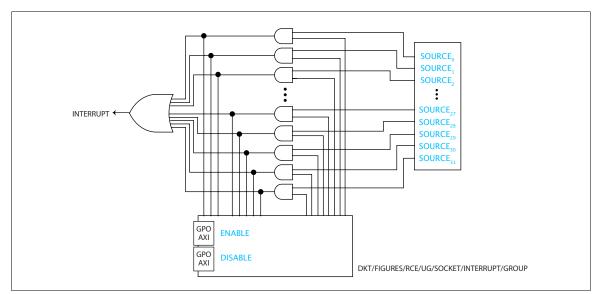

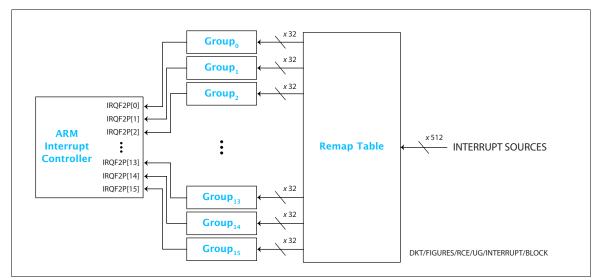

1. In (decimal) *bytes*